74LS193芯片是同步四位二進(jìn)制可逆計(jì)數(shù)器,它具有雙時(shí)鐘輸入,并具有異步清零和異步置數(shù)等功能。

74ls193計(jì)數(shù)器工作原理:

193為可預(yù)置的十進(jìn)制同步加/減計(jì)數(shù)器,共有54193/74193,54LS193/74LS193兩種線路結(jié)構(gòu)形式。其主要電特性的典型值如下:

193的清除端是異步的。當(dāng)清除端(CLEAR)為高電平時(shí),不管時(shí)鐘端(CDOWN、CUP)狀態(tài)如何,即可完成清除功能。

193的預(yù)置是異步的。當(dāng)置入控制端(LOAD)為低電平時(shí),不管時(shí)鐘(CDOWN、CUP)的狀態(tài)如何,輸出端(QA-QD)即可預(yù)置成與數(shù)據(jù)輸入端(A-D)相一致的狀態(tài)。

193的計(jì)數(shù)是同步的,靠CDOWN、CUP同時(shí)加在4個(gè)觸發(fā)器上而實(shí)現(xiàn)。在CDOWN、CUP上升沿作用下QA-QD同時(shí)變化,從而消除了異步計(jì)數(shù)器中出現(xiàn)的計(jì)數(shù)尖峰。當(dāng)進(jìn)行加計(jì)數(shù)或減計(jì)數(shù)時(shí)可分別利用CDOWN或CUP,此時(shí)另一個(gè)時(shí)鐘應(yīng)為高電平。

當(dāng)計(jì)數(shù)上溢出時(shí),進(jìn)位輸出端(CARRY)輸出一個(gè)低電平脈沖,其寬度為CUP低電平部分的低電平脈沖;當(dāng)計(jì)數(shù)下溢出時(shí),錯(cuò)位輸出端(BORROW)輸出一個(gè)低電平脈沖,其寬度為CDOWN低電平部分的低電平脈沖。

當(dāng)把BORROW和CARRY分別連接后一級(jí)的CDOWN、CUP,即可進(jìn)行級(jí)聯(lián)。

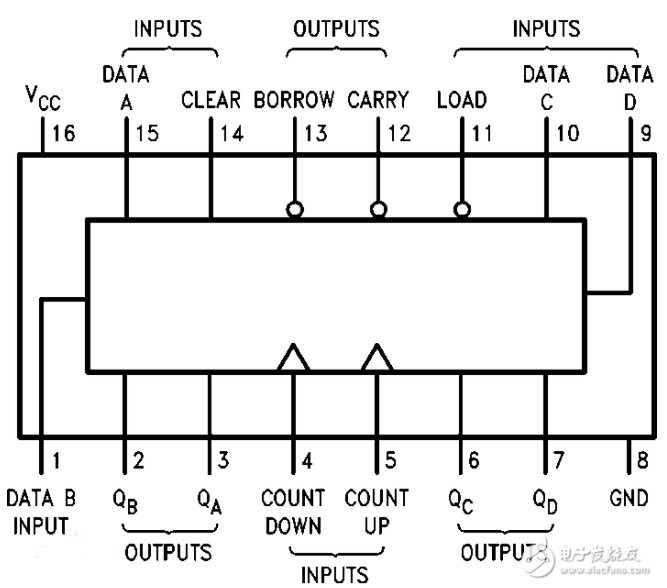

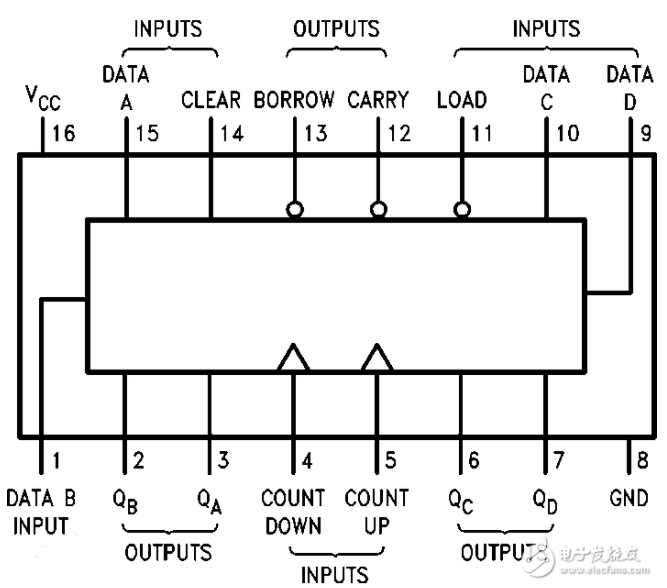

74ls193引腳圖:

74LS193引腳圖

74ls193引腳說(shuō)明:

-

BORROW錯(cuò)位輸出端(低電平有效)

-

CARRY進(jìn)位輸出端(低電平有效)

-

CDOWN減計(jì)數(shù)時(shí)鐘輸入端(上升沿有效)

-

CUP加計(jì)數(shù)時(shí)鐘輸入端(上升沿有效)

-

CLEAR異步清除端

-

A-D并行數(shù)據(jù)輸入端

-

LOAD異步并行置入控制端(低電平有效)

-

QA-QD輸出端

74ls193功能表:

74LS193功能表

-

二進(jìn)制

+關(guān)注

關(guān)注

2文章

803瀏覽量

42129 -

雙時(shí)鐘模式

+關(guān)注

關(guān)注

0文章

2瀏覽量

5798 -

異步清零法

+關(guān)注

關(guān)注

4文章

3瀏覽量

6837

發(fā)布評(píng)論請(qǐng)先 登錄

DLP4710evm lc TRIG_OUT2引腳不輸出脈沖信號(hào)怎么解決?

74HC193-Q100;74HCT193-Q100二進(jìn)制加減計(jì)數(shù)器規(guī)格書(shū)

2引腳VSFN mikroBUS?插座板用戶指南

180引腳ControlCARD集線站信息指南

采用28引腳HTSSOP的SWIFT DC/DC轉(zhuǎn)換器的熱性能

請(qǐng)問(wèn)LMH6410引腳1(SDI)是否是增益控制信號(hào)輸入腳,而引腳4(SDO)又是數(shù)據(jù)輸出,為什么?

STM32引腳中的BOOT1在哪里

求助,關(guān)于INA333引腳鍍金問(wèn)題求解

THS4131 5.6引腳短路的原因?

SN74HC193-Q1 4位同步遞增/遞減計(jì)數(shù)器數(shù)據(jù)表

74ls193引腳圖及功能表

74ls193引腳圖及功能表

評(píng)論