AGM Micro是領(lǐng)先的可編程SoC、通用32位MCU、和異構(gòu)(MCU)邊緣計算芯片和方案提供商,致力于為消費電子、工業(yè)和AIoT中高量市場提供智能化的設(shè)計軟件和芯片系統(tǒng)。AGM針對不同的縱向應(yīng)用市場,并擁有19個知識產(chǎn)權(quán),以及獲得專利的編譯軟件(包括數(shù)據(jù)庫、綜合、布局、布線、時序分析、比特流產(chǎn)生等)及電路。公司的所有芯片產(chǎn)品線均達到接近ASIC的低成本,并兼具靈活性。

以下是AGM FPGA的一份快速入門介紹,限于篇幅,如有不詳盡的地方,歡迎留意或者郵件溝通交流。

3. 設(shè)計流程

從新建工程一步一步操作,直到生成編程文件,燒錄到目標(biāo)器件上。此部分將Supra和Quartus II一起配合使用。

3.1 在Supra中新建工程

打開 Supra,新建工程(File->Project->New Project),設(shè)置工程目錄和工程名稱。具體步驟如下:

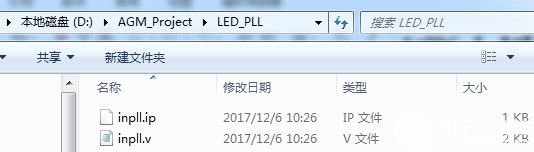

1、 準(zhǔn)備工作:在電腦上先建立一個保存AGM項目工程文件的文件夾。比如在D盤,建立一個AGM_Project\LED_PLL的文件夾。并將使用內(nèi)置晶振的inpll.v和inpll.ip這2個文件放在該文件夾的目錄下。(若不需要使用內(nèi)置的時鐘及PLL,則導(dǎo)入inpll.v和inpll.ip的步驟可以忽略)。

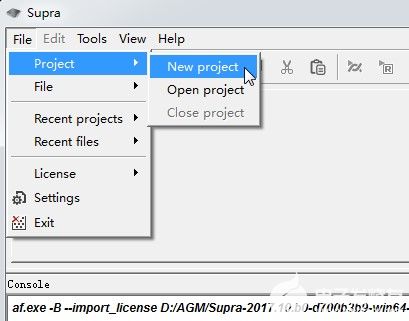

2、 打開Supra軟件新建工程;

圖 3.1 在Supra中新建工程

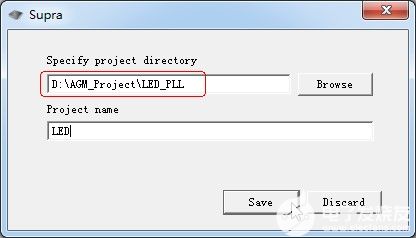

3、 選擇保持路徑及輸入工程名稱;

保存的目錄選擇D:\AGM_Project\LED_PLL,Project name的框內(nèi)輸入工程名稱:LED。然后點擊Save保存工程。

圖 3.2 選擇保存位置及輸入工程名稱

點擊Save后,彈出的對話框點OK。

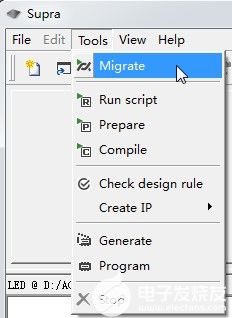

4、 工程轉(zhuǎn)換(Migrate);

選擇菜單: ”Tools -> Migrate” ,或者點擊Migrate按鈕。

圖 3.3 菜單選擇

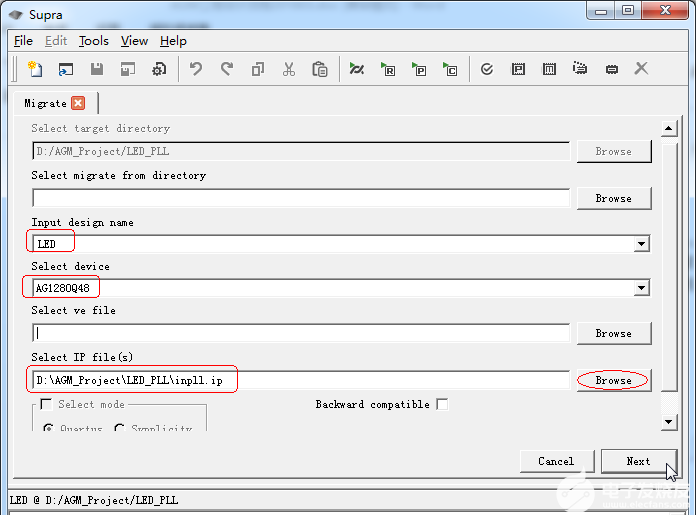

Target Directory:是默認(rèn)選擇當(dāng)前的工程目錄,無法修改;

Select migrate from directory:不填;

Input design name:輸入設(shè)計名稱(例如這里填入:LED);

Select device:從下拉菜單中選擇AG1280Q48;

Select ve file:不填;

Select IP file(s) :點擊Browse,在LED_PLL工程目錄下導(dǎo)入事先保存的inpll.ip;

(注意:1、因為該例程使用了芯片內(nèi)部集成的晶振,所以需要導(dǎo)入此inpll.ip。若是不需要使用晶振,則不需要導(dǎo)入inpll.ip。

2、現(xiàn)在設(shè)的這個PLL的模塊inpll.ip,test1輸出大約37M,test2輸出62MHz,芯片不同略有不同;)

將上述信息設(shè)置完成后,如圖 3.4所示,點擊Next。

圖 3.4 Migrate 窗口設(shè)置

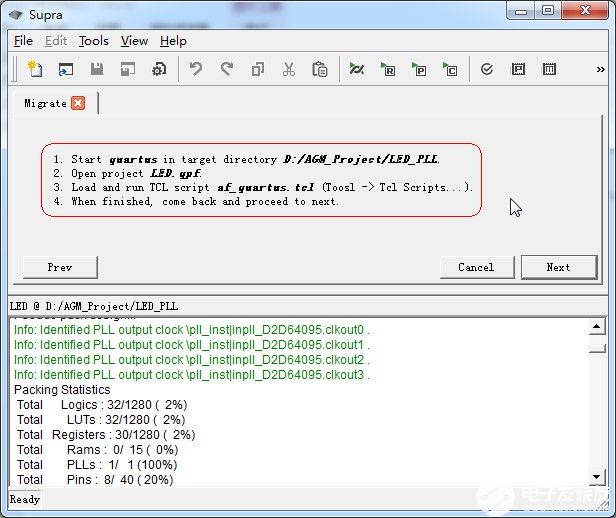

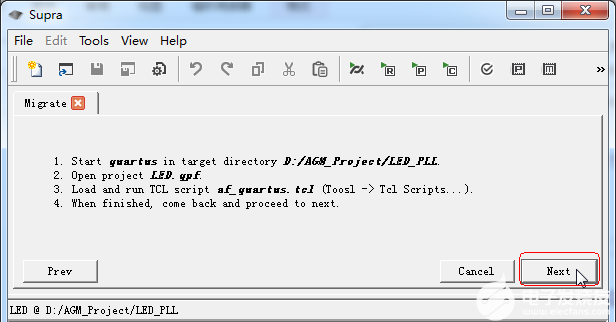

5、點擊 Next后,出現(xiàn)如圖 3.5所示的畫面。軟件會生成一個以 LED 命名的Quartus II格式的Project文件,。下一步操作切換到Quartus II軟件中繼續(xù)進行。

圖 3.5 Migrate設(shè)置完成

3.2 在Quartus II中進行HDL設(shè)計

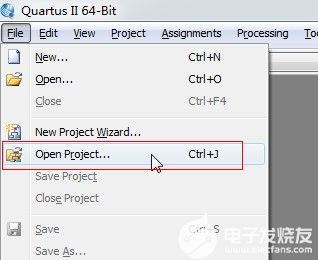

打開Quartus II, 然后選擇Open Project…,打開上一步在Supra中建立的LED Project。

圖 3.6 Quartus II中打開Supra建的工程

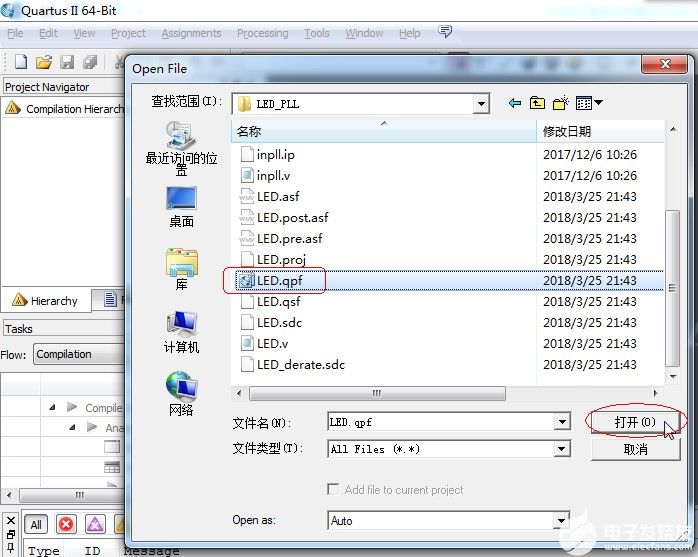

圖 3.7 在Quartus II打開LED.qpf文件

LED的工程已經(jīng)建立好,在Quartus II中,對應(yīng)選擇的器件是EP2C70F896C8,這個不用關(guān)注,只需要在Quartus II中編寫HDL代碼,綜合等。

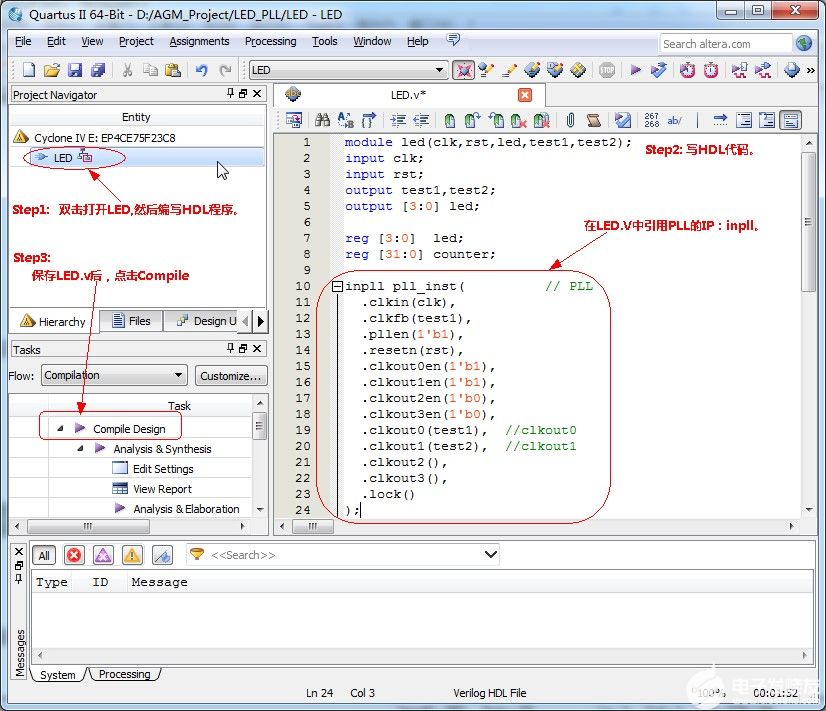

圖 3.8 在Quartus II中編寫HDL代碼

HDL程序編寫完成點保存,然后選擇菜單欄的Processing-àStart Compilation。編譯如果提示有錯誤,就對代碼進行修改,直到?jīng)]有Error提示為止。

圖 3.9 HDL程序編譯

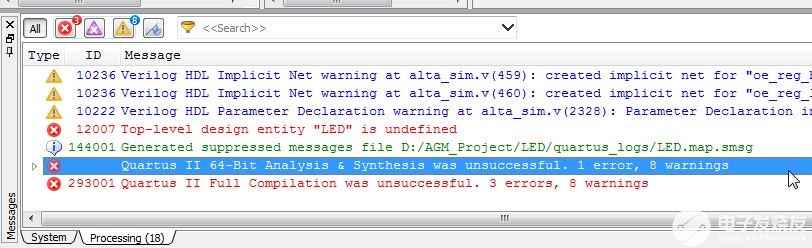

編譯若有錯誤,可以根據(jù)下面的報錯提示,如”LED” is undfined( LED未聲明),故需要修改HDL代碼。

圖 3.10 Qurtus II 錯誤報告

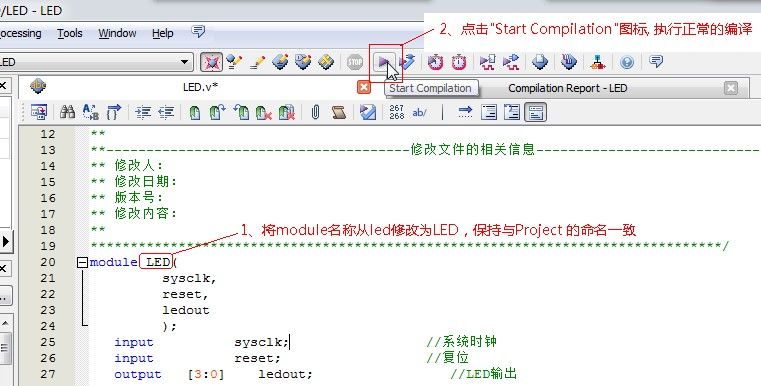

在LED.v的程序代碼中,將module名稱從led修改為LED,然后點擊保存。以后修改原設(shè)計,在Quartus II里只需執(zhí)行正常的編譯(Start Compilation)。

圖 3.11 修改程序后,重新編譯

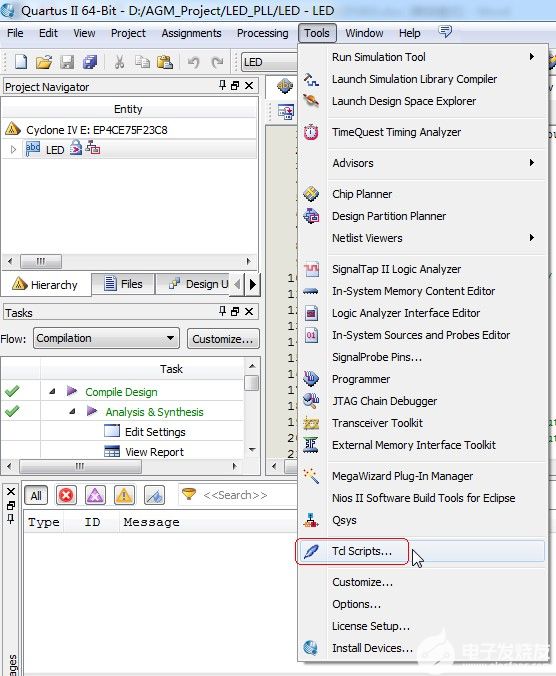

重新再編譯,等編譯通過后, 在Quartus II 中選擇菜單中 Tools -> Tcl Scripts...。

注意:Tcl Scripts...只需要在第一次新建工程的時候需要執(zhí)行,后續(xù)修改HDL代碼,Compile通過后,不需要再執(zhí)行Tcl Scripts...。

圖 3.12 Tcl 操作

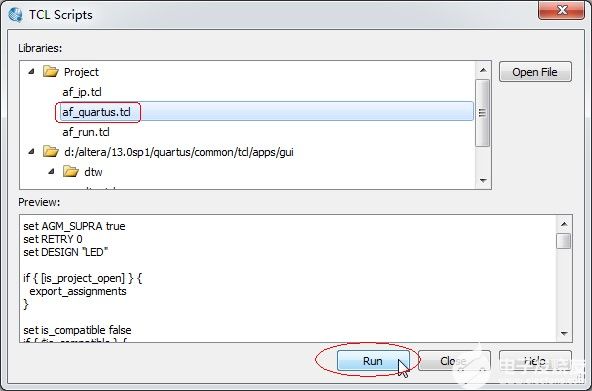

在Tcl Scripts窗口中選 af_quartus.tcl,點擊 Run。

圖 3.13點擊 Run進行編譯

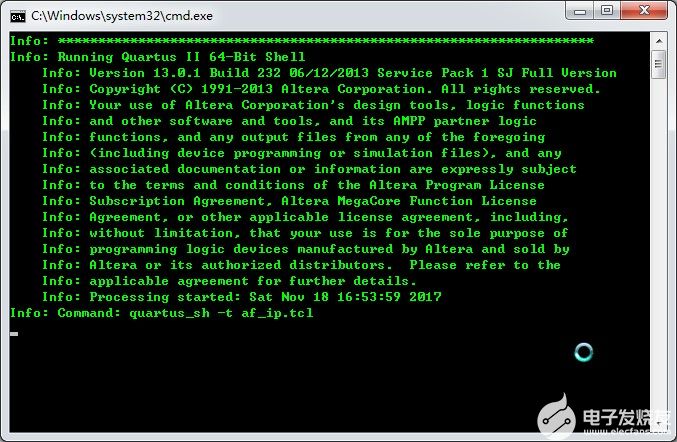

中間會彈出命令窗口,不用理會,后臺會自動處理。

圖 3.14 臨時彈出命令窗口

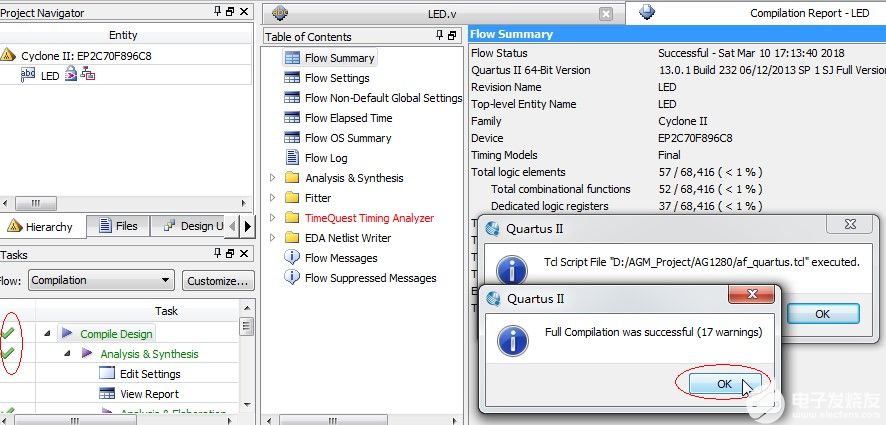

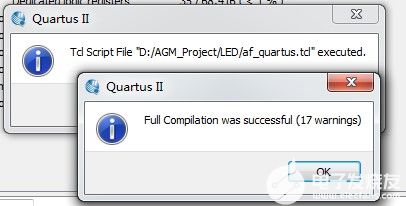

圖 3.15 執(zhí)行TCL操作完成后提示通過OK

如下圖,點擊OK。

圖 3.16 編譯成功

3.4 功能引腳分配

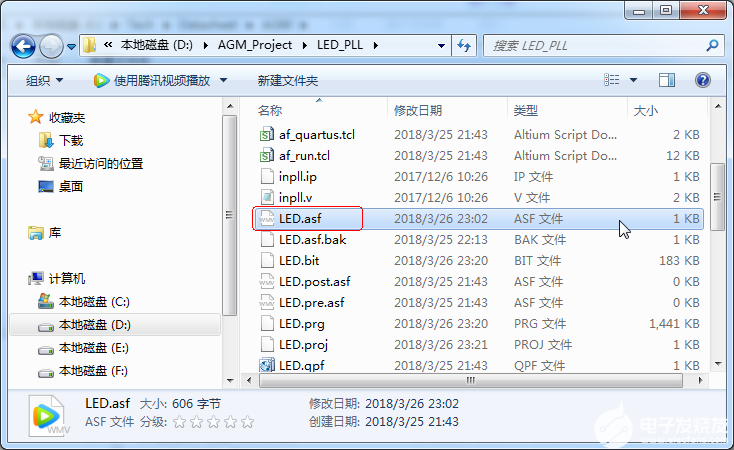

Quartus II 里編譯成功后,在工程目錄D:\AGM_Project\LED_PLL中,找到LED.asf 文件。

圖 3.17 打開工程目錄下的管腳配置文件LED.asf

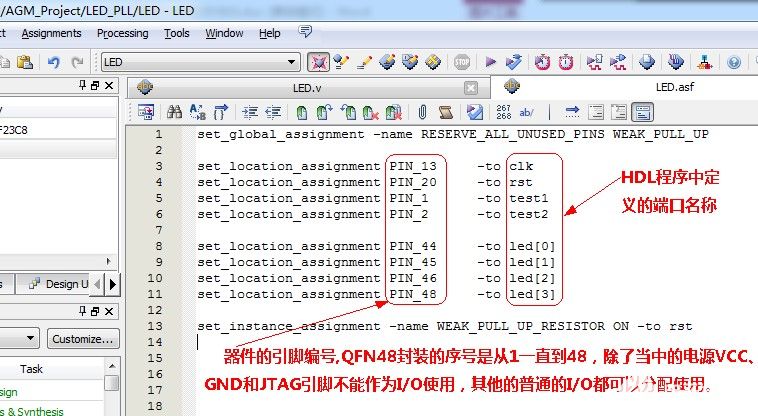

該LED.asf文件可以通過記事本打開,也可以直接拖動到Quartus II中打開。LED.asf文件初始狀態(tài)是一個空文檔,打開后是一片空白,用戶可以直接編輯管腳分配說明,(具體請參考芯片的管腳映射列表,確定 IO 名稱及位置),注意:PLL 的輸入時鐘必須是芯片的全局輸入時鐘管腳(AG1280Q48的是Pin_13,Pin_15,Pin_19 這三個)。LED.asf的管腳指定描述如下。LED.asf文件內(nèi)容如圖 3.18所示,編輯完成后,點擊保存即可。

set_global_assignment -name RESERVE_ALL_UNUSED_PINS WEAK_PULL_UP

set_location_assignment PIN_13 -to clk

set_location_assignment PIN_20 -to rst

set_location_assignment PIN_1 -to test1

set_location_assignment PIN_2 -to test2

set_location_assignment PIN_44 -to led[0]

set_location_assignment PIN_45 -to led[1]

set_location_assignment PIN_46 -to led[2]

set_location_assignment PIN_48 -to led[3]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to rst

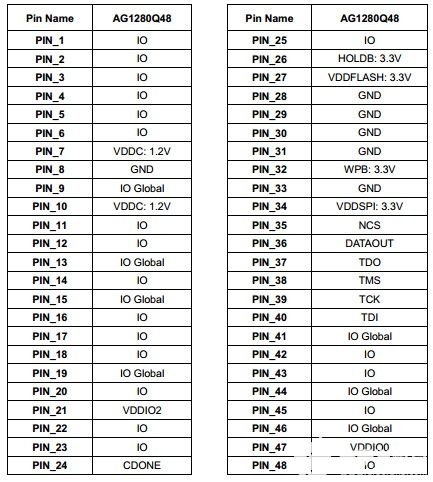

注意:1、器件的引腳序號,QFN48封裝的序號是從1一直到48,除了當(dāng)中的電源VCC、GND和JTAG引腳不能作為使用,其他的普通的I/O都可以分配使用。

2、CLK信號必須要通過名稱為IO Global的全局引腳接入,否則可能導(dǎo)致無法分配引腳。

3、Reset信號也建議從IO Global的全局引腳接入。

圖 3.18 編寫管腳配置文件

補充,AG1280Q48的引腳定義如下:

圖 3.19 AG1280Q48 PINOUT

3.5 在Supra中進行項目編譯

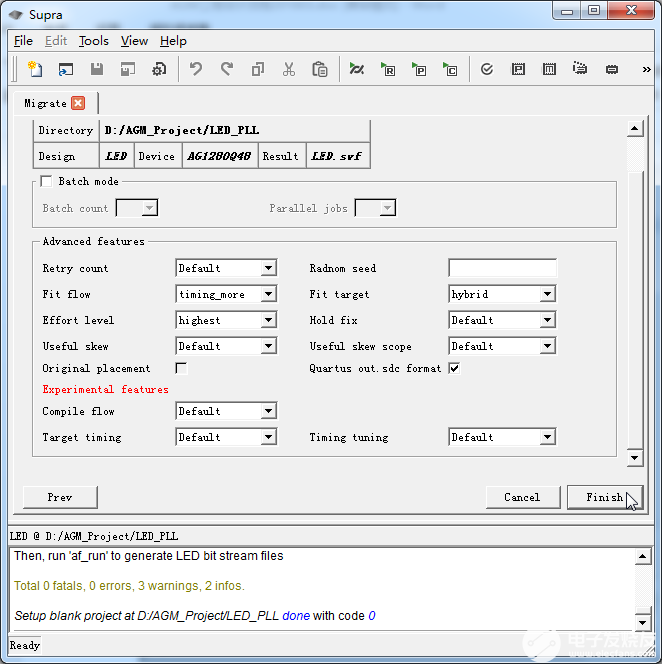

返回Supra 中,點擊Next,開始進行編譯,參數(shù)按照默認(rèn)的。如圖3.20和圖3.21所示。

圖3.20 點擊Next

圖3.21 保持默認(rèn)參數(shù)

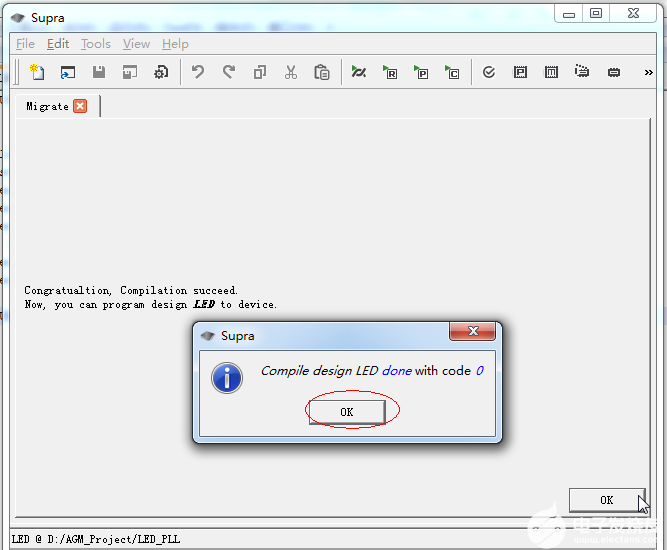

參數(shù)保持默認(rèn)的,然后點擊Finish,軟件后臺將進行布局布線等操作。等待軟件提示成功,如圖3.22所示。

圖3.22 設(shè)計編譯成功

編譯成功后,軟件將自動生成燒寫文件,LED_hybrid.prg。

3.6 芯片燒寫

在Supra 軟件菜單欄中選Tools ---à Program,或者點擊Program圖標(biāo)。選中 DesignName_hybrid.prg,這里我們選擇LED_hybrid.prg,然后點擊Program開始程序燒寫。燒寫成功后,CDONE 管腳會變高。

審核編輯:符乾江

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613945 -

AGM

+關(guān)注

關(guān)注

0文章

86瀏覽量

17397

發(fā)布評論請先 登錄

AGM AG32VH(MCU+FPGA+PSRAM) 系列應(yīng)用指南

國產(chǎn)FPGA往事

AGM FPGA/MCU燒寫文件類型有哪些及用途

【國產(chǎn)FPGA入學(xué)必備】刀劍在鞘,兵器先藏 | 盤古676系列國產(chǎn)FPGA開發(fā)板

【國產(chǎn)FPGA入學(xué)必備】國產(chǎn)FPGA權(quán)威設(shè)計指南+配套FPGA圖像視頻教程

【國產(chǎn)FPGA必備教程】——紫光同創(chuàng)FPGA圖像視頻教程,適用于小眼睛FPGA盤古全系列開發(fā)板

【米爾-紫光MYB-J7A100T國產(chǎn)FPGA開發(fā)板試用】米爾-紫光PG2L100H國產(chǎn)FPGA開發(fā)板開箱評測

FPGA芯片國產(chǎn)替代性價比凸顯,Altera漲價在即,Xilinx繼去年大幅漲價后,12月繼續(xù)大幅調(diào)漲價格,成熟產(chǎn)品尤甚

紫光同創(chuàng)助力國產(chǎn)FPGA高校生態(tài)建設(shè)

【AG32開發(fā)板體驗連載】網(wǎng)絡(luò)攝像頭

AGM官方AG32 MCU開發(fā)板

國產(chǎn)AGM FPGA設(shè)計流程的詳細介紹

國產(chǎn)AGM FPGA設(shè)計流程的詳細介紹

評論