所謂流水線處理,如同生產(chǎn)裝配線一樣,將操作執(zhí)行工作量分成若干個(gè)時(shí)間上均衡的操作段,從流水線的起點(diǎn)連續(xù)地輸入,流水線的各操作段以重疊方式執(zhí)行。這使得操作執(zhí)行速度只與流水線輸入的速度有關(guān),而與處理所需的時(shí)間無關(guān)。這樣,在理想的流水操作狀態(tài)下,其運(yùn)行效率很高。

如果某個(gè)設(shè)計(jì)的處理流程分為若干步驟,而且整個(gè)數(shù)據(jù)處理是單流向的,即沒有反饋或者迭代運(yùn)算,前一個(gè)步驟的輸出是下一個(gè)步驟的輸入,則可以采用流水線設(shè)計(jì)方法來提高系統(tǒng)的工作頻率。

下面用8位全加器作為實(shí)例,分別列舉了非流水線方法、2級(jí)流水線方法和4級(jí)流水線方法。

(1)非流水線實(shí)現(xiàn)方式

module adder_8bits(din_1, clk, cin, dout, din_2, cout);

input [7:0] din_1;

input clk;

input cin;

output [7:0] dout;

input [7:0] din_2;

output cout;

reg [7:0] dout;

reg cout;

always @(posedge clk) begin

{cout,dout} 《= din_1 + din_2 + cin;

end

endmodule

(2)2級(jí)流水線實(shí)現(xiàn)方式:

module adder_4bits_2steps(cin_a, cin_b, cin, clk, cout, sum);

input [7:0] cin_a;

input [7:0] cin_b;

input cin;

input clk;

output cout;

output [7:0] sum;

reg cout;

reg cout_temp;

reg [7:0] sum;

reg [3:0] sum_temp;

always @(posedge clk) begin

{cout_temp,sum_temp} = cin_a[3:0] + cin_b[3:0] + cin;

end

always @(posedge clk) begin

{cout,sum} = {{1‘b0,cin_a[7:4]} + {1’b0,cin_b[7:4]} + cout_temp, sum_temp};

end

endmodule

注意:這里在always塊內(nèi)只能用阻塞賦值方式,否則會(huì)出現(xiàn)邏輯上的錯(cuò)誤!

(3)4級(jí)流水線實(shí)現(xiàn)方式:

module adder_8bits_4steps(cin_a, cin_b, c_in, clk, c_out, sum_out);

input [7:0] cin_a;

input [7:0] cin_b;

input c_in;

input clk;

output c_out;

output [7:0] sum_out;

reg c_out;

reg c_out_t1, c_out_t2, c_out_t3;

reg [7:0] sum_out;

reg [1:0] sum_out_t1;

reg [3:0] sum_out_t2;

reg [5:0] sum_out_t3;

always @(posedge clk) begin

{c_out_t1, sum_out_t1} = {1‘b0, cin_a[1:0]} + {1’b0, cin_b[1:0]} + c_in;

end

always @(posedge clk) begin

{c_out_t2, sum_out_t2} = {{1‘b0, cin_a[3:2]} + {1’b0, cin_b[3:2]} + c_out_t1, sum_out_t1};

end

always @(posedge clk) begin

{c_out_t3, sum_out_t3} = {{1‘b0, cin_a[5:4]} + {1’b0, cin_b[5:4]} + c_out_t2, sum_out_t2};

end

always @(posedge clk) begin

{c_out, sum_out} = {{1‘b0, cin_a[7:6]} + {1’b0, cin_b[7:6]} + c_out_t3, sum_out_t3};

end

endmodule

總結(jié):

利用流水線的設(shè)計(jì)方法,可大大提高系統(tǒng)的工作速度。這種方法可廣泛運(yùn)用于各種設(shè)計(jì),特別是大型的、對(duì)速度要求較高的系統(tǒng)設(shè)計(jì)。雖然采用流水線會(huì)增大資源的使用,但是它可降低寄存器間的傳播延時(shí),保證系統(tǒng)維持高的系統(tǒng)時(shí)鐘速度。在實(shí)際應(yīng)用中,考慮到資源的使用和速度的要求,可以根據(jù)實(shí)際情況來選擇流水線的級(jí)數(shù)以滿足設(shè)計(jì)需要。

這是一種典型的以面積換速度的設(shè)計(jì)方法。這里的“面積”主要是指設(shè)計(jì)所占用的FPGA邏輯資源數(shù)目,即利用所消耗的觸發(fā)器(FF)和查找表(LUT)來衡量。“速度”是指在芯片上穩(wěn)定運(yùn)行時(shí)所能達(dá)到的最高頻率。面積和速度這兩個(gè)指標(biāo)始終貫穿著FPGA的設(shè)計(jì),是設(shè)計(jì)質(zhì)量評(píng)價(jià)的最終標(biāo)準(zhǔn)。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1645文章

22046瀏覽量

618277 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7256瀏覽量

91831 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2039瀏覽量

62138 -

LUT

+關(guān)注

關(guān)注

0文章

50瀏覽量

12848

原文標(biāo)題:FPGA流水線設(shè)計(jì)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

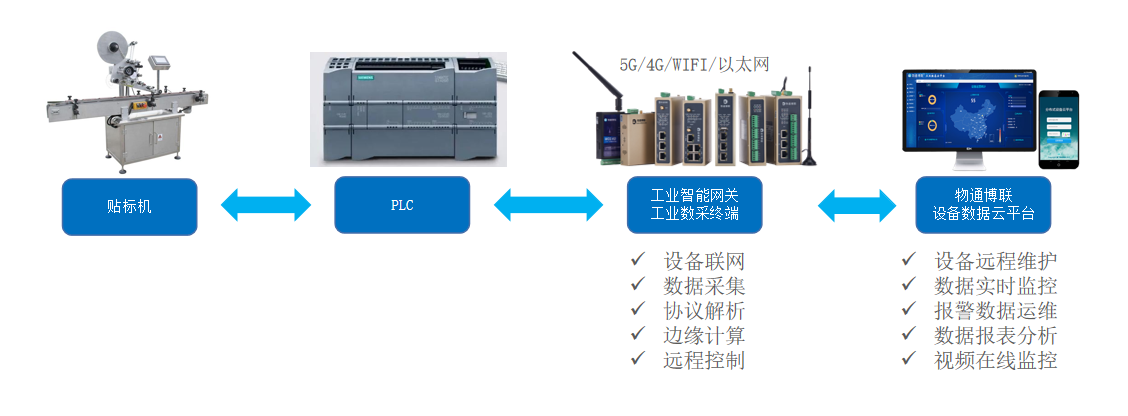

自動(dòng)化開裝封碼流水線數(shù)據(jù)采集解決方案

面包成型流水線數(shù)據(jù)采集遠(yuǎn)程監(jiān)控系統(tǒng)

遠(yuǎn)程io模塊在汽車流水線的應(yīng)用

RISC-V五級(jí)流水線CPU設(shè)計(jì)

工業(yè)讀碼器解決方案在自動(dòng)化流水線上掃描條碼的應(yīng)用

SMT流水線布局優(yōu)化技巧

工業(yè)流水線的智能助手——智能計(jì)數(shù),效率倍增

行云流水線 滿足你對(duì)工作流編排的一切幻想~skr

ADS900高速流水線模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS930高速流水線模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS5421流水線式模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS5413 CMOS流水線模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS5237流水線式模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS828流水線式CMOS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

MT6835磁編碼IC在自動(dòng)鏈板流水線中控制電機(jī)的應(yīng)用

剖析流水線技術(shù)原理和Verilog HDL實(shí)現(xiàn)

剖析流水線技術(shù)原理和Verilog HDL實(shí)現(xiàn)

評(píng)論