1 通信線路誤碼率測試

1.1 測試原理及方法

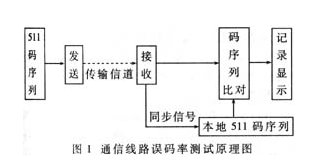

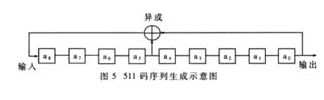

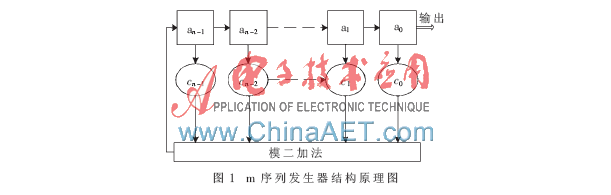

在數(shù)字通信中,誤碼率是檢驗(yàn)數(shù)據(jù)傳輸設(shè)備及其信道工作質(zhì)量的一個主要標(biāo)準(zhǔn)。實(shí)際應(yīng)用中一般都采用本原多項(xiàng)式為1+X5+X9的m序列,其周期為29-1=511,即通常所說的511碼序列。511碼序列實(shí)際上是一個偽隨機(jī)碼序列,利用它進(jìn)行通信線路誤碼率測試的原理如圖1所示。

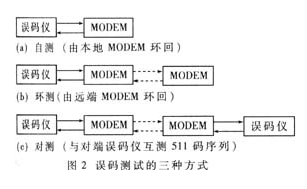

在實(shí)際工作中一般采用誤碼率測試儀(以下稱誤碼儀)來測試通信線路的誤碼率。為解決遠(yuǎn)距離傳輸造成的信號衰減,實(shí)際通信中常用兩臺調(diào)制解調(diào)器(MODEM)將收、發(fā)數(shù)據(jù)終端連接起來,從而實(shí)際應(yīng)用中的誤碼率測試就有自測、環(huán)測和對測三種方式,如圖2所示。

圖中虛線均表示傳輸信道。

1.2 利用誤碼儀測試誤碼率存在的缺陷

當(dāng)需要對某個信道進(jìn)行誤碼率測試時,在通信的兩端要同時將數(shù)據(jù)終端的收發(fā)電纜拔下再連接到誤碼儀上,其弊端是顯而易見的:一是操作不方便,從開始測試到恢復(fù)線路狀態(tài)要對電纜進(jìn)行兩次插拔,既費(fèi)時又費(fèi)事;二是同時對多路信道進(jìn)行誤碼率測試時,必需具備多臺誤碼儀;三是多次插拔電纜會因電纜磨損嚴(yán)重或接觸不良影響設(shè)備工作的可靠性。

2 利用微機(jī)系統(tǒng)實(shí)現(xiàn)誤碼率的測試

2.1 實(shí)現(xiàn)原理

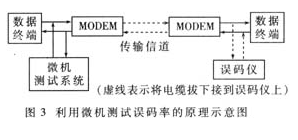

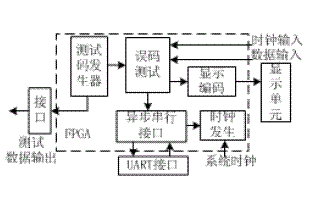

針對上述不利之處,我們設(shè)計(jì)了一種新的誤碼率測試方法應(yīng)用在我單位的數(shù)據(jù)傳輸中心(30路通信信道)。新方法的原理是利用一臺微機(jī),輔以自行開發(fā)的軟、硬件系統(tǒng)替代誤碼儀,對所有信道進(jìn)行集中控制和測試。在測試系統(tǒng)不工作時它僅僅是掛接在通信信道上,對信道中的數(shù)據(jù)傳輸不產(chǎn)生任何影響;當(dāng)要對某一個或幾個信道進(jìn)行誤碼率測試時,在軟件的控制下切斷該信道與數(shù)據(jù)終端的連接,并將其接到測試系統(tǒng),利用微機(jī)與對端的誤碼儀進(jìn)行測試,完畢后由軟件將線路恢復(fù)原狀,如圖3所示。

2.2 硬件設(shè)計(jì)

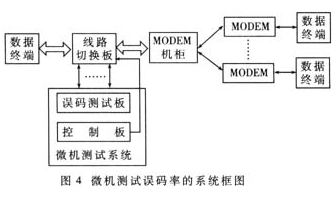

由于數(shù)據(jù)傳輸中心有多達(dá)30路通信信道,為了控制靈活方便,我們設(shè)計(jì)了一塊外置式線路切換板和一塊基于ISA總線的控制板,以實(shí)現(xiàn)從32路全雙工通信信道中分組選擇1~8路進(jìn)行誤碼率測試。分組方式為4個信道作為一組,每組中只能有一個信道被選中測試,最多時可以選中8個信道(一組一個)參加測試。為實(shí)現(xiàn)511碼序列的接收與發(fā)送,又購買了一塊基于ISA總線的誤碼測試板,該板被設(shè)計(jì)成具有8路全雙工通道,支持包括雙同步傳輸方式在內(nèi)的多種通信協(xié)議;且板上具有時鐘控制電路,可以方便地實(shí)現(xiàn)測試碼速率的選擇。但在實(shí)際應(yīng)用中我們將系統(tǒng)設(shè)計(jì)成外時鐘觸發(fā)的方式,即系統(tǒng)收發(fā)511碼序列的速率由MODEM的傳輸速率來確定,最大可支持到14.4Kbits/s的速率。如圖4所示。

2.3 軟件設(shè)計(jì)

2.3.1 應(yīng)用程序介紹

目前使用的微機(jī)測試系統(tǒng)的軟件是用BC++3.1在DOS6平臺下開發(fā)的。由于多路信道的誤碼率測試具有隨機(jī)性,為適應(yīng)這種具有多任務(wù)性質(zhì)的操作,在設(shè)計(jì)過程中模擬了Win32系統(tǒng)的多線程技術(shù),將軟件設(shè)計(jì)成包含一個主線程和多個子線程。主線程負(fù)責(zé)系統(tǒng)的初始化、人機(jī)接口、記錄顯示及子線程的調(diào)度。各子線程獨(dú)立負(fù)責(zé)對某個信道進(jìn)行誤碼率測試,其數(shù)目與被選擇要測試的信道數(shù)目相關(guān)。當(dāng)需要對某個信道測試誤碼率時,主線程執(zhí)行下列操作:

·通過控制板向線路切換板發(fā)送控制信息,將相應(yīng)信道接駁到誤碼測試板中,同時切斷該信道與數(shù)據(jù)終端的連接;

·初始化誤碼測試板上相應(yīng)通道的狀態(tài);

·創(chuàng)建一個子線程啟動511碼的發(fā)送、接收及對比,并開始計(jì)時顯示;

·子線程與主線程通信,實(shí)時地將測試的結(jié)果送主線程顯示、記錄,顯示的內(nèi)容包括信道名稱、測試時間、同步情況、誤碼計(jì)數(shù)和最終結(jié)果誤碼率;

·測試完成時由主線程將相應(yīng)通道復(fù)位,并將線路恢復(fù)到原始狀態(tài)。

2.3.2 511碼序列的產(chǎn)生

產(chǎn)生511碼序列的本原多項(xiàng)式為1+X5+X9,其初始值為任意9位非全“0”的二進(jìn)制數(shù),產(chǎn)生方法如圖5所示。

即位a0與位a5異或后作為下一位輸入值,如此循環(huán)511次,即得到一組511碼序列(一個周期)。

2.3.3 511碼序列的發(fā)送

由于在實(shí)際的誤碼率測試過程中,線路上傳輸?shù)氖前醇榷ùa速率發(fā)送的持續(xù)等間隔511碼位流,即不允許在該位流中插入任何控制字符或比特位。每個比特位的同步依靠與數(shù)據(jù)(TxD、Rxd)一同傳輸?shù)臅r鐘信號(TxC、RxC)來完成。

考慮到一個周期的511碼序列不是整數(shù)字節(jié),為便于微機(jī)的處理,預(yù)先生成8個周期即511個字節(jié)的碼序列,置于一個專門的發(fā)送緩沖區(qū)內(nèi)。根據(jù)511碼產(chǎn)生原理可知,在一個8周期的碼序列中,任選一個相鄰的16位碼組,該碼組必是唯一的。由此,可從511字節(jié)的碼序列中任意選定一個16位碼組作為同步字符,并將誤碼測試板的通信協(xié)議設(shè)置成所支持的雙同步(16位同步字符)傳輸方式。511碼的發(fā)送主要依靠硬件來完成,軟件僅在初始化時設(shè)定發(fā)送緩沖區(qū)的地址、要發(fā)送的字節(jié)數(shù),然后啟動加載發(fā)送;待第一個511字節(jié)的位流發(fā)送完畢后,由硬件自動加載持續(xù)發(fā)送,直到停止測試為止,從而實(shí)現(xiàn)511碼序列的持續(xù)不間斷發(fā)送。

2.3.4 511碼的接收與比對

在設(shè)定好雙同步工作方式后,利用2.3.3節(jié)中的16位同步字符對接收的位流進(jìn)行同步。每同步一次即接收511字節(jié)的位流,然后與預(yù)先生成的511字節(jié)碼序列對比,并計(jì)算出誤碼數(shù)。為了處理上的方便,對每個被測試接收信道設(shè)置兩個接收緩沖區(qū),長度各為511字節(jié),交替接收處理。由于在同步后接收到的511字節(jié)位流是由硬件實(shí)現(xiàn)直接打入到相應(yīng)的接收緩沖區(qū)中(DMA接收),非常高效,故設(shè)置兩個接收緩沖區(qū)所增加的系統(tǒng)開銷相對而言是微不足道的。

2.4 應(yīng)用效果

利用新的微機(jī)測試系統(tǒng),我們在一個信道和多個信道的情況下,分別進(jìn)行了自測、環(huán)測及與誤碼儀的對測,并在測試過程中人工加入干擾,以判斷系統(tǒng)的適應(yīng)性。測試結(jié)果表明,采用新的誤碼率測試方法是完全可靠和可行的。

與用誤碼儀進(jìn)行通信線路誤碼率測試的方法相比,本文中所述的方法有如下幾點(diǎn)優(yōu)越性:

·控制靈活方便,不再需要插拔電纜,簡化了操作;

·從32路通道中分組選擇1~8路進(jìn)行測試的功能既降低了硬件設(shè)計(jì)的復(fù)雜性,又可以適應(yīng)不同情況下的需要。選擇足夠通道的誤碼測試板,即可在通信的兩端實(shí)現(xiàn)高效率的誤碼率測試;

·測試誤碼率時,被測信道不會影響其它信道的正常工作。系統(tǒng)不工作時對所有信道的數(shù)據(jù)傳輸不會造成任何影響,可靠性高。

為更好地適應(yīng)多路誤碼率測試的需求,可充分地利用WindowsNT和VC++的多線程技術(shù),將該微機(jī)測試系統(tǒng)設(shè)計(jì)成在WindowsNT 4(工作站版)下運(yùn)行,這樣既可提高測試系統(tǒng)的性能,又便于軟件的維護(hù)。

責(zé)任編輯:gt

-

調(diào)制解調(diào)器

+關(guān)注

關(guān)注

3文章

872瀏覽量

39429 -

電纜

+關(guān)注

關(guān)注

18文章

2855瀏覽量

55854 -

總線

+關(guān)注

關(guān)注

10文章

2947瀏覽量

89332

發(fā)布評論請先 登錄

是德科技全新多通道比特誤碼率測試儀

誤碼率測試儀的技術(shù)原理和應(yīng)用場景

供應(yīng)維修 誤碼率測試儀 Keysight N4960A

求一種基于FPGA的誤碼率測試儀的方案

Keysight M8030A 長期回收 比特誤碼率測試儀

基于FPGA的誤碼率測試儀的設(shè)計(jì)與實(shí)現(xiàn)

基于DS2172的誤碼測試儀的設(shè)計(jì)

基于Cyclone系列FPGA器件和UART功能實(shí)現(xiàn)誤碼率測試儀器的設(shè)計(jì)

關(guān)于FPGA的誤碼測試儀研究與設(shè)計(jì)

如何在DS2652x STC上使用誤碼率測試儀

是德M8020A比特誤碼率測試儀集成可調(diào)節(jié)碼間干擾功能

是德高性能比特誤碼率測試儀M8020A介紹

誤碼率測試儀,讓工程師從容應(yīng)對高速數(shù)字信號設(shè)計(jì)

內(nèi)置誤碼率測試儀(BERT)和采樣示波器一體化測試儀器安立MP2110A

基于微機(jī)系統(tǒng)實(shí)現(xiàn)誤碼率測試儀的測試方案

基于微機(jī)系統(tǒng)實(shí)現(xiàn)誤碼率測試儀的測試方案

評論