作者:蘇耀峰,王德剛,魏急波

1 引言

軟件無線電(SDR)技術近年來發(fā)展迅速,在無線通信中的數(shù)字接收機領域應用尤為廣泛。FPGA(現(xiàn)場可編程門陣列)以其高集成度、高可靠性和靈活性,在軟件無線電平臺的設計中發(fā)揮著重要的核心作用。同時,SDR中的數(shù)據(jù)接口設計也是關鍵的環(huán)節(jié)。以太網(wǎng)是目前最通用的數(shù)據(jù)接口之一,但是中低端FPGA通常不具備以太網(wǎng)接口,這為FPGA在SDR中的應用造成了不便。如果為FPGA配置以太網(wǎng)接口,與外部網(wǎng)絡實現(xiàn)通信,將有利于SDR平臺的功能延伸,方便數(shù)據(jù)傳輸和與現(xiàn)有系統(tǒng)接口。

DM9000A是Davicom公司生產(chǎn)的一款功能強大的以太網(wǎng)控制器,支持10/100 M以太網(wǎng)速率,可與嵌入式微處理器(MPU)、單片機等以多種方式(如ISA總線等)接口,具有體積小、功耗低、配置靈活、使用簡單等特點。但在傳統(tǒng)應用中,很少有將DM9000A和FPGA直接結合應用的實例,為解決FPGA的以太網(wǎng)接口問題,通常的解決方案是采用單片機或者MPU在FPGA和以太網(wǎng)控制器之間進行數(shù)據(jù)轉發(fā),但弊端是成本提高和功耗增加。

本文在自行設計開發(fā)的OQPSK全數(shù)字接收機中,為實現(xiàn)高速解調(diào)數(shù)據(jù)的實時遠程傳輸處理及接收機參數(shù)的遠程配置,提出了采用FPGA直接控制DM9000A進行以太網(wǎng)數(shù)據(jù)收發(fā)的設計思路。采用Xilinx系列XC2V1000 FPGA和DM9000A,實現(xiàn)低成本、低功耗和高速率的SDR平臺的網(wǎng)絡傳輸功能,其最高傳輸速率可達100 Mb/s。

2 DM9000A工作原理

2.1 主要特性和總體結構

DM9000A的主要特性如下:

支持8/16位數(shù)據(jù)總線;

適用于10Base-T和100Base-T;

10/100 M自適應,適應不同的網(wǎng)絡速率要求;

內(nèi)置16 KB的SRAM,用于收發(fā)緩沖,降低對主處理器的速度要求;

與IEEE 802.3u兼容,支持IEEE802.3x全雙工,可同時收發(fā);

具有睡眠模式,可降低功耗;

采用48引腳LQFP封裝,縮小PCB面積。

DM9000A功能結構框圖如圖1所示,DM9000A實現(xiàn)以太網(wǎng)媒體介質(zhì)訪問層(MAC)和物理層(PHY)的功能,包括MAC數(shù)據(jù)幀的組裝/拆分與收發(fā)、地址識別、CRC編碼/校驗、MLT-3編碼器、接收噪聲抑制、輸出脈沖成形、超時重傳、鏈路完整性測試、信號極性檢測與糾正等。

2.2 工作原理

DM9000A可與微處理器以8 bit或16 bit的總線方式連接,并可根據(jù)需要以單工或全雙工等模式運行。在系統(tǒng)上電時,處理器通過總線配置DM9000A內(nèi)部網(wǎng)絡控制寄存器(NCR)、中斷寄存器(ISR)等,完成DM9000A的初始化。隨后,DM9000A進入數(shù)據(jù)收發(fā)等待狀態(tài)。

當處理器要向以太網(wǎng)發(fā)送數(shù)據(jù)幀時,先將數(shù)據(jù)打包成UDP或IP數(shù)據(jù)包,并通過8 bit或16 bit總線逐字節(jié)發(fā)送到DM9000A的數(shù)據(jù)發(fā)送緩存中,然后將數(shù)據(jù)長度等信息填充到DM9000A的相應寄存器內(nèi),隨后發(fā)送使能命令。DM9000A將緩存的數(shù)據(jù)和數(shù)據(jù)幀信息進行MAC組幀,并發(fā)送出去。

當DM9000A接收到外部網(wǎng)絡送來的以太網(wǎng)數(shù)據(jù)時,首先檢測數(shù)據(jù)幀的合法性,如果幀頭標志有誤或存在CRC校驗錯誤,則將該幀數(shù)據(jù)丟棄。否則將數(shù)據(jù)幀緩存到內(nèi)部RAM,并通過中斷標志位通知處理器,處理器收到中斷后對DM9000A接收RAM的數(shù)據(jù)進行處理。

DM9000A自動檢測網(wǎng)絡連接情況,根據(jù)網(wǎng)速設置內(nèi)部的數(shù)據(jù)收發(fā)速率為10 Mb/s或100 Mb/s。同時,DM9000A還能根據(jù)RJ45接口連接方式改變數(shù)據(jù)收發(fā)引腳的方向,因此無論外部網(wǎng)線是采用對等還是交叉方式,系統(tǒng)均能正常通信。

3 SDR接收機網(wǎng)絡接口設計

在SDR接收機中,中頻模擬信號經(jīng)過A/D轉換、數(shù)字下變頻、抽取濾波等解調(diào)處理后,形成連續(xù)的解調(diào)數(shù)據(jù)流,其速率為10 Mb/s。在FPGA內(nèi)部,解調(diào)輸出的數(shù)據(jù)流和以太網(wǎng)接口部分通過FIFO進行緩沖,當解調(diào)數(shù)據(jù)達到規(guī)定的數(shù)據(jù)幀長度時,F(xiàn)PGA啟動以太網(wǎng)發(fā)送程序,將解調(diào)數(shù)據(jù)發(fā)送到DM9000A,完成數(shù)據(jù)發(fā)送過程。在接收方向,網(wǎng)絡工作站把控制指令按照一定的幀格式組幀發(fā)送到以太網(wǎng),DM9000A接收到發(fā)給自身的以太網(wǎng)幀并通知FPGA啟動以太網(wǎng)接收程序。FPGA將相應的數(shù)據(jù)從DM9000A的接收FIFO讀至FPGA內(nèi)部RAM中,利用數(shù)據(jù)中的控制命令配置接收機參數(shù),完成網(wǎng)絡對SDR接收機的遠程控制。

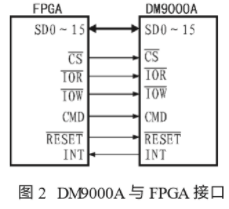

3.1 與FPGA的數(shù)據(jù)接口和控制接口

DM9000A的外部總線符合ISA標準。可通過ISA總線直接與FPGA無縫連接。其硬件連接原理如圖2所示。

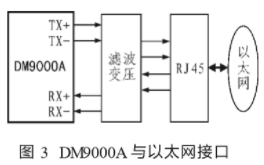

DM9000A內(nèi)部集成了PHY功能,因此與以太網(wǎng)接口可以無縫連接。如圖3所示。

3.2 DM9000A的FPGA控制

3.2.1 初始化模塊

DM9000A正常工作需要在上電后對內(nèi)部寄存器進行初始化。該過程是通過FPGA對DM9000A外部控制總線和數(shù)據(jù)總線的讀寫操作完成的。具體流程如下:

1) 激活PHY

設置GPR(REG_1F) CEPI00 bit[0]=0;

由于復位后,DM9000A恢復默認的休眠狀態(tài)以降低功耗,因此需要首先喚醒PHY。

2) 進行兩次軟復位,步驟如下:

設置NCR(REG_00)bit[2:0]=011;至少保持20μs;

清除NCR(REG_00)bit[2:0]=000;

設置NCR(REQ_00)bit[2:0]=011;至少保持20μs;

清除NCR(REG_00)bit[2:0]=000;

3) 配置NCR寄存器

設置NCR(REG_00)bit[2:1]=00;配置為正常模式。

通過改變該寄存器可以選擇設置內(nèi)部或者外部PHY、全雙工或者半雙工模式、使能喚醒事件等網(wǎng)絡操作。

4) 清除發(fā)送狀態(tài)

設置NSR(REG_01)bit[5]=1 bit[3]=l bit[2]=l;

5) 設置IMR寄存器(REG_FF)PAR bit[7]=l;啟用RX/TX FIFO SRAM讀/寫地址指針自動返回功能。

6) 通過IMR寄存器(REG_FF)PRM bit[0]/PTM bit[1],對RX/TX中斷使能。如果需要在一個數(shù)據(jù)幀發(fā)送完后產(chǎn)生一個中斷,應將PTM bit[1]置為1,如果需要在接收到一幀新數(shù)據(jù)時產(chǎn)生一個中斷,應將PRM bit[1]置為1;

7) 設置RCR寄存器,使能數(shù)據(jù)接收功能。

以上步驟完成后.可以通過LED指示燈觀測DM9000A是否已成功完成初始化。

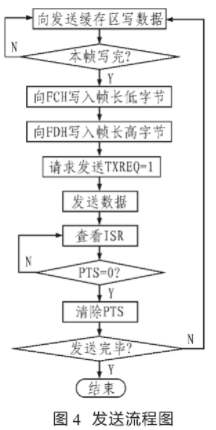

3.2.2 數(shù)據(jù)發(fā)送模塊

DM9000A的發(fā)送緩沖區(qū)可同時存儲兩幀數(shù)據(jù),按照先后順序命名為幀I和幀II,DM9000A上電初始化后,發(fā)送緩存區(qū)的起始地址是00H,當前數(shù)據(jù)幀編號為幀I。兩幀數(shù)據(jù)的狀態(tài)控制字分別記錄在DM9000A的狀態(tài)寄存器03H和04H中。發(fā)送過程如下:

首先,F(xiàn)PGA利用寫操作寄存器MWCMD(REG_F8)向DM9000A的發(fā)送緩存區(qū)中寫入發(fā)送數(shù)據(jù)幀,寫數(shù)據(jù)幀時需要先寫入6字節(jié)的目的MAC地址,再寫入6字節(jié)的源MAC地址,最后寫入發(fā)送數(shù)據(jù)。

隨后,F(xiàn)PGA利用寫操作寄存器MWCMD(REG_F8)將數(shù)據(jù)幀長度寫入寄存器FCH和FDH,數(shù)據(jù)長度為16位,將高8位寫入寄存器FCH,低8位寫入寄存器FDH。

最后,F(xiàn)PGA將發(fā)送控制寄存器TCR(REG_02)的bit[1]置為高電平,向DM9000A發(fā)出發(fā)送數(shù)據(jù)指令。DM9000A自動進行一些處理才將數(shù)據(jù)發(fā)送至以太網(wǎng),包括:插入報頭和幀起始分隔符;插入來自上層協(xié)議的數(shù)據(jù),如果數(shù)據(jù)量小于64字節(jié),則自動補齊64字節(jié);根據(jù)目標地址、源地址、長度/類型和數(shù)據(jù)產(chǎn)生CRC校驗序列,并插入校驗序列位。這些處理都無需FPGA干預。處理完畢后,DM9000A即開始發(fā)送幀I。在幀I發(fā)送的同時,幀II的數(shù)據(jù)即可寫入發(fā)送緩存區(qū)。在幀I發(fā)送完后,將幀II的數(shù)據(jù)長度寫入寄存器FCH和FDH,最后將發(fā)送控制寄存器NSR(REG_01)的bit[1]置為高電平,即可開始幀II的發(fā)送。依此類推,下面發(fā)送的幀將會繼續(xù)編號為幀I,幀II,幀I,幀II……按照同樣的方式發(fā)送。

如果FPGA將中斷屏蔽寄存器IMR(REG_FF)的bit[1]置為高電平,那么發(fā)送完畢后,DM9000A將會產(chǎn)生一個指示發(fā)送完成的中斷信號。在發(fā)送過程中,F(xiàn)PGA可以查詢寄存器標志位寄存器NSR(REG_01)中的TX1END bit[2]或者TX2END bit[3]得到數(shù)據(jù)幀的發(fā)送狀態(tài)。

發(fā)送流程如圖4所示。寄存器ISR中的PTS標志位是發(fā)送中斷標志位,當一幀數(shù)據(jù)發(fā)送完畢,PTS=0,F(xiàn)PGA檢測到該標志后,應清除標志位以便發(fā)送新的數(shù)據(jù)幀。這里需要注意的是,向FC、FD所寫的幀長度應該是包含目的MAC地址段、源MAC地址段和有效數(shù)據(jù)的總長度。

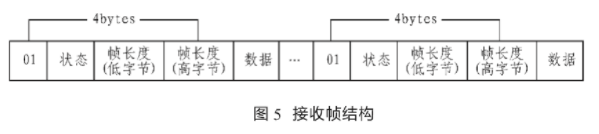

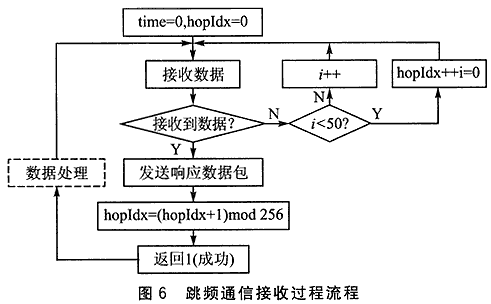

3.2.3 接收模塊

DM9000A中的接收緩存區(qū)是一個環(huán)形結構,初始化后的起始地址為0C00H,每幀數(shù)據(jù)都有4字節(jié)長的首部,然后是有效數(shù)據(jù)和CRC校驗序列。首部4字節(jié)依次是01H、狀態(tài)、長度低字節(jié)和長度高字節(jié),幀結構如圖5所示。

首部4字節(jié)含義如下:

第一個字節(jié)用于檢測接收緩存區(qū)中是否有數(shù)據(jù)。如果這個字節(jié)是01 H,表明接收到了數(shù)據(jù);如果為00H,則說明沒有數(shù)據(jù)。但是如果第一個字節(jié)既不是01H,也不是00H,DM9000A就必須作一次軟復位來從這種異常狀態(tài)中恢復。

第二個字節(jié)存儲以太網(wǎng)幀狀態(tài),由此可判斷所接收幀是否正確。

第三和第四字節(jié)存儲以太網(wǎng)幀長度。后續(xù)的字節(jié)就是有效數(shù)據(jù)。

接收過程如下:

查看中斷狀態(tài)寄存器。如果接收到新數(shù)據(jù),寄存器ISR的PRS位將被置為0;

如果檢測到PRS=0,清除PRS,F(xiàn)PGA開始讀取接收緩存區(qū)數(shù)據(jù)。如果第一個字節(jié)是01H,則說明有數(shù)據(jù);如果是00H,則說明無數(shù)據(jù),需要進行復位;

根據(jù)獲取的長度信息,判斷是否讀完一幀。如果讀完,接著讀下一幀,直到遇到首字節(jié)是00H的幀,說明接收數(shù)據(jù)已讀完。FPGA可以重新查看中斷狀態(tài)寄存器,等待新的有效數(shù)據(jù)幀。接收流程如圖6所示。

4 結束語

本文對以太網(wǎng)控制器DM9000A的原理和功能進行介紹,并結合自行開發(fā)的SDR接收機平臺。基于FPGA設計實現(xiàn)了100 M以太網(wǎng)接口。其設計思路新穎,硬件連接簡單。整體系統(tǒng)具有功耗低、體積小、運行穩(wěn)定可靠等優(yōu)點。SDR平臺的開發(fā)融入網(wǎng)絡設計理念,在應用中有廣泛的前景,大大拓寬了SDR的功能。擴展了SDR的應用領域。

責任編輯:gt

-

FPGA

+關注

關注

1643文章

21952瀏覽量

613833 -

微處理器

+關注

關注

11文章

2369瀏覽量

83816 -

無線電

+關注

關注

60文章

2161瀏覽量

117602

發(fā)布評論請先 登錄

DM9000A,DM9000C網(wǎng)絡接口電路圖

FPGA控制DM9000A進行以太網(wǎng)數(shù)據(jù)收發(fā)的Verilog實現(xiàn)

采用DM9000A實現(xiàn)DSP以太網(wǎng)接口設計

如何利用ARM11驅動DM9000A實現(xiàn)以太網(wǎng)通信?

怎么用XC2V1000型FPGA實現(xiàn)FIR抽取濾波器的設計

dm9000/dm9000a linux驅動程序 (Ethe

伺服控制系統(tǒng)的DM9000A以太網(wǎng)接口設計

DM9000A原理及其與基帶信號處理平臺的結合應用

全數(shù)字跟蹤接收機的設計與實現(xiàn)

基于XC2V1000 FPGA和DM9000A實現(xiàn)OQPSK全數(shù)字接收機的設計

基于XC2V1000 FPGA和DM9000A實現(xiàn)OQPSK全數(shù)字接收機的設計

評論