將模擬信號從“現(xiàn)實”世界轉(zhuǎn)換為可以在上游處理的數(shù)字信號是電子系統(tǒng)的一項基本功能,范圍覆蓋從錄音到物聯(lián)網(wǎng) (IoT)、工業(yè)物聯(lián)網(wǎng) (IIoT),以及現(xiàn)在的智能物聯(lián)網(wǎng) (AIoT)。但是,為了有效地使用和執(zhí)行,需要我們對其基本原理和操作步驟有一定程度的理解,而這往往又被人們忽視。

舉例來說,假設(shè)施加到模數(shù)轉(zhuǎn)換器 (ADC) 輸入上的典型模擬信號的幅度不斷變化,那么在轉(zhuǎn)換前信號究竟是如何先“保持”再“采樣”的呢?信號轉(zhuǎn)換結(jié)束時與一開始會有不同嗎?這種幅度變化或偏差會導(dǎo)致嚴(yán)重的誤差,特別對于需要花費更多時間進(jìn)行信號轉(zhuǎn)換的高分辨率ADC來說,更是如此。設(shè)計人員面臨的挑戰(zhàn)是,既要了解又要消除這種誤差源。

本文介紹了如何使用ADC的采樣和保持 (S&H) 或跟蹤和保持 (T&H) 電路來防止幅度偏差。S&H(或T&H)電路會執(zhí)行真實輸入采樣,工作區(qū)間位于輸入抗混疊低通濾波器和ADC之間。本文討論了S&H IC的特性和選擇標(biāo)準(zhǔn),并介紹了帶有集成S&H的ADC。為了方便描述,我們使用了Texas Instruments、Maxim Integrated和Analog Devices提供的、具有針對不同應(yīng)用的不同特性的樣件。

采樣和保持電路在ADC中的作用

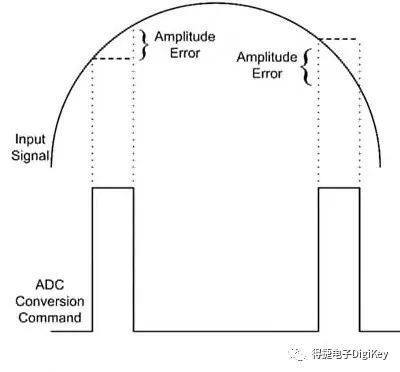

當(dāng)將非直流信號施加到ADC的輸入時,它會不斷改變幅度。但是,模數(shù)轉(zhuǎn)換過程需要一定的時間間隔,在這段時間內(nèi),ADC輸入的幅度將發(fā)生變化(圖1)。正是這種幅度偏差導(dǎo)致了潛在的嚴(yán)重誤差。

圖1:由于數(shù)字化期間(下方)輸入信號幅度的變化,因此造成了ADC發(fā)生幅度誤差(上方)。(圖片來源:Digi-Key Electronics)

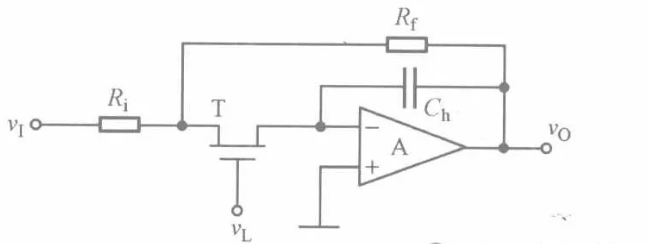

此時防止ADC中的幅度偏差就變成了轉(zhuǎn)換過程中如何對信號采樣并保持固定幅度的問題。這可通過對ADC使用S&H或T&H電路來實現(xiàn)(圖2)。

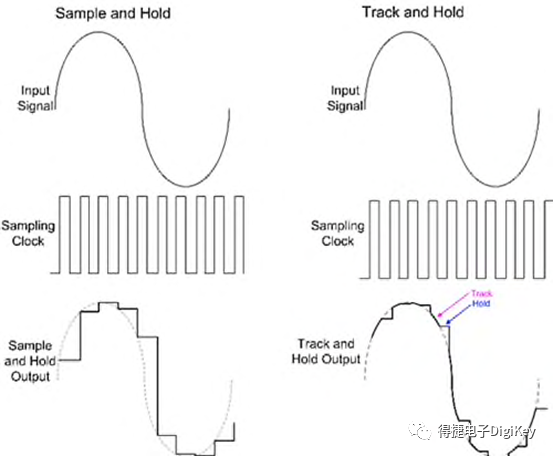

圖2:S&H(左)電路與T&H(右)電路的主要區(qū)別在于跟蹤周期的持續(xù)時間:即 S&H 較短,而T&H較長。(圖片來源:Digi-Key Electronics)

兩種類型的電路都對輸入信號進(jìn)行采樣,并在轉(zhuǎn)換過程中保持采樣電壓恒定。T&H電路輸出(右)跟蹤輸入信號,直到發(fā)出采樣信號;然后在ADC轉(zhuǎn)換期間保存該采樣值。S&H的采樣孔徑更短,其輸出是一系列采樣電平(左)。T&H和S&H之間的主要區(qū)別在于跟蹤間隔的持續(xù)時間:即S&H較短,而T&H較長。這兩個電路均依靠快速開關(guān)來隔離已連接至信號輸入端的儲能電容器。本文余下內(nèi)容中將使用S&H同時指代S&H或T&H。

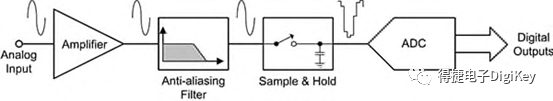

S&H級會執(zhí)行真實輸入采樣,工作區(qū)間位于輸入抗混疊低通濾波器和ADC之間。低通濾波器執(zhí)行抗混疊頻帶限制,且必須先于S&H,這樣便可在采樣前對信號進(jìn)行頻帶限制,以防止發(fā)生混疊(圖3)。

請注意,S&H之前的信號都是模擬信號。S&H的輸出是一個饋送至ADC的采樣波形。

典型的S&H器件

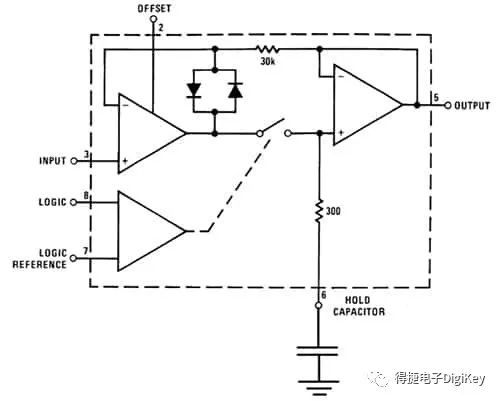

Texas Instruments LF398MX/NOPB S&H集成電路 (IC) 框圖顯示了基本電路配置(圖4)。S&H是使用快速開關(guān)和高質(zhì)量電容器實現(xiàn)的。對于LF398MX/NOPB,電容器在IC外部。當(dāng)開關(guān)閉合時,電容器就會充電至輸入信號電壓電平。當(dāng)開關(guān)斷開時,電容器保持該電壓,直到由ADC將其數(shù)字化為止。這個S&H使用了bi-FET技術(shù),將FET與雙極型晶體管組合在一起,以高直流精度(典型值0.002%)和極低電壓降(通常小于每秒83微伏 (μV))來支持快速采樣(小于6微秒 (μs),幅度誤差為0.01%)。內(nèi)部放大器緩沖了開關(guān)和保持電容器。

S&H的采樣時間取決于保持電容器的值,該值可能范圍為0.001至0.1微法拉 (μF)。外部保持電容器必須具有低介電吸收和低泄漏能力。建議使用聚苯乙烯、聚丙烯和聚四氟乙烯電容器。

圖4:Texas Instruments LF398MX/NOPB S&H框圖顯示了關(guān)鍵組件:快速開關(guān)和外部保持電容器。(圖片來源:Texas Instruments)

S&H特征

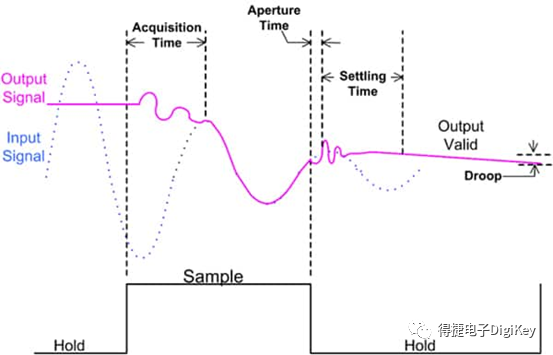

S&H器件具有許多用于描述其操作的特定術(shù)語(圖5)。

圖5:常見S&H動態(tài)特征的定義包括采樣時間、建立時間、孔徑時間和幅度下降。(圖片來源:Digi-Key Electronics)

采樣時間是指從切換到采樣模式到S&H開始跟蹤輸入信號的時間。它是保持電容器的值以及開關(guān)與信號路徑的串聯(lián)電阻的函數(shù)。當(dāng)模式恢復(fù)到保持狀態(tài)時,在器件停止跟蹤輸入并開始保持值前,可能會有一段時間延遲——這就是孔徑時間。孔徑時間是驅(qū)動器和開關(guān)傳播延遲的函數(shù)。孔徑不確定性或抖動是由于時鐘變化和噪聲導(dǎo)致的孔徑時間差異。

一旦進(jìn)入保持模式后,進(jìn)入該模式到器件的保持值穩(wěn)定在一個誤差帶內(nèi),之間會有一段時間,這個時間就是所謂的建立時間或保持建立時間。在建立時間的某些部分,在開關(guān)驅(qū)動器和保持電容器之間可能會包括不必要的電荷轉(zhuǎn)移;這就所謂的保持跳變或基座誤差。保持跳變的幅度通常在毫伏 (mV) 范圍內(nèi),并且通過將全范圍信號保持盡可能高,可以將其影響最小化。

S&H的最短采樣周期是采樣時間、孔徑時間和建立時間之和。可能的最大采樣率是采樣時間、孔徑時間和建立時間之和的倒數(shù)。

在保持模式下,由于保持電容的泄漏,S&H保持值可能會降低。此電壓增量稱為壓降。通常表示為以mV/秒為單位的下降率。

S&H配置

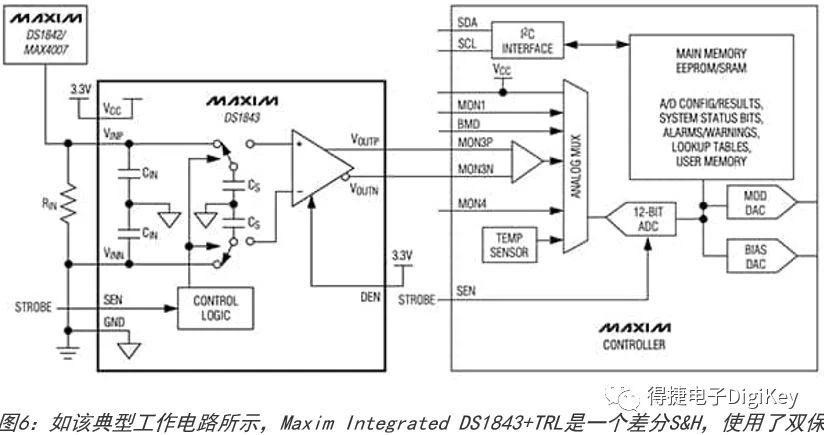

S&H IC具有多種配置,可滿足各種應(yīng)用需求。以一個需要差分輸入的應(yīng)用為例,比如需要連接像加速計、應(yīng)變計或光學(xué)電流監(jiān)控器這樣的差分輸出傳感器。Maxim Integrated DS1843D+TRL就是適合這種應(yīng)用的S&H IC好實例(圖6)。

圖6:如該典型工作電路所示,Maxim Integrated DS1843+TRL是一個差分S&H,使用了雙保持電容器來實現(xiàn)差分采樣。(圖片來源:MaximIntegrated)

所示DS1843+TRL用于一個典型的光學(xué)線路傳輸應(yīng)用,在該應(yīng)用中用于猝發(fā)模式接收信號強度指標(biāo) (RSSI) 測量。Maxim Integrated DS1842/MAX4007是一款電流監(jiān)視器,可鏡像來自連接其參考輸入的雪崩光電二極管的電流。輸出電流直接通過電阻RIN,并將其轉(zhuǎn)換為電壓。然后電壓由包括全差分采樣開關(guān)和電容器CS以及差分輸出緩沖器的DS1843進(jìn)行差分測量。這個S&H使用兩個5皮法拉 (pF) 電容器,一個電容器連接到正差分輸入,另一個連接到負(fù)差分輸入。低電容值可確保快速采樣時間。該器件的快速采樣時間少于300納秒 (ns)。該S&H的保持時間大于 100 μs。

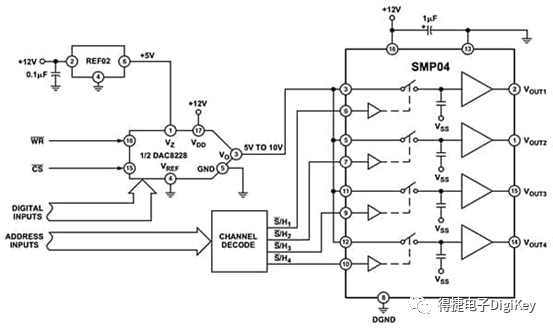

市面上提供的器件在單個IC封裝中可容納四個或八個S&H電路。例如,Analog Devices的SMP04ESZ-REEL四通道S&H。SMP04ESZ-REEL是一個CMOS器件,在一個通用封裝中包含了四個S&H電路,其采樣時間為7μs,下降率僅為2mV/s(圖7)。

圖7還展示了S&H如何與數(shù)模轉(zhuǎn)換器(DAC) 一起使用,在這種情況下,可以防止由于DAC中的代碼轉(zhuǎn)換而引起的輸出瞬變或毛刺。

圖7:Analog Devices SMP04四通道S&H包含四個獨立的S&H電路以及匹配的緩沖放大器。所示電路使用了SMP04,用于將DAC的輸出多路復(fù)用到四個通道。(圖片來源:Analog Devices)

在圖中,SMP04用于復(fù)用DAC的輸出,將單個DAC輸出分成四個多路復(fù)用通道。S&H電路可用于選擇性地將DAC的輸出延遲到毛刺之后,從而使DAC的輸出變得平滑。

通過對復(fù)用輸入進(jìn)行流水線處理,可以使用多個S&H電路來提高ADC的吞吐量。此處,有多個S&H共同連接到多路復(fù)用器輸出。ADC連接到一個S&H,后者保持用于轉(zhuǎn)換的輸入電平。其他S&H會獲取其他多路復(fù)用器通道,然后依次連接到ADC,而第一個S&H可自由連接到另外的多路復(fù)用通道。這種流水線處理技術(shù)消除了ADC信號路徑中的S&H采樣時間。

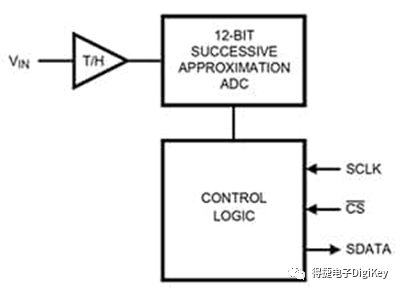

許多ADC在其集成封裝中都集成了S&H或T&H電路。舉例來說,Texas Instruments的ADC121S021CIMFX就是一個具有內(nèi)置T&H的12位逐次逼近寄存器(SAR) ADC,采樣率為每秒50至200千樣本 (kS/s)。它采用高速串行輸出總線,簡化了接線布局(圖8)。

圖8:Texas Instruments ADC121S021是一個具有內(nèi)置T&H電路的12位單通道SARADC。(圖片來源:Texas Instruments)

這個ADC是許多集成ADC電路的典型代表,因為它具有內(nèi)部T&H,從而簡化了印刷電路板的布局,且有助于最大程度地減少組件數(shù)。外部T&H電路用于特殊配置,例如用于差分輸入連接、多路復(fù)用輸入,或用在ADC不具有內(nèi)部T&H或S&H電路時。

總結(jié)

從音頻記錄到最先進(jìn)的IIoT或AI分析,將模擬信號轉(zhuǎn)換為數(shù)字信號是最基本的電子功能,需要特別注意S&H或T&H電路。為了將模數(shù)轉(zhuǎn)換過程中的電壓偏差降至最低,這些電路至關(guān)重要,因為它們在轉(zhuǎn)換過程中可以讓ADC的輸入電壓保持恒定。S&H可以設(shè)在ADC內(nèi)部或外部,但必須位于抗混疊低通濾波器和ADC之間的信號路徑中。如前文所述,有許多配置可以滿足各種設(shè)計應(yīng)用需要,每個IC還有單通道、差分或多通道選擇。應(yīng)用還可擴(kuò)展到包括防止因 DAC 中代碼轉(zhuǎn)換引起輸出瞬變或毛刺。

原文標(biāo)題:模擬設(shè)計小竅門:巧用采樣和保持電路,確保ADC精度

文章出處:【微信公眾號:得捷電子DigiKey】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

電路

+關(guān)注

關(guān)注

173文章

6022瀏覽量

174368 -

adc

+關(guān)注

關(guān)注

99文章

6635瀏覽量

548186 -

信號

+關(guān)注

關(guān)注

11文章

2841瀏覽量

77870

原文標(biāo)題:模擬設(shè)計小竅門:巧用采樣和保持電路,確保ADC精度

文章出處:【微信號:得捷電子DigiKey,微信公眾號:得捷電子DigiKey】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

ADC采樣率與信號頻率:關(guān)鍵概念與設(shè)計要點

ADC技術(shù)的工作原理解析

ADC量化位數(shù)只有兩位,將采樣結(jié)果做FFT分析后,發(fā)現(xiàn)二次諧波的幅度最大,請教是什么原因造成的?

ADC采樣保持過程的具體時間要如何確定?

用ADS8317采樣,如果基準(zhǔn)偏差,對結(jié)果的采樣精度有影響嗎?

高速ADC設(shè)計中采樣時鐘影響的考量

ADC344X或者ADC34J4X系列ADC內(nèi)部有沒有集成采樣保持器(S/H)?

如何優(yōu)化adc的采樣率

adc3101的采樣率由什么來決定呢?

ADC采樣保持電路的工作原理和技術(shù)指標(biāo)

TLV9062IDR的電流采樣電路,請問運放本身偏差大小是否正常?

使用單通道ADC+模擬開關(guān)結(jié)構(gòu)采樣多路信號時,ADC采樣率如何選擇呢?

ADC08DJ5200RF射頻采樣千兆采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC12DJ5200-EP射頻采樣千兆采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

如何使用ADC的采樣和保持電路來防止幅度偏差?

如何使用ADC的采樣和保持電路來防止幅度偏差?

評論