01

概述

本文通過(guò)matlab自帶的工具箱生成一個(gè)可編程FIR濾波器的硬件HDL代碼,可生成VHDL或者Verilog HDL兩種類型的代碼。

02

具體操作步驟

新建一個(gè)matlab的腳本,鍵入下面兩行代碼,這里是直接調(diào)用matlab已經(jīng)定義好的“dspprogfirhdl”模型,然后在simulink工具中打開(kāi)該系統(tǒng)模型。

modelname = ‘dspprogfirhdl’;open_system(modelname)

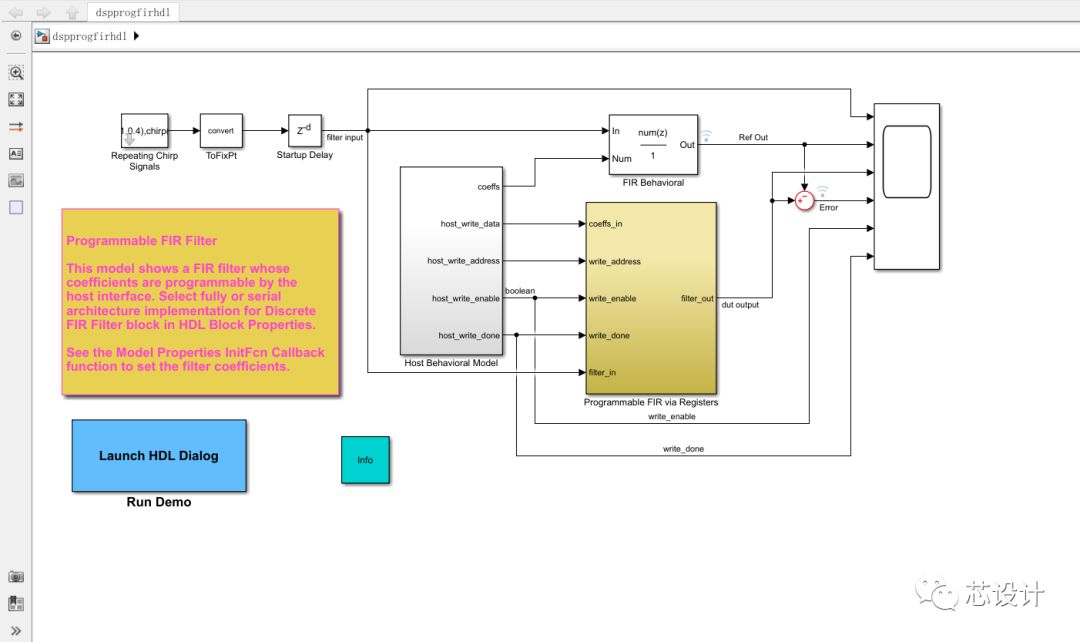

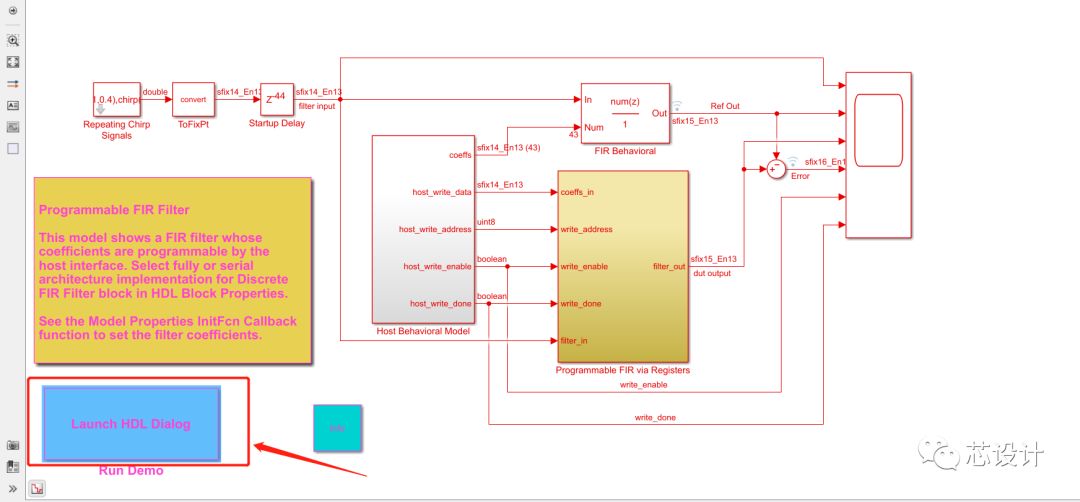

運(yùn)行上面兩行代碼后,會(huì)打開(kāi)simulink并出現(xiàn)下圖:

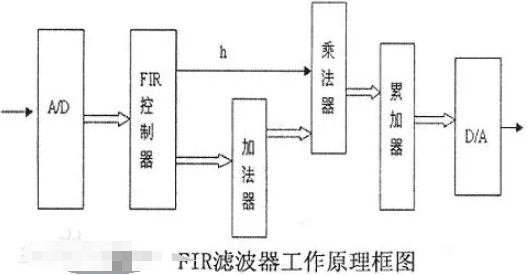

上圖就是“dspprogfirhdl”模型的結(jié)構(gòu)圖, 圖中Host Behavioral Model 是用來(lái)產(chǎn)生可編程FIR濾波器的系數(shù)(低通或者高通濾波器系數(shù)),Programmable FIR via Registers 是我們要生成的可編程濾波器模塊,F(xiàn)IR Behavioral 是一個(gè)行為級(jí)的參考模塊,它用來(lái)和可編程濾波器模塊做結(jié)果的比對(duì)。

雙擊上圖中的 Programmable FIR via Registers 模塊或者運(yùn)行如下腳本中:

systemname = [modelname ‘/Programmable FIR via Registers’];open_system(systemname);

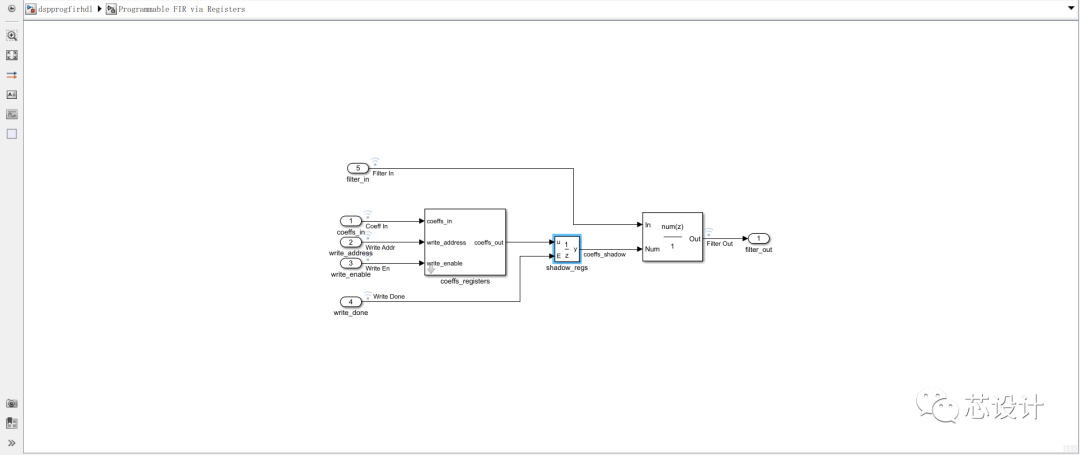

會(huì)出現(xiàn)下圖,這是programmable FIR via Registers模塊的內(nèi)部結(jié)構(gòu):

上圖中coeffs_registers 是一個(gè)FIR 濾波器的系數(shù)寄存器,當(dāng)‘write_enable’ 信號(hào)拉高寫(xiě)FIR的系數(shù);當(dāng) ‘write_done’ 拉高,也就是寫(xiě)完成時(shí), shadow registers 才會(huì)更新一次FIR的濾波器系數(shù),該模型生成的HDL代碼默認(rèn)是全并行的結(jié)構(gòu)實(shí)現(xiàn),可根據(jù)需要改為串行流水結(jié)構(gòu)。

開(kāi)始執(zhí)行仿真,以及查看仿真波形,執(zhí)行如下代碼;

sim(modelname);open_system([modelname ‘/Scope’]);

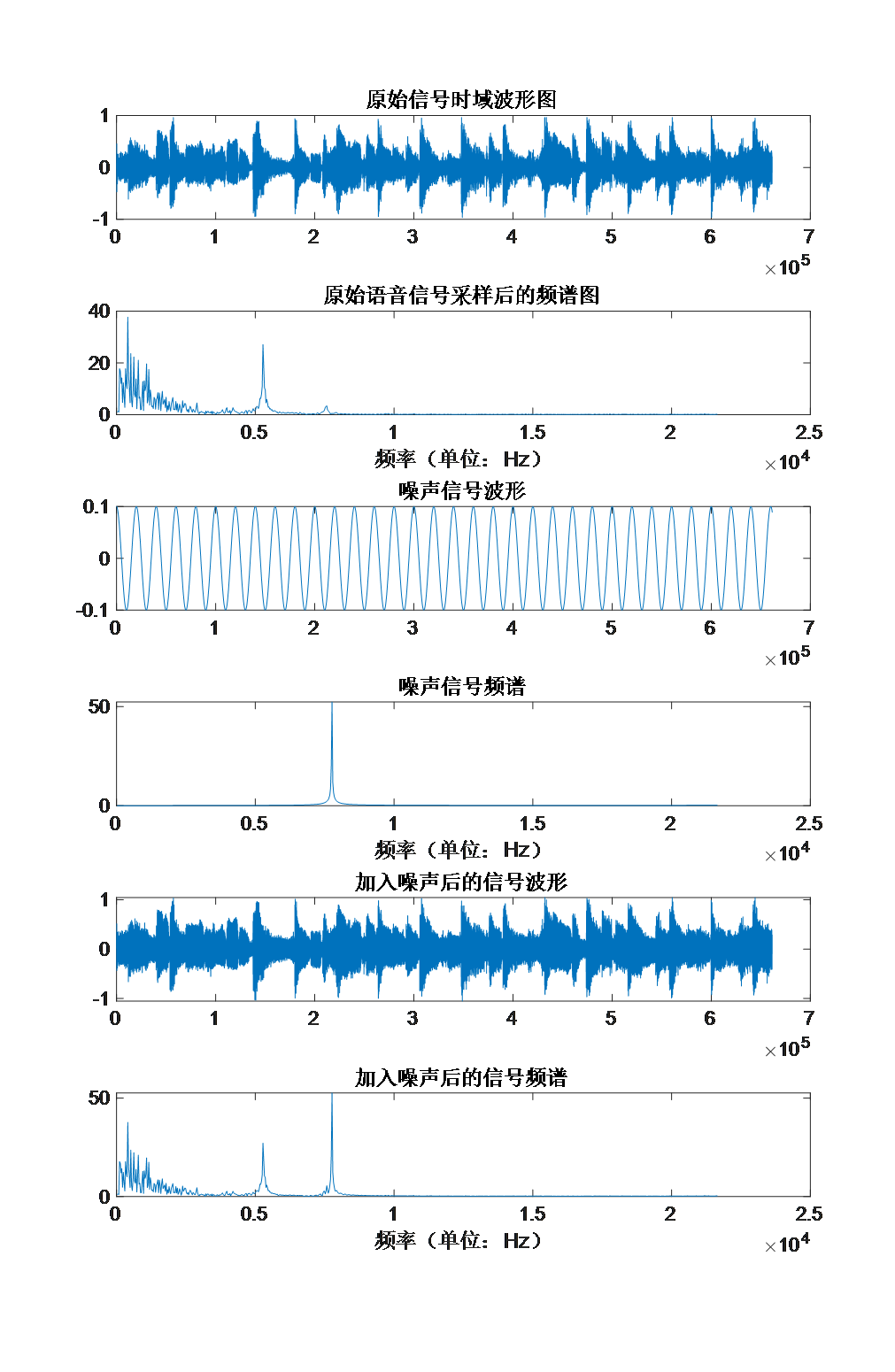

會(huì)生成如下的仿真結(jié)果:

上圖中,filter_input是輸入的信號(hào),ref_out和dut output是參考模型和dut的輸出結(jié)果,error是二者的結(jié)果比對(duì)情況。

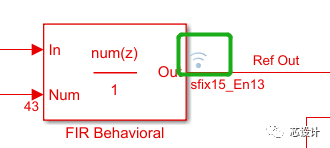

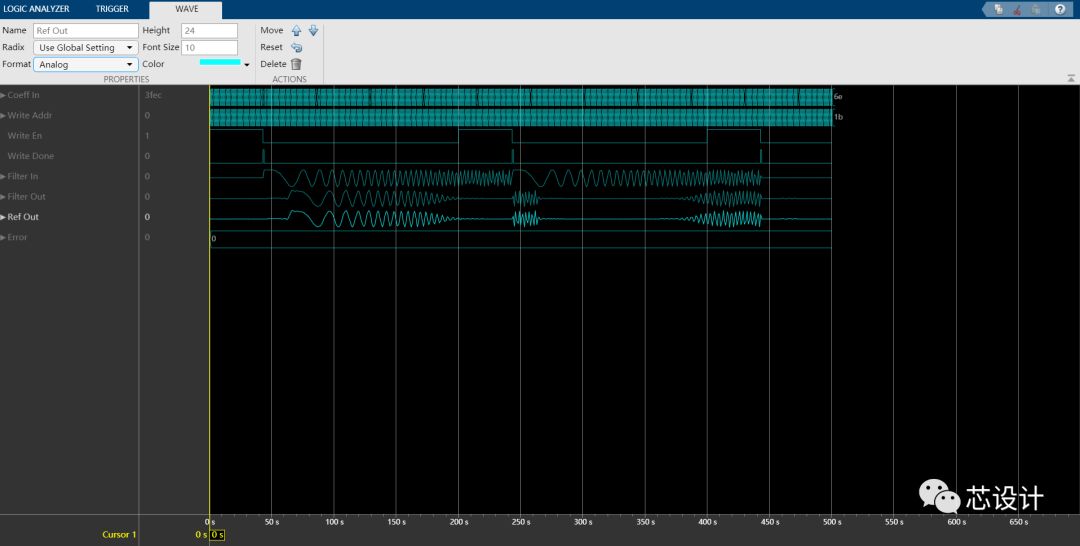

也可以使用simulink工具中的 Logic Analyzer邏輯分析儀查看波形,點(diǎn)擊本文第一張圖中的wifi符號(hào),如下圖:

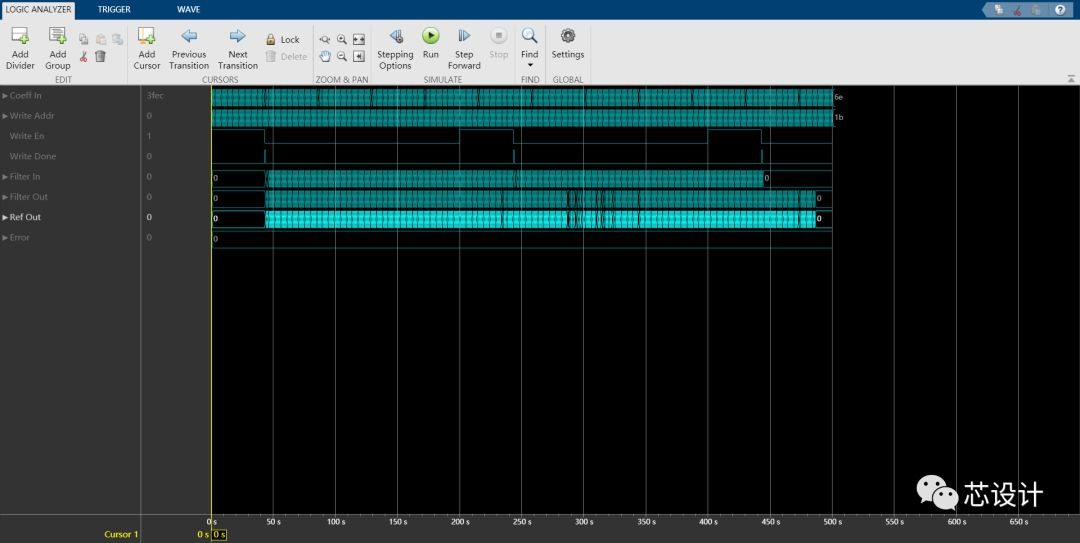

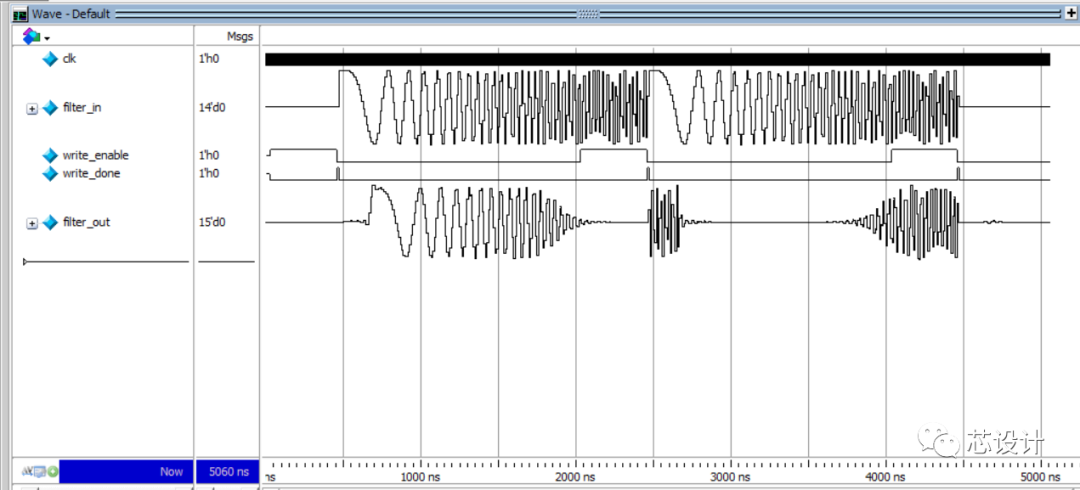

最后會(huì)在 Logic Analyzer中生成如下的波形圖:

將filter濾波器輸入信號(hào)和輸出信號(hào)用模擬形式展開(kāi),如下圖:

03

生成HDL代碼

下面通過(guò)兩種方式生成HDL代碼

方式一(腳本):

腳本中鍵入如下代碼,生成HDL的dut代碼(默認(rèn)生成.vhd的代碼):

workingdir = tempname;makehdl(systemname,‘TargetDirectory’,workingdir);

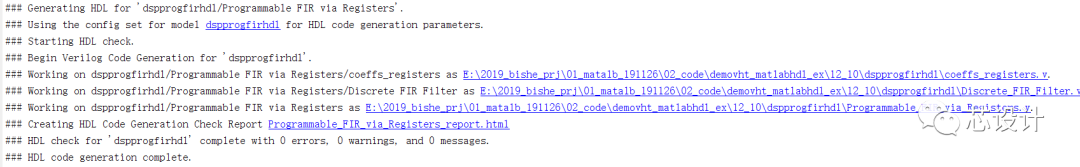

matlab命令行窗口中出現(xiàn)如下圖,表示成功FIR濾波器的DUT代碼:

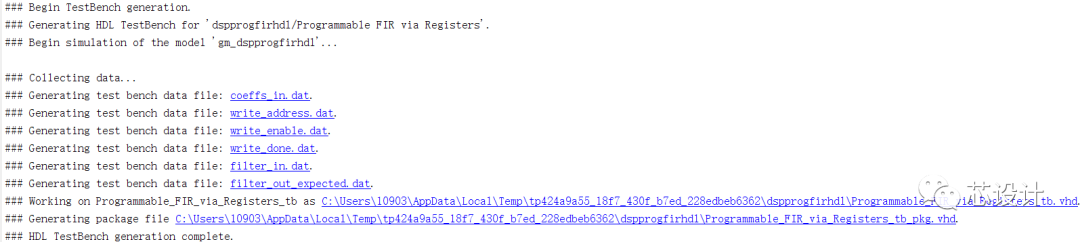

腳本中鍵入如下代碼,生成HDL的tb代碼:

makehdltb(systemname,‘TargetDirectory’,workingdir);

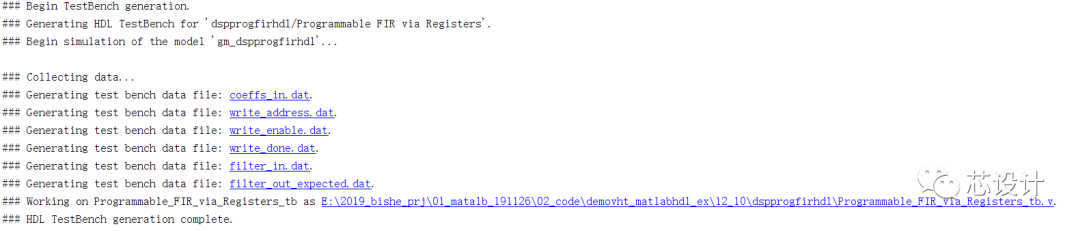

matlab命令行窗口中出現(xiàn)如下圖,表示成功FIR濾波器的TB代碼:

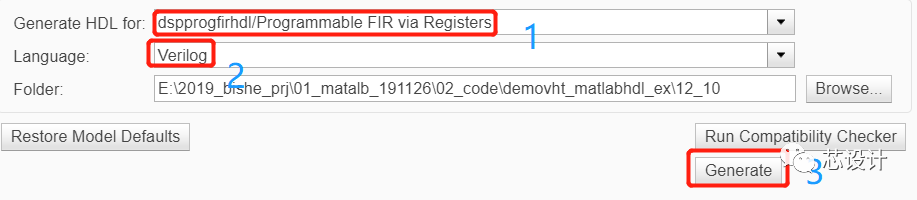

方式二(界面):

在下圖中雙擊箭頭所示部分,會(huì)出現(xiàn)configration配置界面(生成.v格式的代碼):

出現(xiàn)下圖,按照如下圖操作1,2,3,然后點(diǎn)擊下方generate。

matlab的命令行出現(xiàn)下圖,表示成功生成FIR濾波器的DUT代碼:

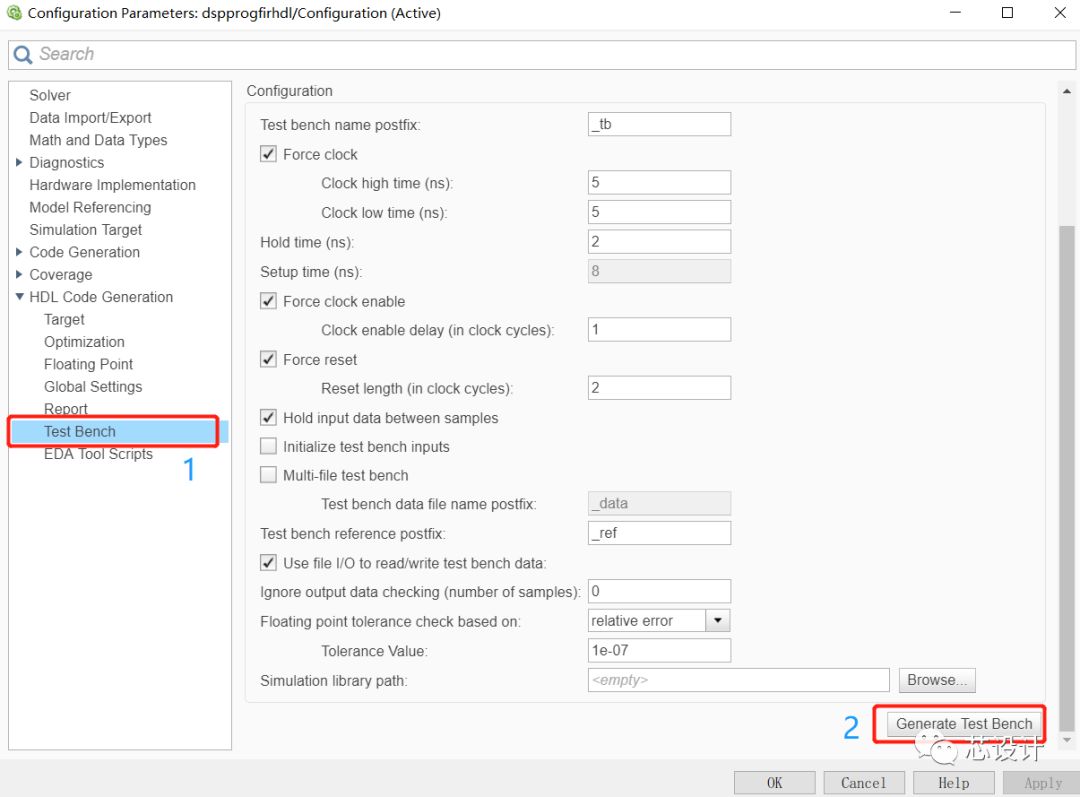

在configuration中選取testbench然后點(diǎn)擊生成testbench即可。

matlab的命令行出現(xiàn)下圖,表示成功生成FIR濾波器的TB代碼:

04

modelsim工具仿真

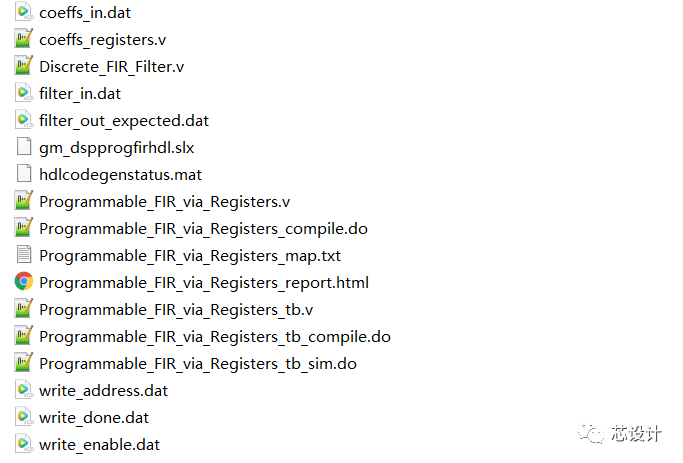

經(jīng)過(guò)matlab工具生成可編程的FIR濾波器HDL代碼后,在工作目錄中會(huì)有如下的文件(包括:仿真用的數(shù)據(jù).dat文件,dut和tb文件,run.do腳本):

使用modelsim仿真后的結(jié)果如下:

原文標(biāo)題:matlab工具生成可編程FIR濾波器的HDL代碼

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

matlab

+關(guān)注

關(guān)注

188文章

2994瀏覽量

233116 -

濾波器

+關(guān)注

關(guān)注

162文章

8051瀏覽量

180853

原文標(biāo)題:matlab工具生成可編程FIR濾波器的HDL代碼

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

HMC1023LP5E 72MHz雙通道可編程低通濾波器技術(shù)手冊(cè)

使用DDS生成三個(gè)信號(hào)并在Vivado中實(shí)現(xiàn)低通濾波器

ADS7066有可編程濾波器,請(qǐng)問(wèn)使用該濾波器時(shí),是否可以簡(jiǎn)化設(shè)計(jì)抗混疊濾波的截止頻率?

基于FPGA實(shí)現(xiàn)FIR數(shù)字濾波器

PurePath Studio配置好濾波器后,生成代碼遇到的疑問(wèn)求解

基于MATLAB的數(shù)字濾波器語(yǔ)音信號(hào)去噪

利用可編程可變電阻濾波器提高分辨率的ADS7138

具有可編程FIR和IIR濾波器的Δ-Σ ADC的優(yōu)點(diǎn)

TLV320ADCx140/PCMx140-Q1可編程雙二階濾波器配置和應(yīng)用

TLV320ADCx120和PCMx120-Q1可編程雙二階濾波器配置和應(yīng)用

FIR濾波器的工作原理和特點(diǎn)

如何區(qū)分IIR濾波器和FIR濾波器

iir濾波器和fir濾波器的優(yōu)勢(shì)和特點(diǎn)

ADS127L21具有可編程濾波器的512kSPS、24位寬帶Δ-ΣADC數(shù)據(jù)表

如何用matlab生成一個(gè)可編程FIR濾波器的硬件HDL代碼?

如何用matlab生成一個(gè)可編程FIR濾波器的硬件HDL代碼?

評(píng)論