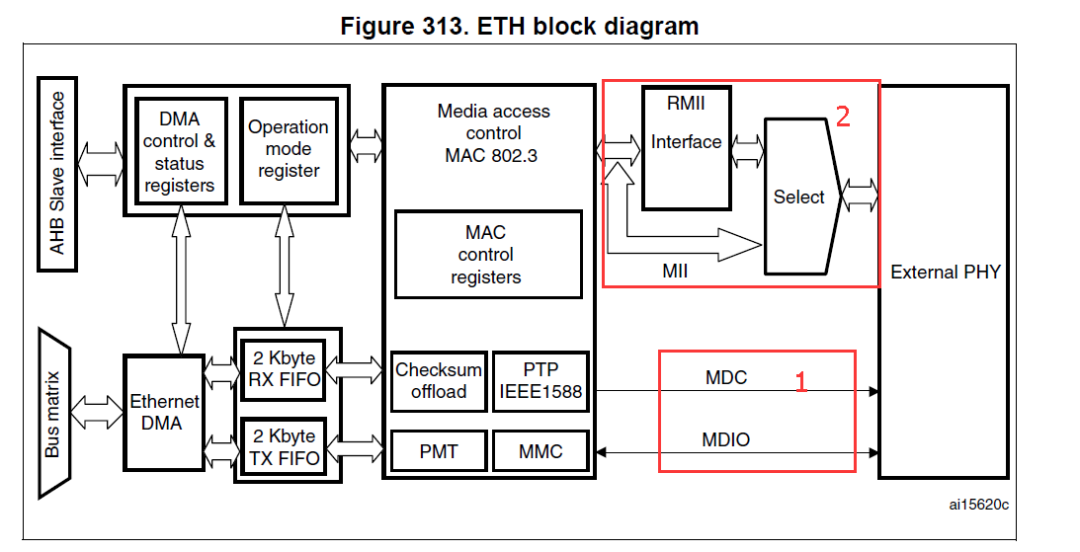

如果有同學對SMI,MII和RMII接口不熟悉,建議看一下上面提到的兩篇文章,不然可能看不太懂下文。

區域1:我們稱為SMI接口,用于配置外部PHY芯片。

區域2:是數據交換接口,也就是上面我們說的MII接口和RMII接口。

利用這些接口可以有多種不同的網絡電路設計方案,這里我來總結下。

01MII接口方案

MII接口在文章《STM32網絡之MII和RMII》已經詳細介紹過了,從中得知,需要一個25MHz的時鐘。

對于MII接口,最常用的方案是,STM32外接25MHz的晶振。

內部的PLL配置HCLK,提供給內核和外設等。

外部PHY連接提供了25MHz的MCO腳。

此方案適合STM32F107/2x7/4x7。

02RMII接口方案

RMII接口在文章《STM32網絡之MII和RMII》已經詳細介紹過了,從中得知,需要一個50MHz的時鐘。

2.1、外部晶振(2個晶振)

這個方案需要外接連里兩個晶振。

外接25MHz晶振,內部的PLL配置HCLK,提供給內核和外設等。

外接50MHz晶振,輸出50MHz時鐘,提供給MAC控制器和外部PHY。

此方案適合STM32F107/2x7/4x7。

2.2、外部晶振(1個晶振)

這種方案外部只需要接1個50M晶振。一個晶振同時給STM32和外部PHY提供時鐘,這樣可以省成本。

重點:STM32F2X7不能使用這種方案,只適用于STM32F107/4x7。

大家注意上圖的區別

這是因為,將HSE的OSC部分濾除掉,通過HSE的bypass,已經將50MHz的時鐘通過OSCIN輸入到PLL,再通過PLL產生提供內核和外設的時鐘。

2.3、需要強力PHY

這個方案也使用一個25MHz的晶振,但是需要一個功能強大的PHY芯片,這顆PHY可以將輸入的25MHz的時鐘內部倍頻到50MHz時鐘,然后輸出給STM32的MAC控制模塊。

外接25MHz晶振,內部的PLL配置HCLK,提供給內核和外設等。

STM32通過MCO引腳提供25MHz時鐘給外部PHY。

外部PHY內部生成50MHz的時鐘提供給STM32的MAC控制模塊。

此方案適合STM32F107/2x7/4x7。

個人不建議這種方案,不利于后期更換物料。

編輯:lyn

-

電路

+關注

關注

173文章

6022瀏覽量

174359 -

晶振

+關注

關注

34文章

3187瀏覽量

69489 -

smt

+關注

關注

42文章

3014瀏覽量

71215

原文標題:STM32網絡電路設計

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

華為發布5G-A毫米波萬兆網絡

電科網安榮獲2024年網絡安全技術應用典型案例

Jtti:中國電信CN2網絡與其他網絡相比有何優勢?

RJ45網絡故障排除技巧 RJ45網線的長度對信號影響

RJ45網絡接口的安裝指南 RJ45與其他網絡接口的區別

過壓保護電路的多種設計方案

基于改進ResNet50網絡的自動駕駛場景天氣識別算法

常見的IPv6網絡問題與解決

如何配置IPv6網絡

如何在RS-485網絡中使用MSP430和MSP432 eUSCI和USCI模塊

藍牙Mesh 1.1網絡的性能測試

廣和通通過IEC 62443-4-1網絡安全體系認證

廣和通通過IEC 62443-4-1網絡安全體系認證

關于STM32網絡電路設計方案

關于STM32網絡電路設計方案

評論