本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處(http://www.alinx.com)。

適用于板卡型號(hào):

PGL22G/PGL12G

1. 實(shí)驗(yàn)簡(jiǎn)介

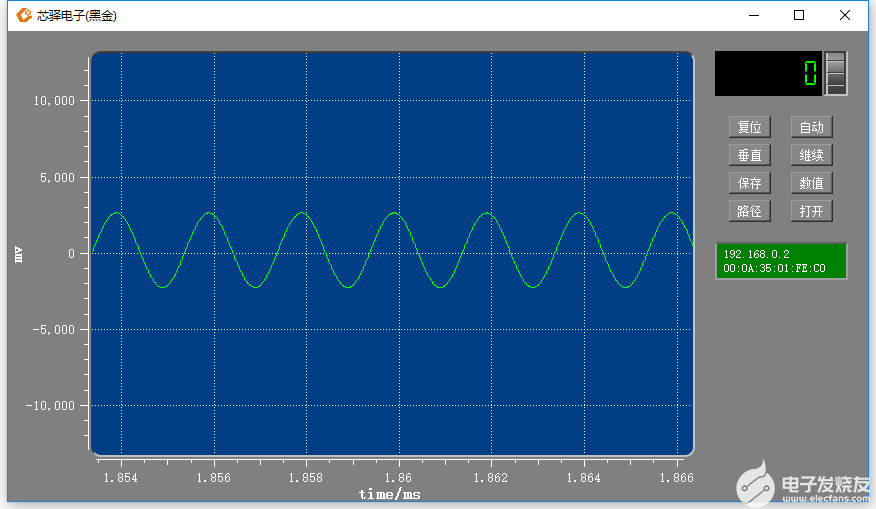

本實(shí)驗(yàn)練習(xí)使用ADC,實(shí)驗(yàn)中使用的ADC模塊型號(hào)為AN9238,最大采樣率65Mhz,精度為12位。實(shí)驗(yàn)中把AN9238的2路輸入以波形方式在HDMI上顯示出來(lái),我們可以用更加直觀(guān)的方式觀(guān)察波形,是一個(gè)數(shù)字示波器雛形。

AN9238雙路65M采樣12位ADC模塊實(shí)驗(yàn)預(yù)期結(jié)果

2. 實(shí)驗(yàn)原理

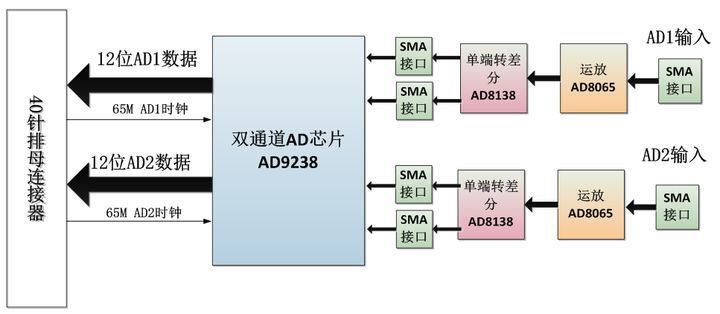

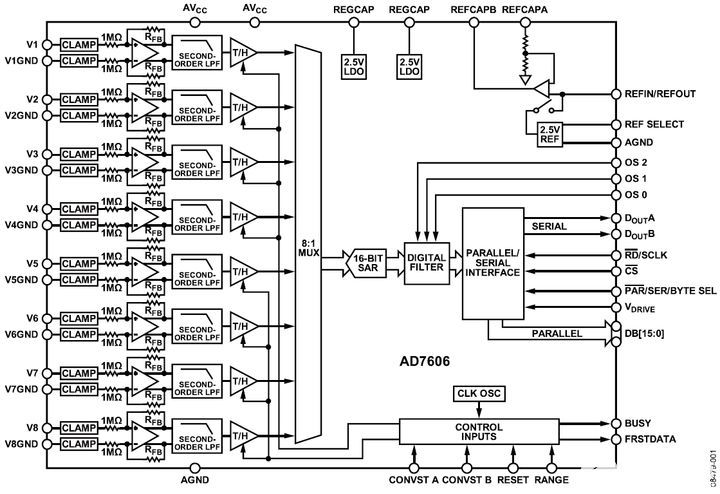

黑金高速AD模塊AN9238為2路65MSPS, 12位的模擬信號(hào)轉(zhuǎn)數(shù)字信號(hào)模塊。模塊的AD轉(zhuǎn)換采用了ADI公司的AD9238芯片, AD9238芯片支持2路AD輸入轉(zhuǎn)換,所以1片AD9238芯片一共支持2路的AD輸入轉(zhuǎn)換。模擬信號(hào)輸入支持單端模擬信號(hào)輸入,輸入電壓范圍為-5V~+5V,接口為SMA插座。

AN9238模塊的原理設(shè)計(jì)框圖如下:

關(guān)于AD9238的電路具體參考設(shè)計(jì)請(qǐng)參考AD9238的芯片手冊(cè)。

2.1 單端輸入及運(yùn)放電路

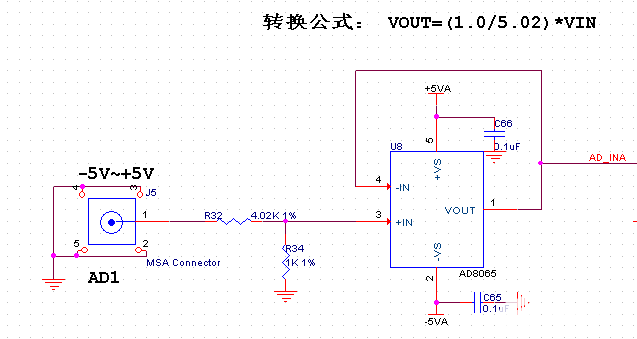

單端輸入AD1和AD2通過(guò)J5或者J6兩個(gè)SMA頭輸入,單端輸入的電壓為-5V~+5V。

板上通過(guò)運(yùn)放AD8065芯片和分壓電阻把-5V~+5V輸入的電壓縮小成-1V~+1V。如果用戶(hù)想輸入更寬范圍的電壓輸入只要修改前端的分壓電阻的阻值。

下表為模擬輸入信號(hào)和AD8065運(yùn)放輸出后的電壓對(duì)照表:

| AD模擬輸入值 | AD8065運(yùn)放輸出 |

| -5V | -1V |

| 0V | 0V |

| +5V | +1V |

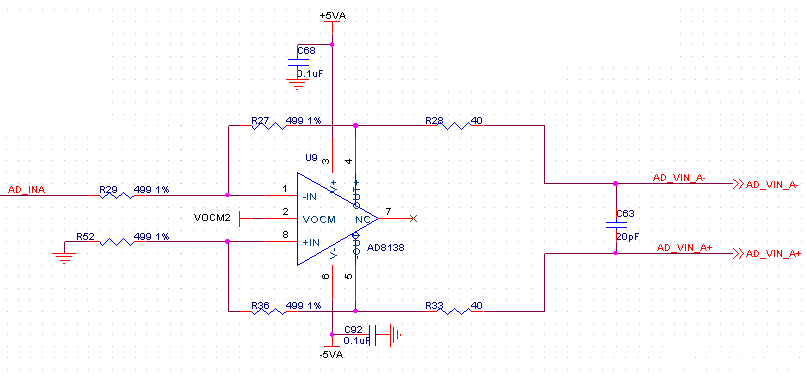

2.2 單端轉(zhuǎn)差分及AD轉(zhuǎn)換

-1V~+1V的輸入電壓通過(guò)AD8138芯片轉(zhuǎn)換成差分信號(hào)(VIN+ ? VIN?), 差分信號(hào)的共模電平由AD的CML管腳決定。

下表為模擬輸入信號(hào)到AD8138差分輸出后的電壓對(duì)照表:

| AD模擬輸入值 | AD8065運(yùn)放輸出 | AD8138差分輸出(VIN+?VIN?) |

| -5V | -1V | -1V |

| 0V | 0V | 0V |

| +5V | +1V | +1V |

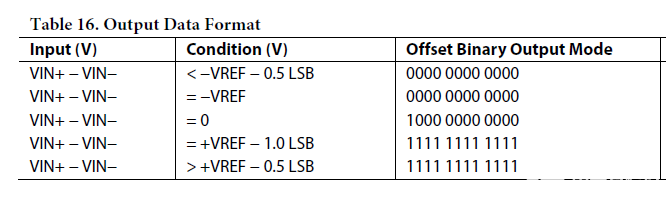

2.3 AD9238轉(zhuǎn)換

默認(rèn)AD是配置成offset binary的,AD轉(zhuǎn)換的值如下圖所示:

在模塊電路設(shè)計(jì)中,AD9238的VREF的值為1V,這樣最終的模擬信號(hào)輸入和AD轉(zhuǎn)換的數(shù)據(jù)如下:

| AD模擬輸入值 | AD8055運(yùn)放輸出 | AD8138差分輸出(VIN+?VIN?) | AD9238數(shù)字輸出 |

| -5V | -1V | -1V | 000000000000 |

| 0V | 0V | 0V | 100000000000 |

| +5V | +1V | +1V | 11111111111 |

從表中我們可以看出,-5V輸入的時(shí)候,AD9238轉(zhuǎn)換的數(shù)字值最小,+5V輸入的時(shí)候,AD9238轉(zhuǎn)換的數(shù)字值最大。

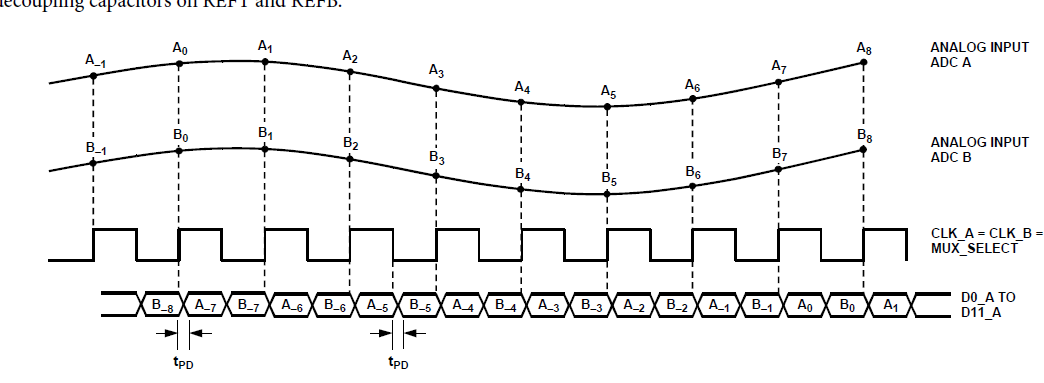

2.4 AN9238數(shù)字輸出時(shí)序

AD9238雙通道AD的數(shù)字輸出為+3.3V的CMOS輸出模式,2路通道(A和B)獨(dú)立的數(shù)據(jù)和時(shí)鐘。AD數(shù)據(jù)在時(shí)鐘的上降沿轉(zhuǎn)換數(shù)據(jù),FPGA端可用AD時(shí)鐘的采樣AD數(shù)據(jù)。

3. 程序設(shè)計(jì)

本實(shí)驗(yàn)顯示部分是基于前面的已有的實(shí)驗(yàn),在彩條上疊加網(wǎng)格線(xiàn)和波形。

timing_gen_xy模塊完成視頻圖像的坐標(biāo)生成,x坐標(biāo),從左到右增大,y坐標(biāo)從上到下增大。

| 信號(hào)名稱(chēng) | 方向 | 寬度(bit) | 說(shuō)明 |

| clk | in | 1 | 系統(tǒng)時(shí)鐘 |

| rst_n | in | 1 | 異步復(fù)位,低電平復(fù)位 |

| i_hs | in | 1 | 視頻行同步輸入 |

| i_vs | in | 1 | 視頻場(chǎng)同步輸入 |

| i_de | in | 1 | 視頻數(shù)據(jù)有效輸入 |

| i_data | in | 24 | 視頻數(shù)據(jù)輸入 |

| o_hs | out | 1 | 視頻行同步輸出 |

| o_vs | out | 1 | 視頻場(chǎng)同步輸出 |

| o_de | out | 1 | 視頻數(shù)據(jù)有效輸出 |

| o_data | out | 24 | 視頻數(shù)據(jù)輸出 |

| x | out | 12 | 坐標(biāo)x輸出 |

| y | out | 12 | 坐標(biāo)y輸出 |

timing_gen_xy模塊端口

grid_display模塊主要完成視頻的網(wǎng)格線(xiàn)疊加,本實(shí)驗(yàn)將彩條視頻輸入,然后疊加一個(gè)網(wǎng)格后輸出,提供給后面的波形顯示模塊使用。

| 信號(hào)名稱(chēng) | 方向 | 寬度(bit) | 說(shuō)明 |

| pclk | in | 1 | 像素時(shí)鐘 |

| rst_n | in | 1 | 異步復(fù)位,低電平復(fù)位 |

| i_hs | in | 1 | 視頻行同步輸入 |

| i_vs | in | 1 | 視頻場(chǎng)同步輸入 |

| i_de | in | 1 | 視頻數(shù)據(jù)有效輸入 |

| i_data | in | 24 | 視頻數(shù)據(jù)輸入 |

| o_hs | out | 1 | 帶網(wǎng)格視頻行同步輸出 |

| o_vs | out | 1 | 帶網(wǎng)格視頻場(chǎng)同步輸出 |

| o_de | out | 1 | 帶網(wǎng)格視頻數(shù)據(jù)有效輸出 |

| o_data | out | 24 | 帶網(wǎng)格視頻數(shù)據(jù)輸出 |

grid_display模塊端口

wav_display顯示模塊主要是完成波形數(shù)據(jù)的疊加顯示,模塊內(nèi)含有一個(gè)雙口ram,寫(xiě)端口是由ADC采集模塊寫(xiě)入,讀端口是顯示模塊。

| 信號(hào)名稱(chēng) | 方向 | 寬度(bit) | 說(shuō)明 |

| pclk | in | 1 | 像素時(shí)鐘 |

| rst_n | in | 1 | 異步復(fù)位,低電平復(fù)位 |

| wave_color | in | 24 | 波形顏色,rgb |

| adc_clk | in | 1 | adc模塊時(shí)鐘 |

| adc_buf_wr | in | 1 | adc數(shù)據(jù)寫(xiě)使能 |

| adc_buf_addr | in | 12 | adc數(shù)據(jù)寫(xiě)地址 |

| adc_buf_data | in | 8 | adc數(shù)據(jù),無(wú)符號(hào)數(shù) |

| i_hs | in | 1 | 視頻行同步輸入 |

| i_vs | in | 1 | 視頻場(chǎng)同步輸入 |

| i_de | in | 1 | 視頻數(shù)據(jù)有效輸入 |

| i_data | in | 24 | 視頻數(shù)據(jù)輸入 |

| o_hs | out | 1 | 帶網(wǎng)格視頻行同步輸出 |

| o_vs | out | 1 | 帶網(wǎng)格視頻場(chǎng)同步輸出 |

| o_de | out | 1 | 帶網(wǎng)格視頻數(shù)據(jù)有效輸出 |

| o_data | out | 24 | 帶網(wǎng)格視頻數(shù)據(jù)輸出 |

wav_display模塊端口

ad9226_sample模塊主要完成ad9226輸入數(shù)據(jù)順序調(diào)整,因?yàn)閍d9226輸入的數(shù)據(jù)MSB在最低位。再把有符號(hào)數(shù)轉(zhuǎn)換為無(wú)符號(hào)數(shù),最后位寬轉(zhuǎn)換到8bit。

| 信號(hào)名稱(chēng) | 方向 | 寬度(bit) | 說(shuō)明 |

| adc_clk | in | 1 | adc系統(tǒng)時(shí)鐘 |

| rst | in | 1 | 異步復(fù)位,高復(fù)位 |

| adc_data | in | 12 | ADC數(shù)據(jù)輸入,MSB在最低位,需要倒序 |

| adc_buf_wr | out | 1 | ADC數(shù)據(jù)寫(xiě)使能 |

| adc_buf_addr | out | 12 | ADC數(shù)據(jù)寫(xiě)地址 |

| adc_buf_data | out | 8 | 無(wú)符號(hào)8位ADC數(shù)據(jù) |

ad9226_sample模塊端口

4. 實(shí)驗(yàn)現(xiàn)象

1)將AN9238模塊插入開(kāi)發(fā)板的擴(kuò)展口J8,注意1腳對(duì)齊,不要插錯(cuò)、插偏,不能帶電操作。

2)連接AN9238的輸入到信號(hào)發(fā)生器的輸出,這里使用的是專(zhuān)用屏蔽線(xiàn),如果使用其他線(xiàn)可能會(huì)有較大干擾。

AN9238連接信號(hào)源示意圖

3)連接HDMI顯示器,注意:連接的是顯示器,不是筆記本電腦HDMI接口

HDMI接口連接示意圖

4)下載程序,調(diào)節(jié)信號(hào)發(fā)生的頻率和幅度,AN9238輸入范圍-5V-5V,為了便于觀(guān)察波形數(shù)據(jù),建議信號(hào)輸入頻率200Khz到1Mhz。觀(guān)察顯示器輸出,紅色波形為AD1輸入、藍(lán)色為AD2輸入、黃色網(wǎng)格最上面橫線(xiàn)代表5V,最下面橫線(xiàn)代表-5V,中間橫線(xiàn)代表0V,每個(gè)豎線(xiàn)間隔是10個(gè)采樣點(diǎn)。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21949瀏覽量

613716 -

adc

+關(guān)注

關(guān)注

99文章

6626瀏覽量

548158 -

數(shù)字示波器

+關(guān)注

關(guān)注

7文章

548瀏覽量

34432 -

波形顯示

+關(guān)注

關(guān)注

0文章

4瀏覽量

9299 -

紫光同創(chuàng)

+關(guān)注

關(guān)注

5文章

95瀏覽量

27852

發(fā)布評(píng)論請(qǐng)先 登錄

【紫光同創(chuàng)國(guó)產(chǎn)FPGA教程】【第十八章】AD實(shí)驗(yàn)之AD7606波形顯示

【紫光同創(chuàng)國(guó)產(chǎn)FPGA教程】【第二十四章】AD9238以太網(wǎng)傳輸

國(guó)產(chǎn)FPGA介紹-紫光同創(chuàng)

AD9238

【紫光同創(chuàng)國(guó)產(chǎn)FPGA教程】【PGC1/2KG第二章】LED 流水燈實(shí)驗(yàn)例程

紫光同創(chuàng)FPGA開(kāi)發(fā)套件,高性能國(guó)產(chǎn)FPGA方案

AD9238,pdf datasheet (Dual AD

【正點(diǎn)原子FPGA連載】第二十七章DS18B20數(shù)字溫度傳感器實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開(kāi)發(fā)指南_V2.1

【正點(diǎn)原子FPGA連載】第三十七章雙路高速AD實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開(kāi)發(fā)指南_V2.1

"STM32H7學(xué)習(xí)繼續(xù)(STM32H7系列5)第十七章比較實(shí)用,以后寫(xiě)程序的時(shí)候會(huì)用到"

【紫光同創(chuàng)國(guó)產(chǎn)FPGA教程】【第十七章】AD實(shí)驗(yàn)之AD9238波形顯示

【紫光同創(chuàng)國(guó)產(chǎn)FPGA教程】【第十七章】AD實(shí)驗(yàn)之AD9238波形顯示

評(píng)論