本文給想直接使用Vitis HLS 工具在 Standalone 模式下調(diào)用 Xilinx Vision Library L1 API 的小伙伴提供了一個(gè)非常容易上手的腳本文件。

在論壇上遇到在高層次綜合工具中調(diào)用視覺庫遇到的大多數(shù)問題都和 opencv 庫以及Xilinx Vision 庫的安裝路徑有關(guān),如今 Vitis HLS 2020.1 之后的版本都不再提供OpenCV 的預(yù)編譯庫,就更需要開發(fā)者們將各自工作環(huán)境中的庫路徑,環(huán)境變量都設(shè)置好。希望這篇博文能給大家調(diào)用 Vitis Vision Library 提供向?qū)В嵘省?/p>

Vitis Vision庫

Vitis Vision 庫是 Xilinx 官方將 Opencv 功能轉(zhuǎn)換至易于在 FPGA 中部署的視覺加速庫,可在Vitis 環(huán)境中實(shí)施。其中 Vitis Vision 庫的 L1 目錄提供了在 Vitis HLS 層級部署的應(yīng)用實(shí)例設(shè)計(jì)。這個(gè)實(shí)例設(shè)計(jì)中 C-sim 的流程中需要調(diào)用 OpenCV 用于測試平臺(tái)功能,因此需要現(xiàn)有的OpenCV 安裝。

Vitis Vision庫:

https://github.com/Xilinx/Vitis_Libraries/tree/master/vision

為了適應(yīng)各種用戶環(huán)境,從2020.1版本開始,Xilinx 不再提供帶有 Vivado / Vitis 工具的OpenCV 的預(yù)安裝版本。盡管 Vitis 在綜合布局布線Vision庫的流程中不需要 OpenCV,但是運(yùn)行示例設(shè)計(jì)仿真是必需的。

本文使用 Vitis 2020.2 版本介紹了如何創(chuàng)建獨(dú)立的 Vitis HLS TCL 文件,用戶只要在將該 tcl腳本拷貝在 Vision Lirary 的實(shí)例目錄中,即可在命令行模式下跑完 Vitis_HLS C仿真,綜合,聯(lián)合仿真以及導(dǎo)出 IP 等全部流程。

Vision 的官方文檔中包含使用 Vitis HLS standalone 模式的教程,該信息位于以下位置:

https://github.com/Xilinx/Vitis_Libraries/blob/master/vision/docs/getting-started-with-hls.rst

https://xilinx.github.io/Vitis_Libraries/vision/2020.1/index.html#

要利用示例設(shè)計(jì)或在用戶測試平臺(tái)中引用 OpenCV 庫,必須執(zhí)行以下步驟:

-安裝 OpenCV 工具版本3.x

OpenCV 在Linux 的安裝和環(huán)境設(shè)置請參考附錄A, 在 Windows 環(huán)境下建議使用 Mingw 編譯Opencv 安裝包。

-設(shè)置環(huán)境變量以引用 OpenCV 安裝路徑

-下載 Vitis Version library

-創(chuàng)建 TCL 腳本并在 Vitis HLS 命令行執(zhí)行

注意:2020.1 Vitis Vision 庫已使用 OpenCV 庫的3.3版進(jìn)行了驗(yàn)證。比該版本更新的任何版本都可以使用,但是,版本4.x可能相對于3.x版本具有庫功能更改,可能需要修改示例設(shè)計(jì)測試平臺(tái)。因此,建議使用 OpenCV 3.x 版運(yùn)行示例設(shè)計(jì)。OpenCV 庫僅提供測試平臺(tái)功能,不是必需的,并且不會(huì)以任何方式影響 Vision 內(nèi)核的實(shí)現(xiàn)。

環(huán)境設(shè)置

Linux 環(huán)境變量設(shè)置要求:

source < path-to-Vitis-installation-directory >/settings64.shsource < part-to-XRT-installation-directory >/setup.shexport DEVICE=< path-to-platform-directory >/< platform >.xpfm

export OPENCV_INCLUDE=< path-to-opencv-include-folder >

export OPENCV_LIB=< path-to-opencv-lib-folder >

export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:< path-to-opencv-lib-folder>

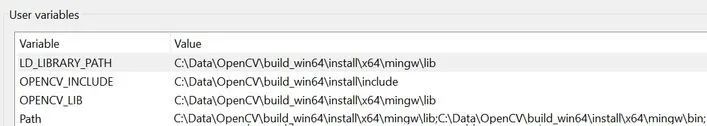

Windows 環(huán)境變量設(shè)置要求:

示例如下所示,并且每個(gè)用戶的設(shè)置會(huì)有所不同,具體取決于 OpenCV 和編譯器工具的安裝目錄。

注意:必須在用戶的環(huán)境中正確設(shè)置 LD_LIBRARY_PATH 動(dòng)態(tài)庫的搜索路徑環(huán)境變量和OpenCV PATH 信息,此腳本和 Vitis Vision 示例設(shè)計(jì)才能正常工作。此外,OpenCV 的包含庫和二進(jìn)制文件的路徑必須包含在系統(tǒng)的環(huán)境變量中。否則,將導(dǎo)致仿真期間庫包含錯(cuò)誤。

操作步驟

要運(yùn)行 Vitis HLS tcl 腳本,請執(zhí)行以下操作:

-將修改好的 tcl 腳本放在

-打開 Vitis HLS 命令行外殼并 cd

-運(yùn)行以下命令:vitis_hls -f run_hls_standalone.tcl

Vitis HLS TCL腳本詳細(xì)解釋

該AR提供了一個(gè) TCL 腳本,用于在 makefile 流之外運(yùn)行 L1 調(diào)整大小示例設(shè)計(jì)。該腳本基于Windows 環(huán)境。該腳本基于以下環(huán)境設(shè)置:

-OpenCV 版本3.4.11

Linux:

set XF_PROJ_ROOT"/home/vicky/Xilinx/Vitis_Libraries-master/vision"

set OPENCV_INCLUDE"/home/vicky/opencv/include"

set OPENCV_LIB"/home/vicky/opencv/lib"

Windows:

- OpenCV include directory /Data/OpenCV/build_win64/install/include

- OpenCV library directory /Data/OpenCV/build_win64/install/x64/mingw/lib

- Vitis Vision Directory /Data/Vitis_Libraries/Vitis_Libraries-master/vision/

TCL腳本文件包含以下部分,本文將逐一介紹

·代表 OpenCV 和項(xiàng)目環(huán)境的變量聲明

·項(xiàng)目創(chuàng)建命令

·使用 Vitis Vision 庫添加設(shè)計(jì)文件包括路徑

·使用 OpenCV 和 VitisVision 庫添加 Testbench 文件包括路徑

·使用 OpenCV 鏈接器參考進(jìn)行 C 仿真

·Vitis HLS IP 綜合

·具有 OpenCV 鏈接器參考的 RTL 協(xié)同仿真

· 導(dǎo)出IP

1

變量聲明:

變量聲明部分的第一部分聲明了一些變量,這些變量復(fù)制makefile流和該流生成的settings.tcl文件的環(huán)境變量。這些變量指向 Vitis Vision Includes,OpenCV 頭文件和 OpenCV預(yù)編譯的庫。這些位置可能會(huì)根據(jù)用戶系統(tǒng)的安裝路徑而有所不同。

設(shè)置 XF_PROJ_ROOT“ C:/ Data / Vitis_Libraries / Vitis_Libraries-master / vision”#Vitis Vision庫的包含目錄

設(shè)置 OPENCV_INCLUDE“ C:/ Data / OpenCV / build_win64 / install /include” #OpenCV頭文件目錄

設(shè)置 OPENCV_LIB“ C:/ Data / OpenCV / build_win64 / install / x64 /mingw / lib” #OpenCV 編譯的庫目錄

下一個(gè)變量聲明部分有助于創(chuàng)建 Vitis HLS 項(xiàng)目,并有助于使腳本可移植:

·設(shè)置 PROJ_DIR“ $ XF_PROJ_ROOT /L1 / examples / resize”

·設(shè)置 SOURCE_DIR“ $ PROJ_DIR /”

·設(shè)置 PROJ_NAME“ hls_example”

·設(shè)置 PROJ_TOP“ resize_accel”

·設(shè)置 SOLUTION_NAME“ sol1”

·設(shè)置 SOLUTION_PART“xcvu11p-flgb2104-1-e”

·設(shè)置 SOLUTION_CLKP 5

最后,最后一部分聲明變量,這些變量表示 HLS 引用和使用庫所需的引用路徑和標(biāo)志。這里我們發(fā)現(xiàn)在一個(gè)易用性高的腳本中,使用變量而不是代碼有助于理解如何使用這些選項(xiàng)。

設(shè)置 VISION_INC_FLAGS“ -I $XF_PROJ_ROOT / L1 / include -std = c ++ 0x”#Vitis Vision 包含路徑和 C ++ 11 設(shè)置

設(shè)置 OPENCV_INC_FLAGS“ -I $OPENCV_INCLUDE”#OpenCV 包含目錄引用

設(shè)置 OPENCV_LIB_FLAGS“ -L $OPENCV_LIB”#OpenCV 庫參考

注意:

在 Windows 中,庫引用必須包含版本號。本示例使用 OpenCV 3.4.11安裝。精確的包含格式將取決于用戶的安裝,并且可能與下面列出的格式不同。

設(shè)置 OPENCV_LIB_REF“ -lopencv_imgcodecs3411-lopencv_imgproc3411 -lopencv_core3411 -lopencv_highgui3411 -lopencv_flann3411-lopencv_features2d3411”

在 Linux include 語句不使用版本號,并給出如下:

設(shè)置 OPENCV_LIB_REF“-lopencv_imgcodecs -lopencv_imgproc -lopencv_core -lopencv_highgui -lopencv_flann-lopencv_features2d”

2

項(xiàng)目創(chuàng)建:

項(xiàng)目創(chuàng)建部分非常簡單,它會(huì)創(chuàng)建一個(gè)新的項(xiàng)目目錄和項(xiàng)目文件:

open_project -reset$PROJ_NAME

設(shè)計(jì)文件包括:

設(shè)計(jì)文件已添加到本節(jié)中的設(shè)計(jì)中。該命令:

-引用單個(gè)HLS內(nèi)核文件:add_files“ $ {PROJ_DIR} /xf_resize_accel.cpp”

-引用 Vision 庫和特定于項(xiàng)目的包含合成目錄:-cflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} /build

-引用了用于 C 仿真的Vision庫和特定于項(xiàng)目的包含目錄:-csimflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR}/ build”

完整的命令如下所示:

add_files“ $ {PROJ_DIR}/xf_resize_accel.cpp” -cflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} / build”-csimflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} / build”

Testbench 文件包括:

testbench 文件將在本節(jié)中添加到設(shè)計(jì)中。命令:

-引用 Test bench 文件:add_files -tb“ $ {PROJ_DIR} /xf_resize_tb.cpp”

-引用 Vision 庫和特定于項(xiàng)目的包含目錄:-cflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I $ {PROJ_DIR}/ build”

-引用 Vision 庫和特定于項(xiàng)目的 C 仿真目錄:-csimflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} /build”

請注意,在測試臺(tái)標(biāo)志和設(shè)計(jì)文件標(biāo)志中添加了$ {VISION_INC_FLAGS}變量。此設(shè)置引用OpenCV 包含文件。

完整的命令如下所示:

add_files -tb“ $ {PROJ_DIR}/xf_resize_tb.cpp” -cflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I ${PROJ_DIR} / build” -csimflags“ $ {OPENCV_INC_FLAGS} $ {PROSION_IN /建立”

3

項(xiàng)目設(shè)置:

現(xiàn)在已經(jīng)添加了所有需要的 C 源文件,執(zhí)行項(xiàng)目創(chuàng)建的最后一步。這些命令設(shè)置 HLS IP 的頂層函數(shù),并創(chuàng)建一個(gè)所需的項(xiàng)目solution。

set_top $ PROJ_TOP#設(shè)置HLS IP的頂級文件

open_solution -reset $SOLUTION_NAME#創(chuàng)建項(xiàng)目解決方案

set_part $ SOLUTION_PART#設(shè)置解決方案部分

create_clock -period $SOLUTION_CLKP#設(shè)置項(xiàng)目目標(biāo)時(shí)鐘周期

4

c-sim:

本部分通過將 HLS IP 和 Testbench 設(shè)計(jì)發(fā)送給編譯器進(jìn)行編譯和執(zhí)行,來執(zhí)行 HLS 流的 C仿真階段。此命令用于設(shè)置編譯器鏈接器標(biāo)志和 testbench 文件,以及:

-引用 OpenCV包含和預(yù)編譯的庫目錄:-ldflags“ -L $ {OPENCV_LIB} $ {OPENCV_LIB_REF}”

-包括用于驗(yàn)證測試臺(tái)的圖像作為主要功能的參數(shù):-argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

完整的命令如下所示:

csim_design -ldflags“ -L ${OPENCV_LIB} $ {OPENCV_LIB_REF}” -argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

5

C到RTL綜合:

本部分執(zhí)行 Vitis HLS C 到 RTL 合成階段。此階段不需要標(biāo)志或選項(xiàng)。

csynth_design

6

C/RTL協(xié)同仿真:

本部分在合成后執(zhí)行 Vitis HLS IP的 RTL 協(xié)同仿真。HLS 會(huì)自動(dòng)根據(jù) C test bench 生成RTLtestbench 進(jìn)行協(xié)同仿真,以下指令用于設(shè)置編譯器鏈接器標(biāo)志和 testbench 文件,以及:

-引用 OpenCV包含和預(yù)編譯的庫目錄:-ldflags“ -L $ {OPENCV_LIB} $ {OPENCV_LIB_REF}”

-包括用于驗(yàn)證測試平臺(tái)的圖像:-argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

完整的命令如下所示:

cosim_design -ldflags“ -L ${OPENCV_LIB} $ {OPENCV_LIB_REF}” -argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

7

導(dǎo)出IP:

Vitis HLS 流程的最后階段是設(shè)計(jì)的輸出。本示例導(dǎo)出RTL的設(shè)計(jì)并運(yùn)行 Vivado Synthesis,以獲取準(zhǔn)確的資源利用率和估計(jì)的時(shí)序結(jié)果。

export_design -flow syn -rtlverilog

注意:導(dǎo)出 RTL 的設(shè)計(jì)并運(yùn)行 Vivado Synthesis 進(jìn)行布局布線的過程需要在 Vivado 工具中先載入有效的 license

附件為在 Ubuntu 18.04 版本在 2020.2 上運(yùn)行成功的 tcl shell, 大家可以下載后稍作修改,根據(jù)本文流程在自己的環(huán)境中進(jìn)行實(shí)驗(yàn),有問題歡迎在本帖下方留言。

責(zé)任編輯:lq

-

變量

+關(guān)注

關(guān)注

0文章

614瀏覽量

28802 -

OpenCV

+關(guān)注

關(guān)注

32文章

642瀏覽量

42382 -

Vision

+關(guān)注

關(guān)注

1文章

201瀏覽量

18613

原文標(biāo)題:Vitis Vision | 利用Vitis HLS tcl shell 一鍵跑通視覺加速例程

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Sky5? GNSS L1 L5 雙頻低噪聲放大器前端模塊,帶后置濾波器 skyworksinc

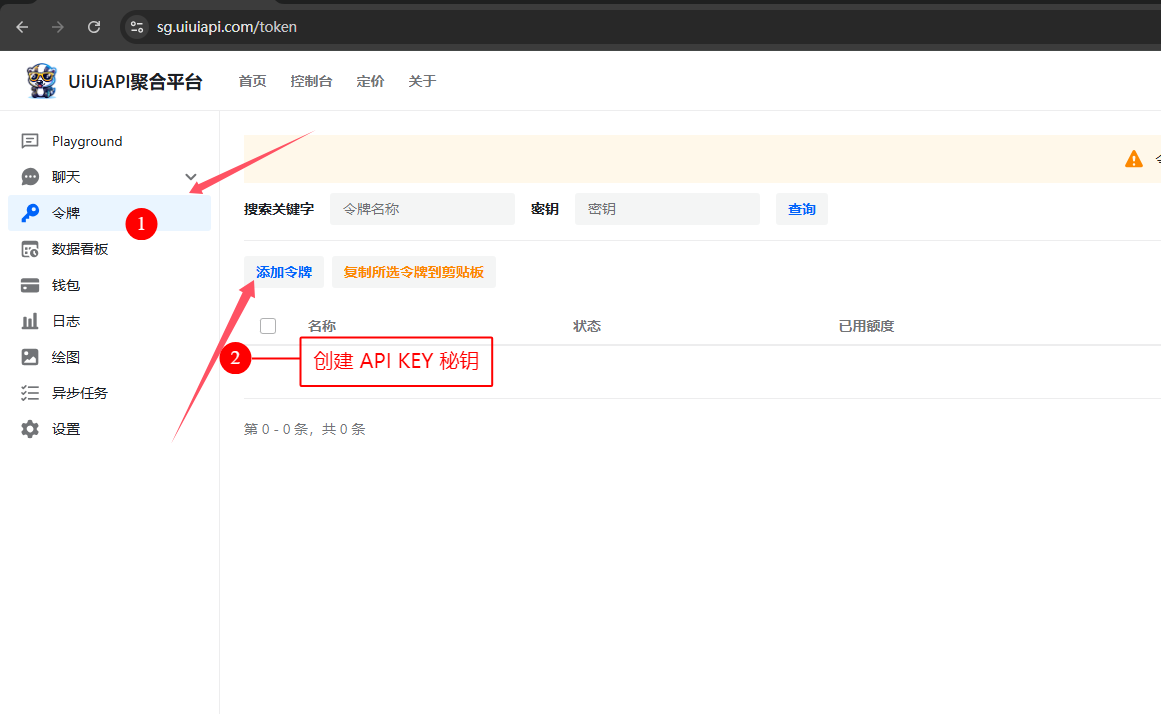

如何獲取 OpenAI API Key?API 獲取與代碼調(diào)用示例 (詳解教程)

Vivado HLS設(shè)計(jì)流程

ZU+RFSoC之RFDC API介紹和使用

企業(yè)級Claude API應(yīng)用方案!完整調(diào)用攻略來襲:帶你解鎖Claude 3.5/3.7大模型

助力AIoT應(yīng)用:在米爾FPGA開發(fā)板上實(shí)現(xiàn)Tiny YOLO V4

api驅(qū)動(dòng)的云服務(wù)是什么意思?

優(yōu)化 FPGA HLS 設(shè)計(jì)

國內(nèi)直聯(lián)使用ChatGPT 4.0 API Key使用和多模態(tài)GPT4o API調(diào)用開發(fā)教程!

BK1661 全集成的單芯片 L1 頻段 GNSS 解決方案

BK1662 單芯片L1/L5雙頻GNSS解決方案

BK1616P 全集成的單芯片 L1 頻段 GNSS 解決方案(高性價(jià)比FLASH版本)

AMD Vitis?設(shè)計(jì)工具中的Libraries新功能介紹

使用Vitis HLS工具在Standalone模式下調(diào)用Xilinx Vision Library L1 API

使用Vitis HLS工具在Standalone模式下調(diào)用Xilinx Vision Library L1 API

評論