近幾年,語音系統廣泛應用于嵌入式數字音頻產品,在MP3、手機等消費類電子產品中,人們對于這些個人終端的要求早已不限于單純通話和簡單的文字處理,高質量的音效是當前發展的重要趨勢。隨著嵌入式系統性能的提高,在ARM嵌入式系統中實現對各種音樂格式的解碼和播放已有可能。在語音功能需求的驅動下,越來越多的廠商紛紛推出了具有各種功能和標準的語音處理接口協議。IIS(Integrate Interface of Sound)總線是Philips公司提出的串行數字音頻總線協議。它是一種面向多媒體的音頻總線,專用于音頻設備之間的數據傳輸,為數字立體聲提供序列的連接至標準編解碼器。IIS總線處理聲音數據。其他信號(如控制信號)必須單獨傳輸。IIS總線一般具有4根信號線,包括串行數據輸入(IISDI)、串行數據輸出(IISD0)、左/右聲道選擇(IISLRCK)和串行數據時鐘(IISCLK),產生IISL2RCK和IISCLK的是主設備。

整個音頻系統的硬件部分主要是CPU和CODEC的連接與實現。Philips公司生產了一種支持IIS總線數據格式的音頻編解碼芯片UDA1341TS,采用位元流轉換技術進行信號處理,完成聲音信號的模數轉換,具有可編程增益放大器和數字自動增益控制器,由于其功能強大、低功耗、低電壓及具有DSP語音功能等特征,目前已廣泛應用于各種嵌入式語音系統中。同時作者有關于觸摸式語音菜單系統的實用新型專利授權正在審核當中。本文首先簡單介紹了S3C2410X中的IIS總線接口,并在此基礎上介紹了UDA1341TS語音芯片在觸摸式語音電子菜單系統中的軟硬件接口實現方法。

1 S3C2410X中的IIS總線接口

S3C2410X提供的IIS總線接口可以作為一個編碼解碼接口與外部8/16位的立體聲音解頻碼IC相連從而實現一個微唱片和便攜式應用。它支持IIS和MSBjustifled數據格式。IIS總線接口為FIFO隊列的訪問提供DMA傳輸模式來取代中斷,它可以同時發送和接收數據,也可以只發送或接收數據。

1.1 IIS總線特征

(1)1通道基于DMA的IIS總線用于音頻接口;

(2)每通道串行數據傳輸8/16位;

(3)128 B FIFO用于發送/接收;

(4)支持IIS格式和MSB驗證數據格式。

1.2 數據傳輸模式

ARM芯片內置的IIS總線接口可以讀取IIS總線上的數據,同時還可以為FIFO數據提供DMA傳輸,從而做到同時傳輸和接收數據。

S3C2410X的IIS接口有3種數據傳輸方式:

(1)正常傳輸模式:正常傳輸模式基于FIFO寄存器,該模式CPU通過輪詢方式訪問FIFO寄存器,通過IISCON寄存器的第7位控制FIFO。如果FIFO已滿,IISCON的第7位被設置為“O”,表示不能繼續傳輸數據;反之FIFO的第7位被設置為“1”,表示可以繼續傳輸數據。

(2)DMA模式:這種模式是一種外部設備控制方式,通過設置IISFCON寄存器可以使IIS接口工作在該模式下。它使用竊取總線控制權的方式使外部設備和RAM交換數據,從而提高系統的吞吐能力。在S3C2410X芯片中有4個通道的DMA控制器用于控制各種外部設備,其中IIS與其他串行外設共用2個橋聯DMA(BDMA)類型的通道。

(3)傳輸/接收模式:在這種模式下,IIS數據通過雙通道DMA同時接收和發送音頻數據。

1.3 信號線

信號線共5根:

(1)串行數據輸入(IISDI);

(2)串行數據輸出(IISDO);

(3)左/右聲道選擇(IISLRCK);

(4)串行數據時鐘(IISCLK);

(5)音頻系統主時鐘CODECLK。

2 支持IIS的語音控制芯片UDA1341TS的介紹

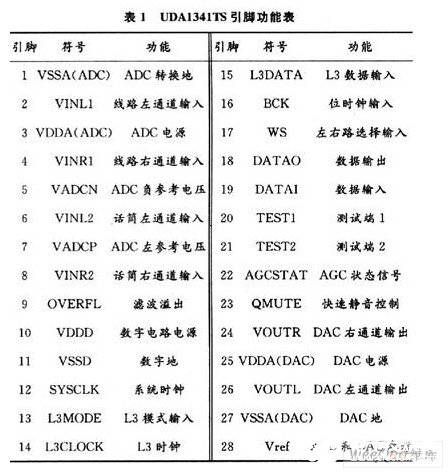

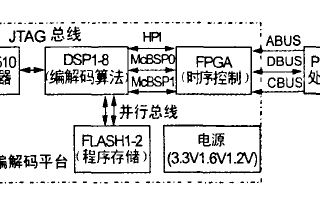

UDA1341TS是Philips公司的一款經濟型音頻CODEC,用于實現模擬音頻信號的采集(音頻AD)和數字音頻信號的模擬輸出(DA),并通過IIS數字音頻接口,實現音頻信號的數字化處理。具有3 V的低電壓、低功耗、高保真,寬動態范圍和低失真的高品質特性,大量應用于家庭袖珍多媒體立體聲音響設備,筆記本電腦、數字攝像機及計算機音頻信號處理設備中。其引腳圖如圖1所示,其引腳功能如表1所示。

2.1 UDA1341TS的主要特性

UDA1341TS主要特性如下:

(1)低功耗;

(2)3.0 V的電源電壓;

(3)256,384,512倍采樣頻率的系統時鐘;

(4)包含AGC的全部繼承的模擬前端;

(5)ADC增加了集成的模擬前端;

(6)ADC支持2 V(RMS值)輸入信號;

(7)具有為簡單電壓過載的檢測器;

(8)獨立的電源控制ADC和DAC;

(9)DAC不必須有后端濾波器;

(10)可通過L3總線管理其功能。

2.2 工作模式

雙通道立體聲模數轉換控制器有4種工作模式:

(1)ADCl輸入通道1工作方式(為線路輸入),輸入通道2關閉;

(2)ADC2輸入通道2工作方式(麥克風輸入),輸入通道1關閉,具有PGA和AGC控制特性;

(3)ADCl+ADC2混合工作方式,具有PGA和AGC控制特性;

(4)ADC1-ADC2混合工作方式。

2.3 L3控制特性

由微處理器與UDA1341TS芯片L3接口,完成下列控制功能:電源控制;芯片復位;數模、模數轉換的增益開關;數模、模數轉換的極性控制;倍速錄音控制;音量、高低音、靜音控制;麥克風靈敏度控制;可編程增益放大器控制,數字AGC自動增益控制。

由UDA1341TS的通道2組成可編程增益放大前置雙通道立體聲模數轉換控制電路,可編程的增益放大器(PGA),PGA通過L3接口進行設置,增益可設置為:-3 dB,0 dB,3 dB,9 dB,15 dB,21 dB或27 dB,通道2還具有數字自動增益控制AGC特性,數字式自動增益控制(AGC)范圍為60.5 dB,控制步長為0.5 dB。輸入通道1有0或6 dB放大增益選擇,通過L3接口進行控制,用這種方法輸入信號可達到1 V或2 V。

3 UDA1341TS在基于S3C2410X的觸摸式語音菜單系統中的應用

3.1 硬件連接方案

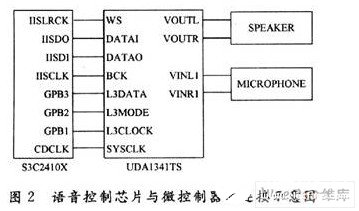

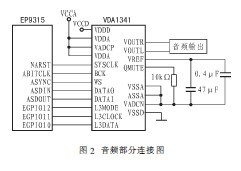

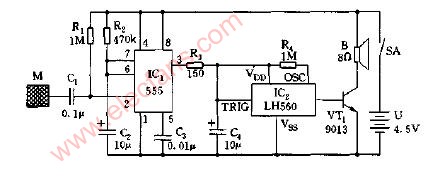

語音驅動芯片UDA1341TS和微控制器S3C2410X的連接如圖2所示。

S3C2410X的IIS總線信號與UDA1341TS的IIS信號直接相連。L3接口的引腳L3CLOCK,L3MODE和L3DATA分別連接到S3C2410X的GPBl,GPB2和GPB3通用數據輸出引腳。UDA1341TS對外提供兩組音頻信號輸入接口,每組包括左右2個聲道。

由于IIS總線只處理音頻數據,因此UDA1341TS還內置了用于傳輸控制信號的L3總線接口。L3接口相當于混音器控制接口,可以控制輸入/輸出音頻信號的低音及音量大小等。L3接口接在S3C2410X的3個通用GPIO輸入/輸出引腳上,利用這3個I/O口模擬L3總線的全部時序和協議。這里一定要注意L3總線的時鐘不是連續時鐘,它只在數據線上有數據時才發出8個周期的時鐘信號,其他情況下時鐘線始終保持高電平。

3.2 軟件設計方案

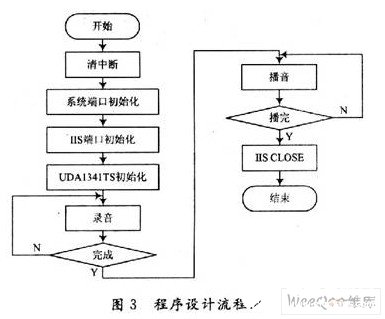

該數字語音模塊IIS經過正確的配置可以實現錄音、放音及循環放音等功能。因為音頻數據傳輸較簡單,本文主要介紹軟件設計的流程圖,流程圖如圖3所示。

4 結語

介紹了UDA1341TS在基于Samsung公司S3C2410X型微處理器的觸摸式語音電子菜單系統中的應用。該系統已經在基于S3C2410X的開發平臺上得到了實現,可以順利進行音頻的采集和播放,并取得了良好的效果。

責任編輯:gt

-

芯片

+關注

關注

459文章

52145瀏覽量

435854 -

嵌入式

+關注

關注

5138文章

19524瀏覽量

314692 -

總線

+關注

關注

10文章

2947瀏覽量

89325

發布評論請先 登錄

基于ARM7的嵌入式音頻處理系統的設計

基于ARM9的UDA1341驅動在Linux下移植方法

音頻編解碼芯片 VS1005最集成的音頻編解碼芯片

求推薦音頻芯片

采用FPGA實現音頻編解碼芯片接口

如何利用ARM9設計一種嵌入式音頻系統?

UDA1341TS pdf datasheet

基于ARM9處理器的嵌人式音頻系統設計

基于μC/OS-II的MP3文件播放系統設計

iis總線:基于IIS總線的嵌入式音頻系統設計

基于ARM9的音頻系統設計

DSP芯片實現語音編解碼技術的設計方案

基于音頻編解碼芯片UDA1341TS和IIS總線接口設計觸摸式語音菜單系統

基于音頻編解碼芯片UDA1341TS和IIS總線接口設計觸摸式語音菜單系統

評論