數(shù)字IC設(shè)計流程是每個IC從業(yè)者的第一課,無論你是做前端,后端,還是驗證,都需要對芯片的整個設(shè)計流程有個基本的了解。

本文章主要介紹以下三點內(nèi)容:

一. 數(shù)字IC設(shè)計的流程及每個流程需要做的工作

二. 每個流程涉及到的EDA工具

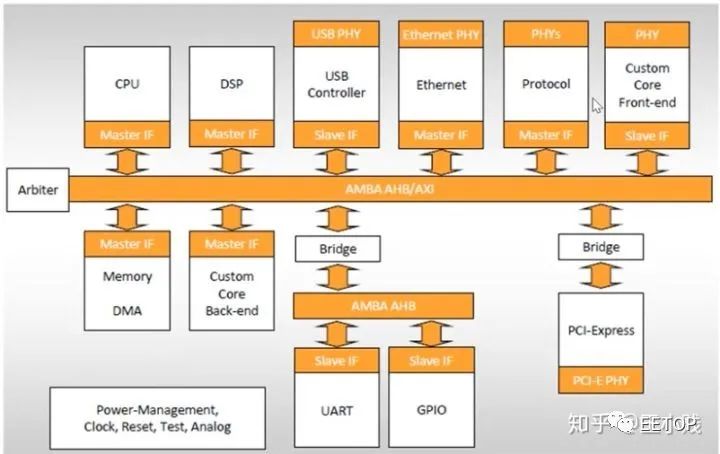

在介紹設(shè)計流程之前,我們先來看看數(shù)字芯片內(nèi)部的架構(gòu)。

如下圖所示,一個芯片是包含很多模塊的,有CPU,DSP,USB外設(shè),memory等,然后通過總線連接,1通常我們都是把各個模塊先設(shè)計好(IP team),然后再把他們集成到一起(SOC team).

一. 數(shù)字IC設(shè)計的流程

下面我用流程圖把設(shè)計的四大步以及要做的事情整理出來,主要分四大步:

1.確定項目需求

首先做一款芯片需要有市場,一般公司會先做市場調(diào)研,比如最近市面上比較火的人工智能芯片,物聯(lián)網(wǎng)芯片,5G芯片,需求量都比較大。有了市場的需求我們就可以設(shè)計芯片的spec了。先由架構(gòu)工程師來設(shè)計架構(gòu),確定芯片的功能,然后用算法進(jìn)行模擬仿真,最后得出一個可行的芯片設(shè)計方案。

有了芯片的spec,下一步就可以做RTL coding了。

2. 前端設(shè)計

RTL(register transfer level) 設(shè)計:利用硬件描述語言,如VHDL,Verilog,System Verilog, 對電路以寄存器之間的傳輸為基礎(chǔ)進(jìn)行描述。

功能仿真:通常是有DV工程師來完成這部分工作,通過搭建test bench, 對電路功能進(jìn)行驗證。

邏輯綜合:邏輯綜合是將電路的行為級描述,特別是RTL級描述轉(zhuǎn)化成為門級表達(dá)的過程。也就是將代碼翻譯成各種實際的元器件。

STA:(static timing analysis) 靜態(tài)時序分析,也就是套用特定的時序模型,針對特定電路分析其是否違反設(shè)計者給定的時序限制。

整個IC設(shè)計流程都是一個迭代的過程,每一步如果不能滿足要求,都要重復(fù)之前的過程,直至滿足要求為止,才能進(jìn)行下一步。

除了以上的步驟,前端設(shè)計還有一個步驟就是DFT,隨著芯片越來越大,DFT也就成為必不可少的一步。DFT通常要做scan chain, mbist ,ATPG等工作。

完成以上的工作后,就生成nestlist交給后端。

3. 后端設(shè)計

下圖給出了后端設(shè)計的流程及主要工作。

Place & Route一般由后端工程師來做,Physical Design Engineer.

后端里DRC就是要檢查設(shè)計規(guī)則是否符合芯片制造商的要求,這樣才能正確的生產(chǎn)芯片。

最后上一個全家福:

這里就不對每一步做具體的介紹了,因為內(nèi)容實在太多,每一點都可以挖掘的很深入。

后端完成工作后,最終會生成GDSII格式的文件,交由芯片制造商流片。

二. 每個流程使用的EDA 工具

數(shù)字邏輯仿真工具:

cadence: Incisive

synopsys: VCS

mentor: QuestaSim

數(shù)字邏輯綜合工具:

Cadence:Genus

Synopsis: design

數(shù)字后端設(shè)計工具:

1. 自動布局布線工具

Cadence: Innovus

Synopsis: IC Compiler

2.物理驗證工具

Mentor: Calibre

Synopsis: Hercules

Cadence: Diva/dracula

責(zé)任編輯:xj

原文標(biāo)題:干貨 | 數(shù)字IC設(shè)計全流程介紹

文章出處:【微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

435987 -

IC

+關(guān)注

關(guān)注

36文章

6093瀏覽量

178362 -

數(shù)字

+關(guān)注

關(guān)注

1文章

1698瀏覽量

51728

原文標(biāo)題:干貨 | 數(shù)字IC設(shè)計全流程介紹

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

數(shù)字IC設(shè)計:方法、技巧與實踐

西門子利用AI來縮小行業(yè)的IC驗證生產(chǎn)率差距

GaAs IC 1 位數(shù)字衰減器 skyworksinc

GaAs IC 1 位數(shù)字衰減器 15 dB LSB DC-2 GHz skyworksinc

NX CAD軟件:數(shù)字化工作流程解決方案(CAD工作流程)

工業(yè)流程:智慧工廠機(jī)械臂作業(yè)數(shù)字孿生 #機(jī)械臂 #數(shù)字孿生 #智慧工廠 #工業(yè)流程

數(shù)字設(shè)計ic芯片流程

TI電池監(jiān)控器IC的高級電量監(jiān)測器固件流程圖

【「數(shù)字IC設(shè)計入門」閱讀體驗】+ 數(shù)字IC設(shè)計流程

【「數(shù)字IC設(shè)計入門」閱讀體驗】+ 概觀

ic測試原理和設(shè)備教程的區(qū)別

名單公布!【書籍評測活動NO.40】數(shù)字IC設(shè)計入門,多角度透視芯片設(shè)計

VSP2560/62/66數(shù)字相機(jī)混合信號處理IC數(shù)據(jù)表

自動化IC封裝模擬分析工作流程

數(shù)字IC設(shè)計流程

數(shù)字IC設(shè)計流程

評論