DDR存儲器不僅迅速成為領先的技術,而且正成為存儲器設計中使用的唯一技術。因此,DDR系統(tǒng)在技術行業(yè)中有很高的需求。與原理圖和PCB設計軟??件集成在一起的高速仿真工具可以為設計人員提供廣泛的強大功能,以幫助完成整個DDR設計過程。從建立布局前約束到自動布線技術以及布局后驗證,這些工具消除了設計過程中的猜測,同時使工程團隊可以放心地知道他們的系統(tǒng)將按預期運行。

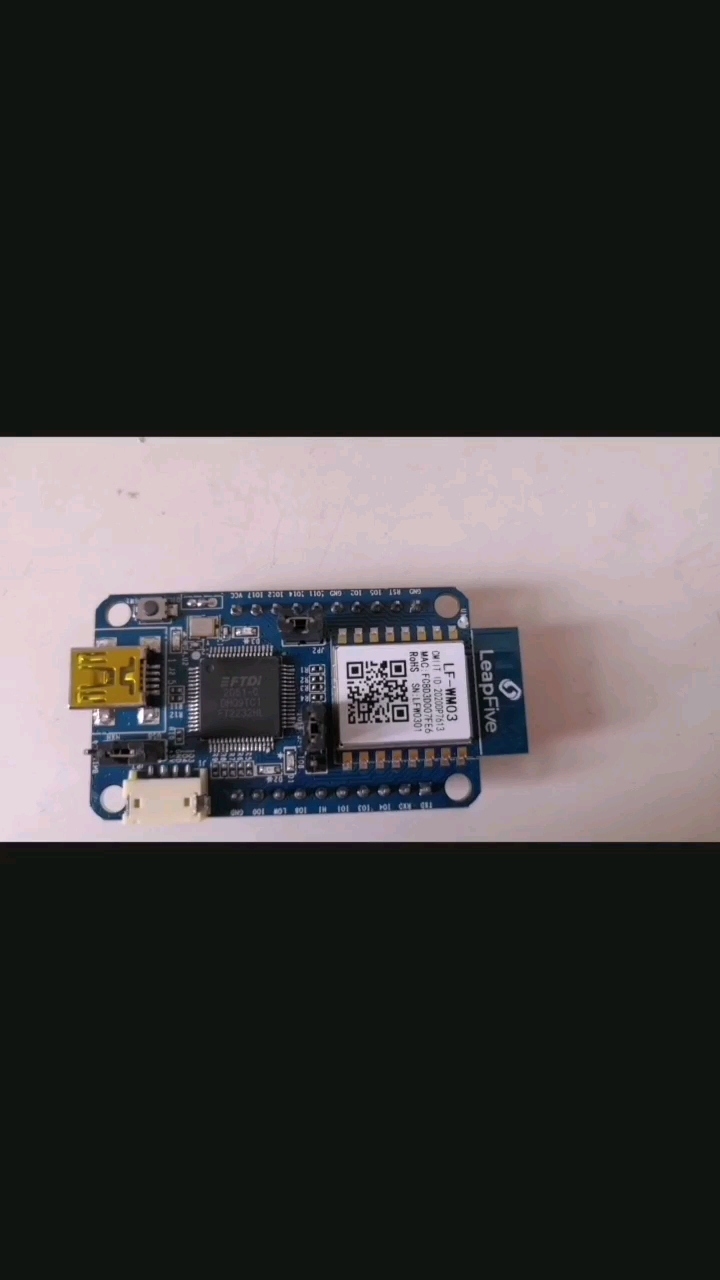

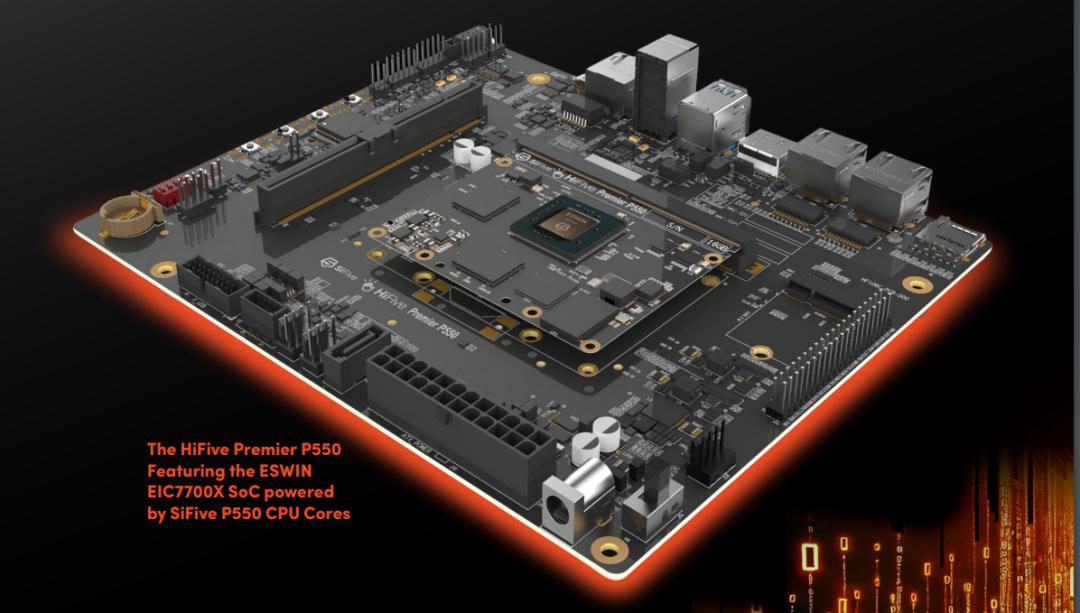

用于此DDR演示的設計是SiFive的HiFive Unleashed,基于RISC-V的開發(fā)板。除了其他一些接口和功能(圖1)之外,該板還具有8 GB的帶ECC的DDR4 DDR4。

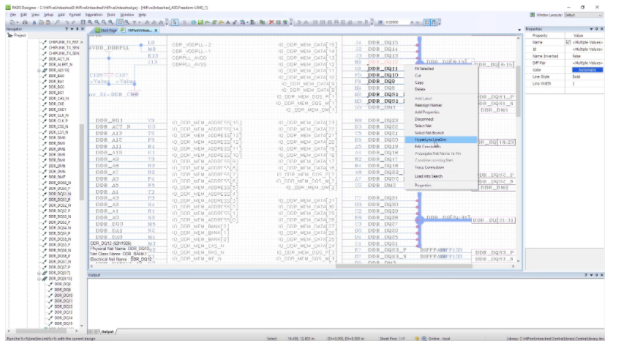

圖1:HiFive Unleashed開發(fā)板上可用的功能

在原理圖中,兩個差分選通網(wǎng)絡以及一條數(shù)據(jù)總線上的四個數(shù)據(jù)網(wǎng)絡可以直接輸出到HyperLynx LineSim進行預布局仿真(圖2)。借助HyperLynx DDR的擴展功能,使用組件IBIS模型模擬現(xiàn)實世界的場景,可使工程師在布局電路板之前確定并優(yōu)化傳輸線的性能。供應商通常為DDR控制器提供IBIS模型,為I / O行為建模提供DRAM組件。

圖2:可以從原理圖工具中將四個數(shù)據(jù)網(wǎng)和差分選通網(wǎng)導出到Linesim

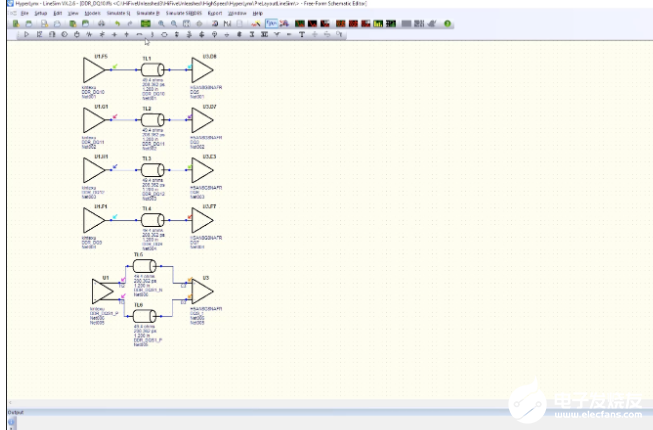

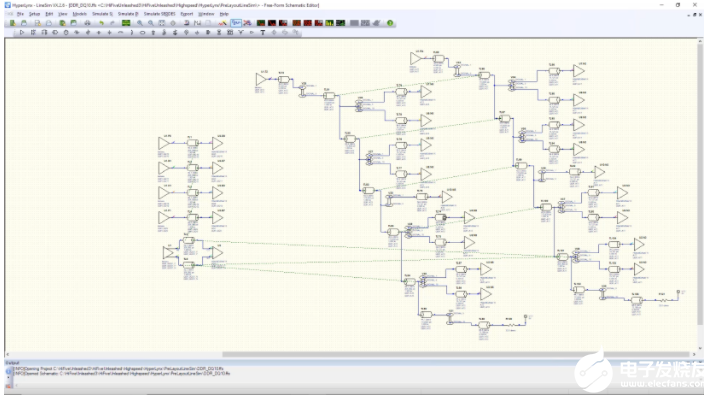

在LineSim中,數(shù)據(jù)和選通網(wǎng)絡的引腳和映射已從其原理圖符號中自動保留下來。然后,工程師除了可以從組件IBIS模型中獲得驅動強度和ODT值以外,還可以分配控制器的特定于引腳的緩沖區(qū)數(shù)據(jù)。在這種情況下,具有48歐姆終端值的中等驅動強度將可以達到預期的目的。一旦將引腳分配并指定為輸入或輸出,它們的LineSim符號將準確反映緩沖器的方向和引腳名稱(圖3)。

圖3:網(wǎng)絡及其關聯(lián)的緩沖區(qū)顯示在LineSim中

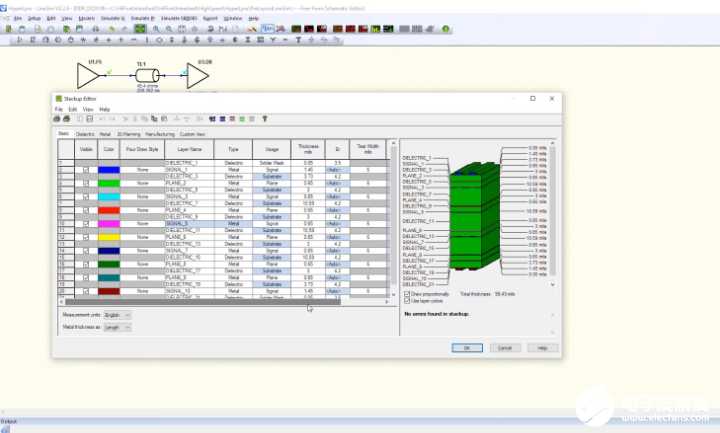

除材料的介電常數(shù)外,層厚度還會對電氣組件的功能產(chǎn)生重大影響,尤其是在高頻下。工程師能夠在HyperLynx內(nèi)部創(chuàng)建層堆疊并計算信號,平面和介電數(shù)據(jù)(圖4)。預先布局的DDR LineSim中的堆棧功能使您可以了解此信息將如何影響阻抗值和信號行為。

圖4:堆棧編輯器可以幫助確定初始堆棧數(shù)據(jù)

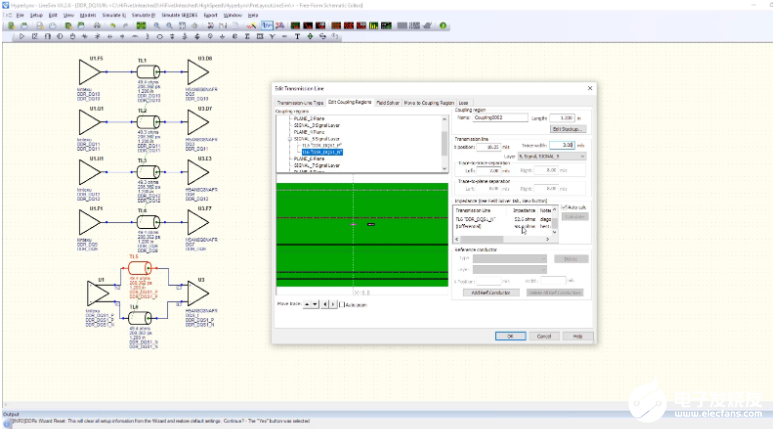

可以創(chuàng)建耦合區(qū)域,以幫助計劃和可視化潛在的信號放置和分組,以及確定走線阻抗和耦合距離。當對走線的長度,寬度和間距進行仿真掃描時,這些區(qū)域很有用,以便為布局約束找到可接受的參數(shù)。在此示例中,工程師創(chuàng)建了兩個耦合區(qū)域:一個用于數(shù)據(jù)網(wǎng)絡,另一個用于選通網(wǎng)絡。一旦將差分跡線添加到它們的耦合區(qū)域,就可以調整寬度和間距參數(shù)以微調值,同時確保滿足阻抗公差(圖5)。在此示例中,電路板將被密集地包裝,因此工程師將嘗試最小化走線寬度和間距,同時仍保持在100歐姆差分阻抗規(guī)格附近。

圖5:在LineSim中可視化了選定耦合區(qū)域的走線寬度和間距值

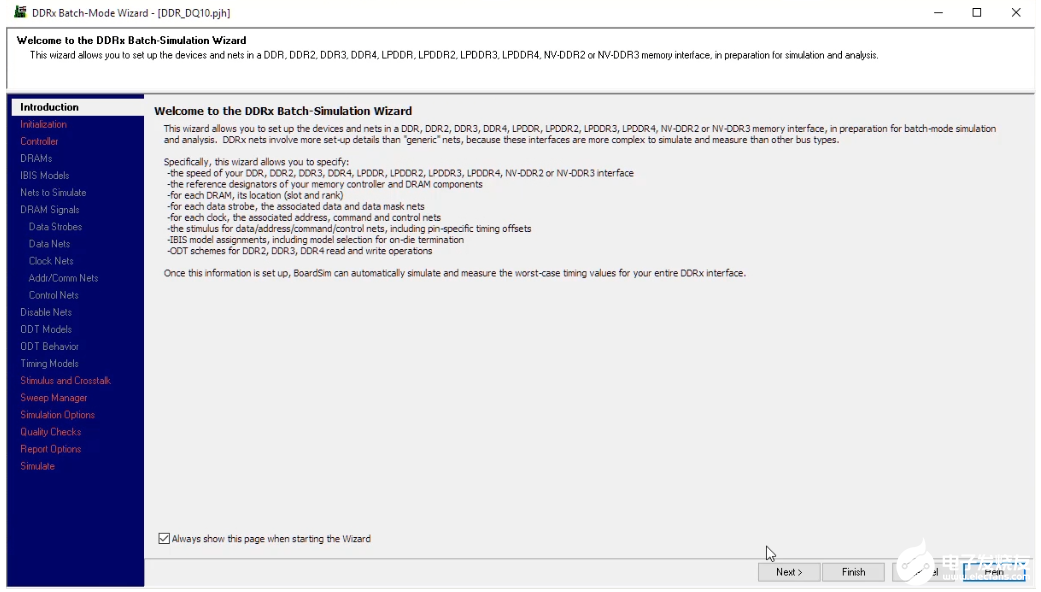

一旦分配了組件模型和耦合區(qū)域,就可以對網(wǎng)絡進行仿真了。DDRx向導將引導用戶逐步進行設置過程(圖6)。首先,必須在“初始化”頁面上指定DDR接口的類型以及數(shù)據(jù)速率。接下來,必須在“控制器”和“ DRAM”頁面上使用適當?shù)膮⒖紭擞泚矸峙淇刂破骱虳RAM設備。在選擇DRAM時,用戶還將指出插槽和等級的數(shù)量。插槽代表設計中存在的DIMM模塊的物理數(shù)量。由于此設計沒有可移動的DIMM模塊,因此插槽數(shù)為零。板上的板載DRAM模塊只有一個芯片,與一個等級相關。

圖6:DDRx向導將引導用戶逐步進行設置過程

由于工程師最初對確定物理網(wǎng)絡參數(shù)將如何影響數(shù)據(jù)網(wǎng)絡上的時序感興趣,因此將在“要模擬的網(wǎng)絡”頁面上僅選擇“數(shù)據(jù)時序”部分。如果需要,還可以提供用于模擬偏斜時序以及地址和命令時序的選項。幾乎所有DRAM供應商都遵循通用的命名約定,以遵守JEDEC標準。DDRx向導使用此標準約定自動確定“ DRAM Signals”頁面上的DDR內(nèi)存總線信號。僅需模擬一個數(shù)據(jù)網(wǎng)絡即可找到初始時序信息,因此可以在“禁用網(wǎng)絡”頁面上禁用除一個網(wǎng)絡以外的所有網(wǎng)絡。芯片上端接是內(nèi)置在DRAM硅中用于阻抗匹配的動態(tài)端接電阻。不同的ODT設置可能會對信號質量產(chǎn)生很大影響。在“ ODT模型”頁面上,可以選擇從IBIS模型得出的控制器和DRAM設備的動態(tài)ODT值。“激勵和串擾”頁面允許用戶控制在檢查SI損傷時運行多少個偽隨機序列。為了加快仿真運行時間,可以使用較小的位模式。為了獲得更準確的結果,可以使用更長的位模式。

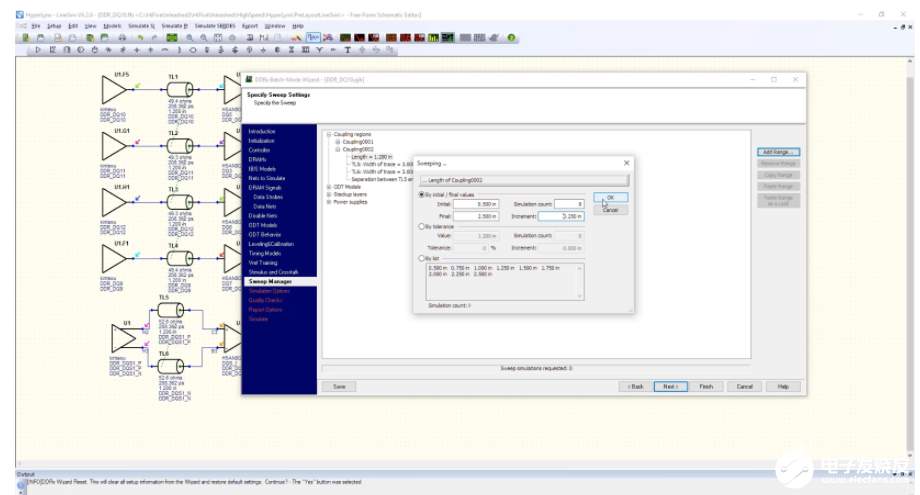

布局前仿真DDRx向導使用戶可以設置掃描,以確定一定范圍的值將如何影響信號行為。在這種情況下,工程師希望查看不同的選通網(wǎng)絡長度對數(shù)據(jù)信號質量的影響。在“掃描管理器”頁面上選擇差分耦合區(qū)域,可以指定長度范圍從半英寸到兩個半英寸(增量為四分之一英寸)(圖7)。這些值是根據(jù)大約1.2英寸的初步數(shù)據(jù)網(wǎng)長度選擇的。

圖7:可以設置掃描以模擬不同的頻閃網(wǎng)絡長度

模型角點可以提供有價值的洞察力,以了解IC在典型或極限參數(shù)值下的性能。通過僅在“模擬選項”頁面上選擇快速和慢速模型角,工程師可以洞悉信號在兩種極端情況下的性能。如果它們在這些條件下通過,則可以預期它們在典型情況下會通過。在其余的設置階段中,無需進行其他任何調整。啟動模擬后,模擬器將逐步執(zhí)行先前定義的9個掃描中的每個掃描。完成后,輸出HTML報告將顯示每次掃描的結果。紅色的單元格和通過次數(shù)代表失敗,綠色的單元格代表失敗。很顯然,在執(zhí)行寫命令期間,當差分閃光燈的長度小于四分之三英寸或大于四分之一或四分之一英寸時,就會發(fā)生故障(圖8)。這表明在數(shù)據(jù)網(wǎng)絡和選通網(wǎng)絡之間大約有正負半英寸的可接受長度差異。讀取命令模仿了相同的響應。

圖8:輸出的HTML報告顯示每次掃描是通過還是失敗

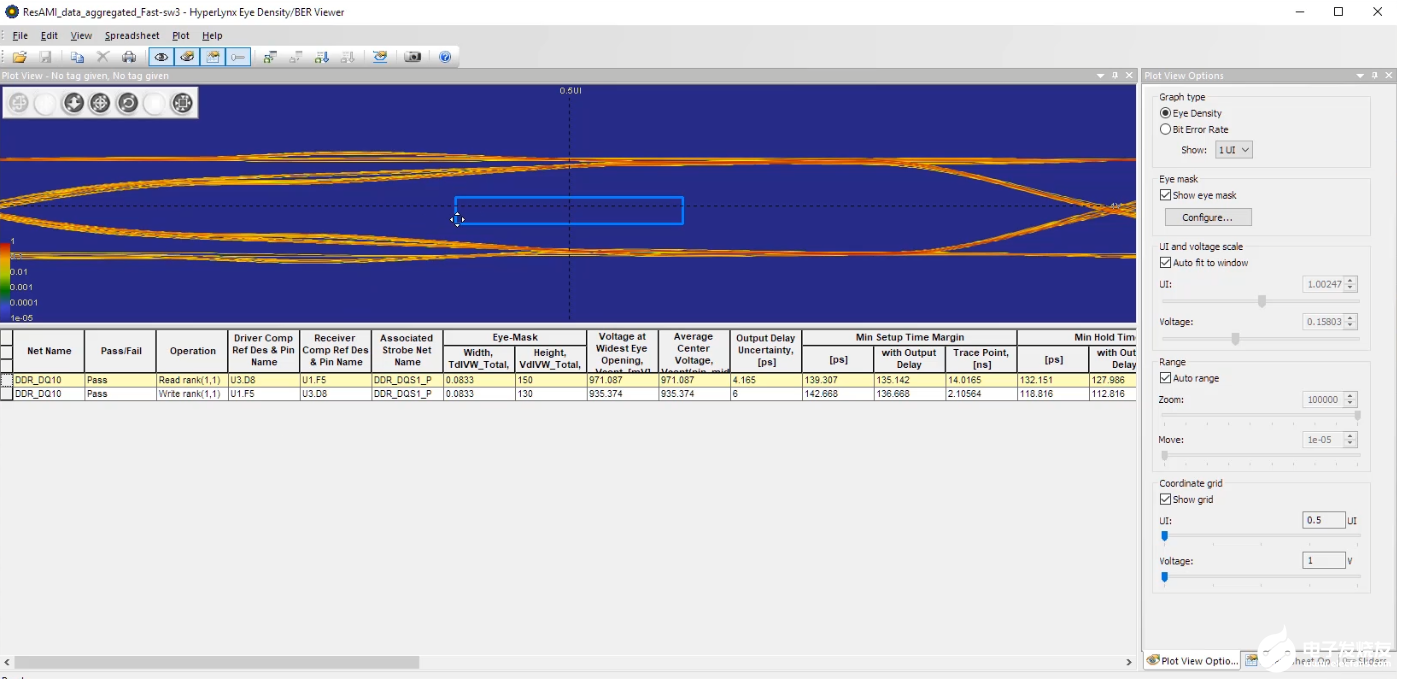

可以查看每個掃描的眼圖密度鏈接,以進行更好的比較。圖中的眼罩可解決DQS邊緣變化并自動放置。第一張圖(圖9)顯示了大于2英寸的差分閃光燈網(wǎng)長。第二張圖(圖10)顯示了在可接受的長度參數(shù)范圍內(nèi)的選通脈沖長度。這兩個圖顯示了通過和失敗之間的明顯區(qū)別。

圖9:眼圖顯示了差分頻閃燈網(wǎng)長大于2英寸時的信號并發(fā)癥

圖10:眼圖顯示了可接受的差分選通網(wǎng)絡長度,信號質量顯著提高

回到LineSim,工程師在原理圖中添加了兩個地址網(wǎng)(圖11)。此布局使用翻蓋技術以節(jié)省空間。通過放置用于從引腳到內(nèi)部走線層的層更改的過孔來解決此布線拓撲問題。還為駐留在同一內(nèi)層上的地址網(wǎng)的每個段(包括耦合到數(shù)據(jù)網(wǎng)的段)創(chuàng)建了耦合區(qū)域。

圖11:LineSim示意圖中所示的地址網(wǎng)和相關的耦合區(qū)域

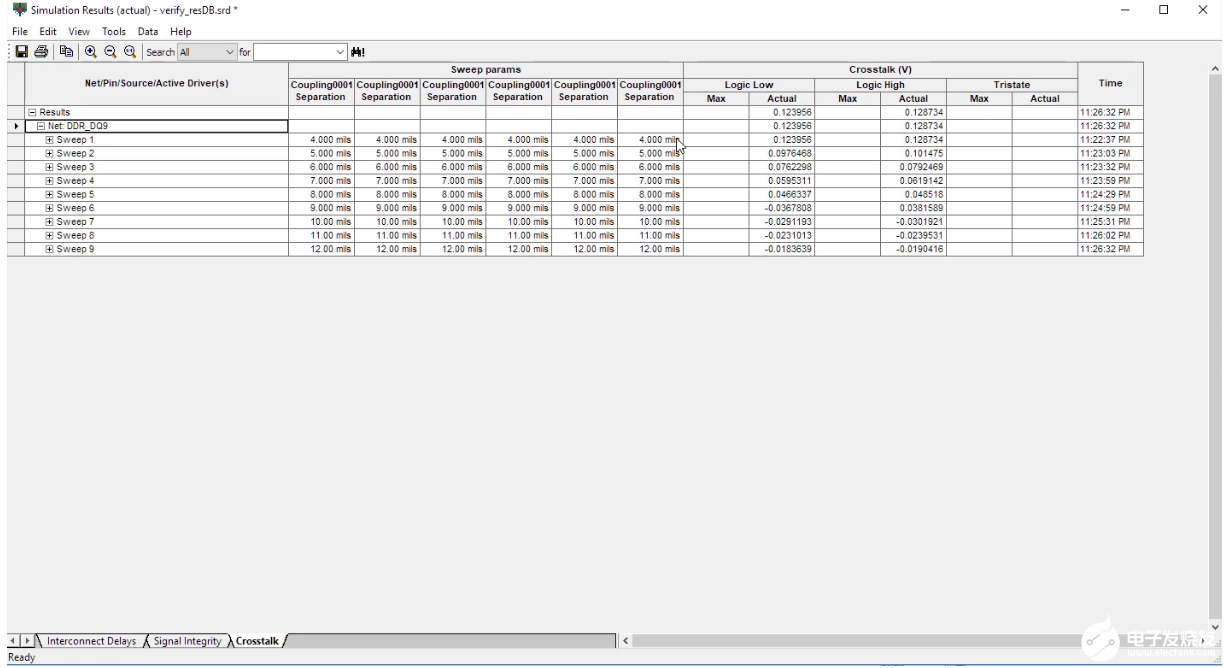

工程師將運行交互式仿真來查看從地址網(wǎng)絡施加到受害者數(shù)據(jù)網(wǎng)上的串擾,而不是運行另一個批處理仿真。要了解走線間距如何影響串擾結果,地址和數(shù)據(jù)網(wǎng)之間的寬度可以從4到12 mils范圍內(nèi)掃描。通過將數(shù)據(jù)位9識別為受害者,可以確定在該特定跡線上由附近的攻擊者網(wǎng)絡誘發(fā)的噪聲量。然后可以將這些發(fā)現(xiàn)合并到布局實踐中。一旦仿真完成,結果表明,當走線間距為4 mils時,串擾會達到最高水平(圖12)。但是,即使看到的最大串擾量也約為120 mV,這對于性能而言可能是可以接受的。如果電平開始達到150 mV以上,

圖12:串擾仿真結果表明,在4 mils的走線間距下發(fā)生了最高水平的串擾

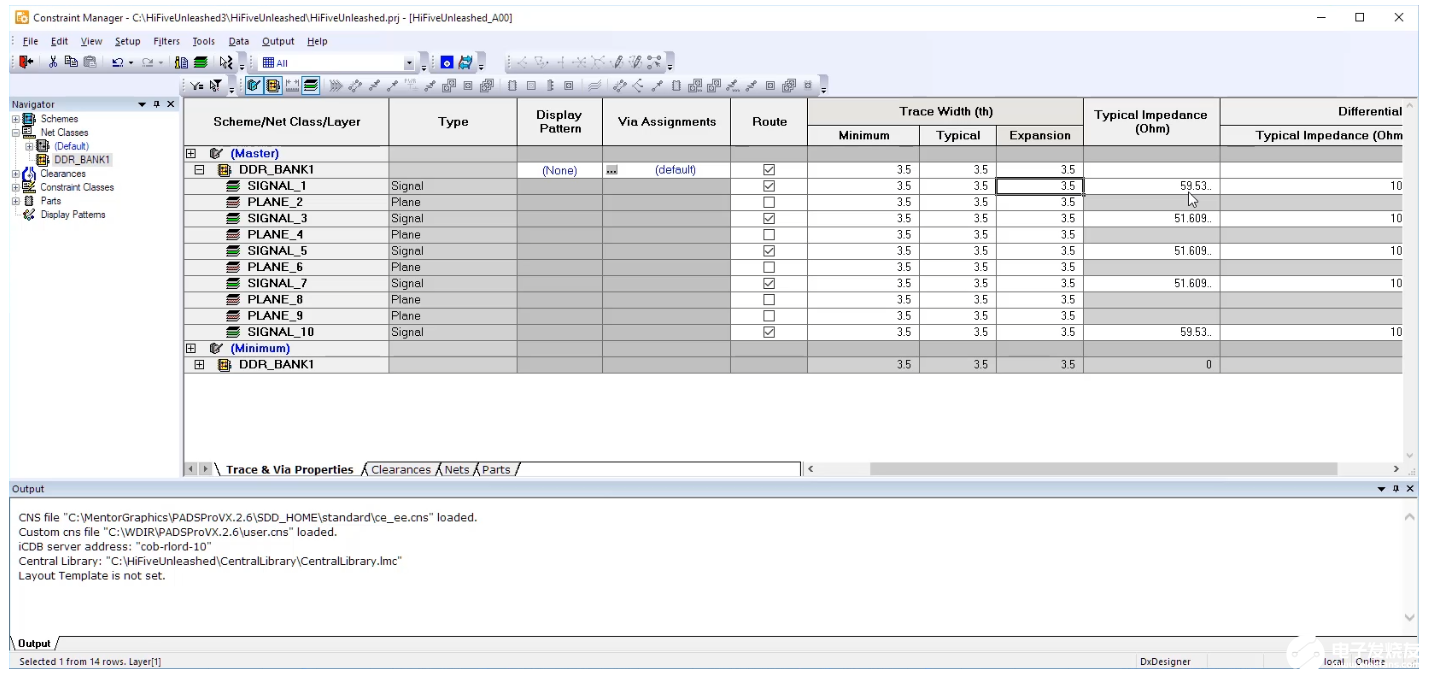

利用從運行這些布局前仿真中發(fā)現(xiàn)的信息,工程師可以使用原理圖工具內(nèi)部的約束管理器創(chuàng)建初始約束。約束管理器允許用戶創(chuàng)建網(wǎng)類,清除規(guī)則和約束類,以確保滿足物理布局和布線要求。可以創(chuàng)建網(wǎng)類以定義指定網(wǎng)上的寬度和間距要求。工程師創(chuàng)建了一個名為“ DDR_BANK1”的網(wǎng)絡類,其中包含單個DRAM模塊的數(shù)據(jù)和數(shù)據(jù)掩碼網(wǎng)絡。考慮到來自堆疊的電介質和阻抗信息,數(shù)據(jù)和數(shù)據(jù)屏蔽網(wǎng)的寬度應約為3.5密耳,以使單端阻抗值保持在50歐姆左右。輸入值后,約束管理器將根據(jù)走線寬度顯示近似阻抗值(圖13)。頂層和底層的阻抗將不再那么重要,因為位于這些層上的走線的唯一部分將是來自器件引腳的扇出。在“約束管理器”中定義了參數(shù)之后,布局工具將要求在放置和布線時遵守這些約束。可以從原理圖和布局工具中訪問“約束管理器”,以便工程師和布局專家之間進行簡單的協(xié)作,以及動態(tài)地進行動態(tài)編輯。在“約束管理器”中定義了參數(shù)之后,布局工具將要求在放置和布線時遵守這些約束。可以從原理圖和布局工具中訪問“約束管理器”,以便工程師和布局專家之間進行簡單的協(xié)作,以及動態(tài)地進行動態(tài)編輯。在“約束管理器”中定義了參數(shù)之后,布局工具將要求在放置和布線時遵守這些約束。可以從原理圖和布局工具中訪問“約束管理器”,以便工程師和布局專家之間進行簡單的協(xié)作,以及動態(tài)地進行動態(tài)編輯。

圖13:輸入跡線寬度值后,約束管理器將計算阻抗值

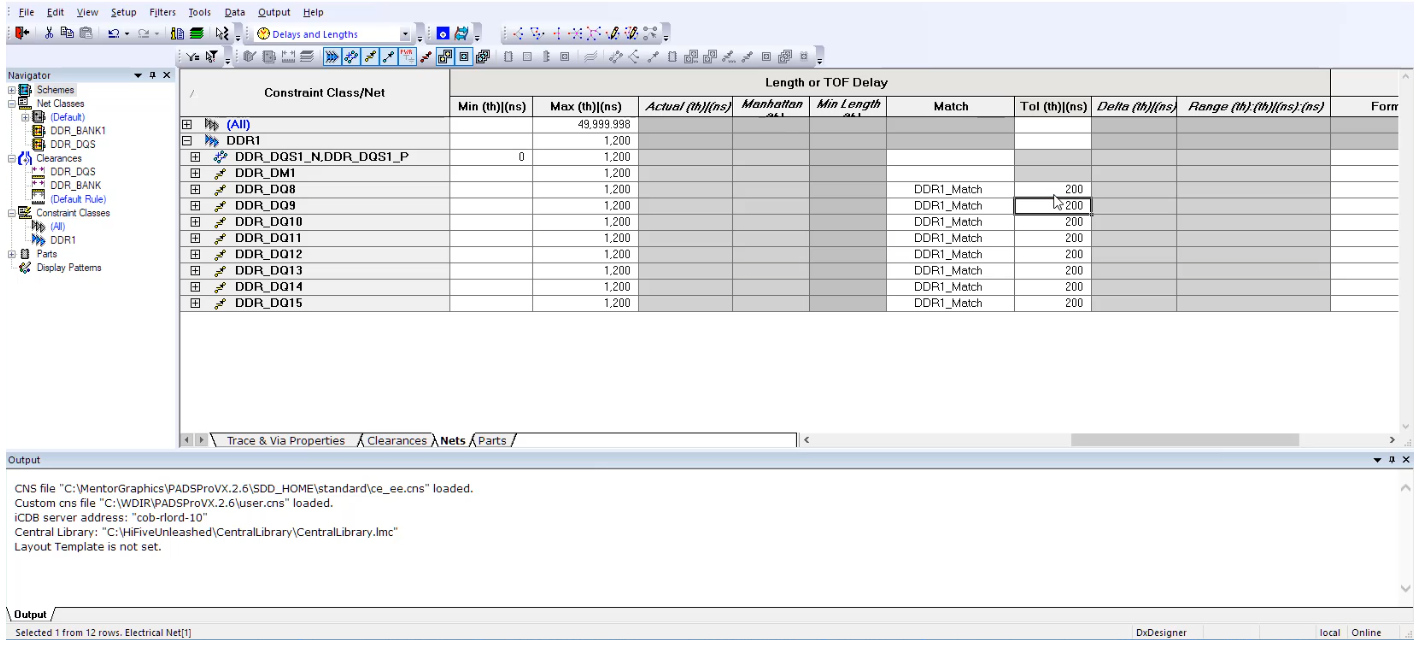

可以創(chuàng)建間隙規(guī)則來定義網(wǎng),組件和電路板對象之間的物理間隙約束。約束類允許用戶使用相同或單獨的網(wǎng)絡類分配將網(wǎng)絡分組在一起,同時還允許向每個網(wǎng)絡添加物理需求。除了針對DRAM的單個約束類別外,工程師還為數(shù)據(jù)和選通網(wǎng)絡創(chuàng)建了單獨的清除規(guī)則。約束類將包含數(shù)據(jù)庫的所有數(shù)據(jù),數(shù)據(jù)掩碼和選通網(wǎng)。一旦創(chuàng)建了約束類別,并向其中添加了適當?shù)木W(wǎng)絡,就可以為這些網(wǎng)絡定義許多物理參數(shù),包括阻抗容差和長度匹配要求。LineSim仿真表明,選通網(wǎng)絡必須在數(shù)據(jù)網(wǎng)絡的半英寸內(nèi)匹配,可以在約束類中定義。此外,工程師還希望確保數(shù)據(jù)和數(shù)據(jù)屏蔽網(wǎng)的長度在200密耳范圍內(nèi)匹配(圖14)。

圖14:數(shù)據(jù)和數(shù)據(jù)掩碼網(wǎng)的長度應在約束管理器中定義的200密耳范圍內(nèi)匹配

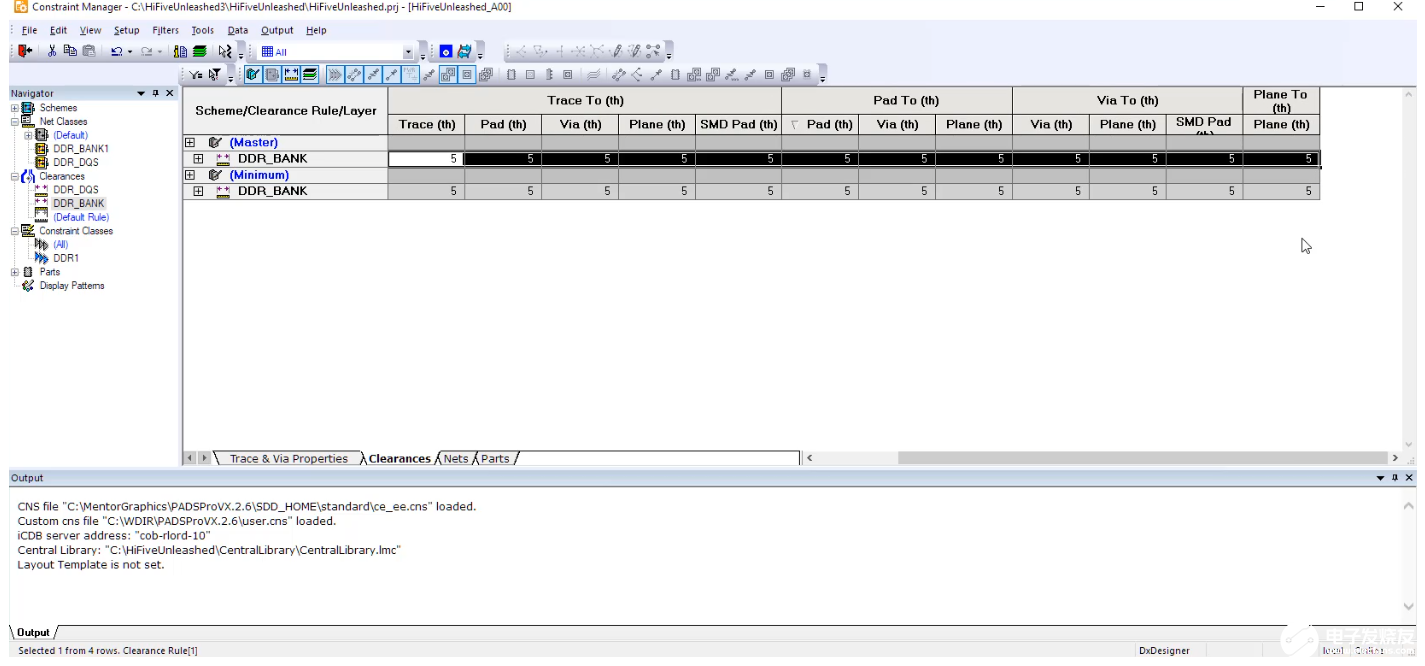

串擾仿真結果確定,即使數(shù)據(jù)網(wǎng)絡之間的間隔為4 mil,串擾水平也應在合理范圍內(nèi)。為了安全起見,工程師已將間隙規(guī)則要求設置為5 mil的間距閾值(圖15)。如果執(zhí)行額外的仿真計算,則還可在走線,焊盤和過孔之間應用更精確的間隙值。類別間許可矩陣允許用戶指定在凈類別之間適用的許可規(guī)則。

圖15:約束管理器中定義了5 mil的清除閾值

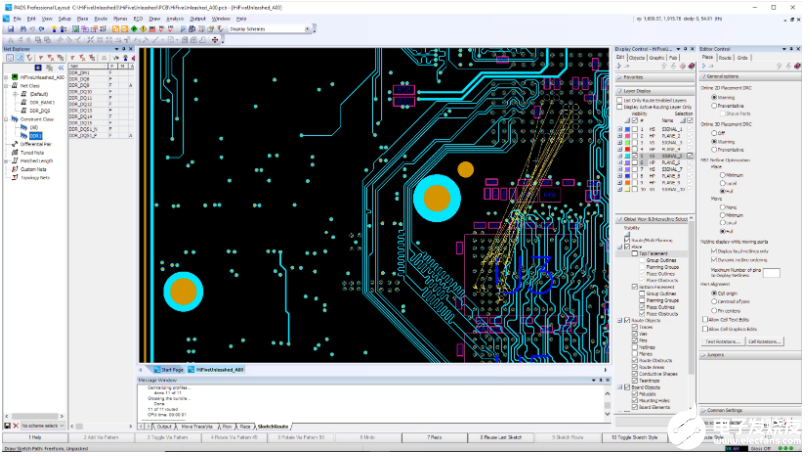

分配了初始的網(wǎng)絡約束后,設計人員已準備好為適當?shù)腄RAM路由走線。對于這種布局,SoC已放置在電路板的中間,而DRAM模塊位于其下方。每個組件的引腳的扇出已放置在頂層和底層。此DRAM的其余網(wǎng)段將在第5層上布線。在Net Explorer面板中,選擇DDR1約束類別將突出顯示網(wǎng)的引腳連接(圖16)。

圖16:在Net Explorer中選擇先前定義的DDR1約束類別將突出顯示引腳連接

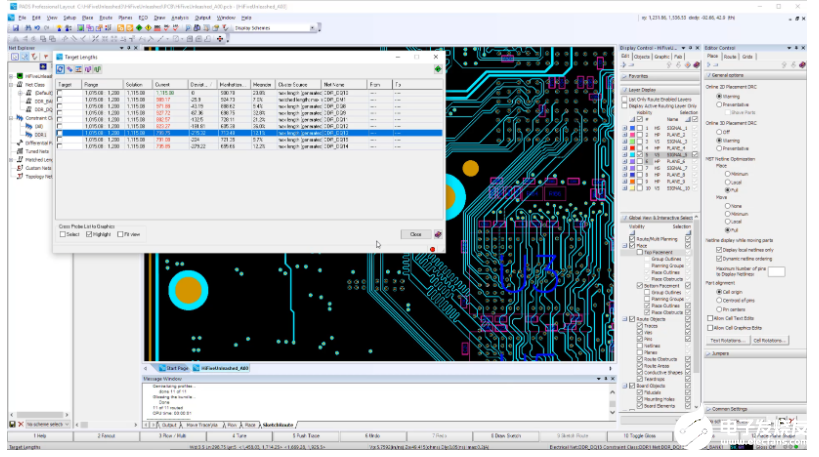

現(xiàn)在,設計人員可以簡單地選擇約束類,通過在鍵盤上按F8來打開草圖布線,用鼠標繪制其預期的布線路徑,該工具將自動對軌跡進行布線。右鍵單擊一個路由的數(shù)據(jù)網(wǎng)絡并選擇目標長度,可以輕松查看匹配組中每個跡線的實際長度值(圖17)。這有助于可視化跡線是否落在工程師先前設置的200密耳長度匹配約束范圍內(nèi)。顯然,走線長度不符合指定的要求,因此設計人員可以使用自動調整功能來快速蛇形匹配該組中的所有走線信號。

圖17:目標長度功能使用戶可以清楚地看到其走線長度是否已正確調整

正確路由接口后,用戶可以將布局直接導出到HyperLynx DDR以進行布局后分析。運行布局后分析的目的是驗證電路的正確功能和完整性。布局后仿真將考慮網(wǎng)和堆疊的實際長度和阻抗值,以及相鄰走線和組件的影響。加載HyperLynx BoardSim后(圖18),設計人員將首先啟用信號之間的耦合效果,信號與區(qū)域填充之間的耦合效果以及損耗的影響,以更準確地預測信號行為。借助布局后DDR分析,用戶可以運行交互式和批處理仿真,以全面了解系統(tǒng)功能。在交互式仿真過程中生成的示波器視圖將為單獨選擇的網(wǎng)絡提供真實的波形和值。對于此演示,將僅顯示批處理仿真。

圖18:HyperLynx BoardSim布局后工具視圖

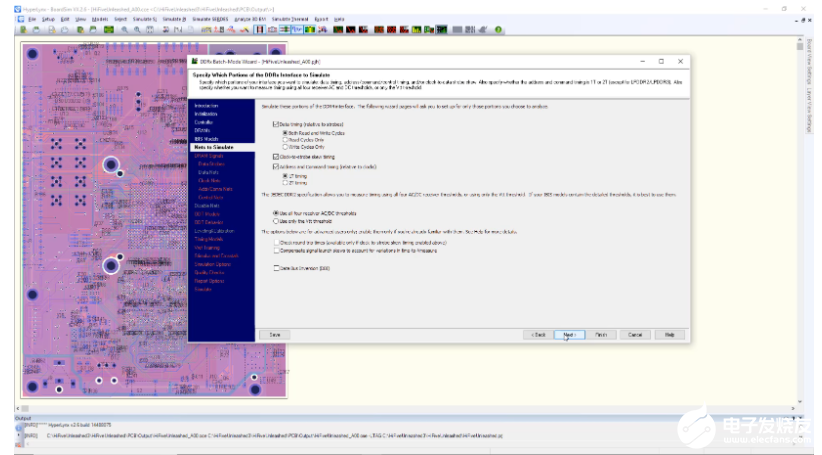

在布局后DDRx向導中,工程師最初將指定此接口為DDR4,每秒傳輸速率為2400兆兆。接下來,必須分配控制器組件。這次,當分配內(nèi)存組件時,工程師將選擇所有9個DRAM。由于整個DRAM接口均已布線,因此可以通過模擬數(shù)據(jù)的時序,時鐘到選通脈沖的偏斜以及地址和命令來收集重要的功能信息(圖19)。在這種情況下,感興趣的網(wǎng)絡是地址網(wǎng)絡以及剛剛路由的數(shù)據(jù)和選通信號之一。此處也將使用與布局前模擬相同的ODT設置,但是使用不同的ODT值運行多個模擬非常重要。

圖19:從布局后仿真中提取的時序信息可以為電路性能提供有價值的見解

存儲器控制器本身必須實時補償時鐘和選通信號之間的偏差。它通過在必要時添加適當?shù)难舆t(稱為寫平衡)來實現(xiàn)此目的。該向導的DDRx可以選擇“三通一平及校準”頁面上的復選框,當模擬過程中占到寫平衡。默認的DRAM時序模型符合JEDEC,但控制器模型應特定于設計的控制器設備。時序模型向導可以從“時序模型”頁面啟動,該頁面用于基于供應商時序參數(shù)設置和創(chuàng)建自定義時序模型。同時模擬快速和慢速模型拐角可提供最極端情況下的性能信息。HyperLynx DDR提供的自定義級別允許用戶創(chuàng)建高度針對設計的參數(shù)和限制,

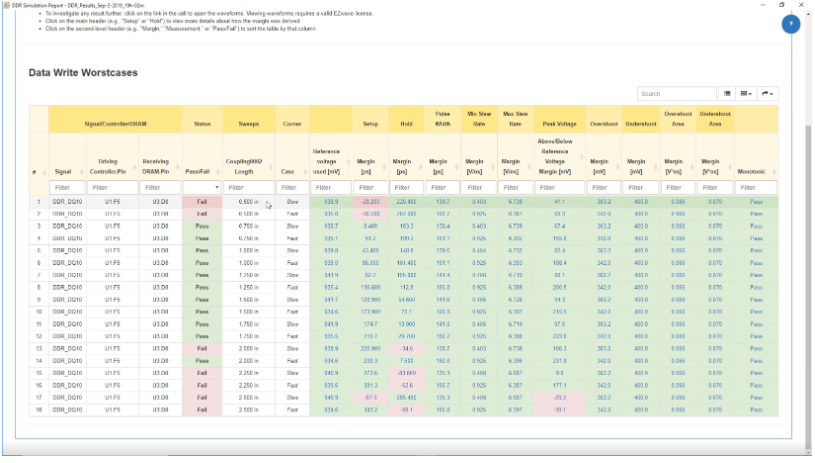

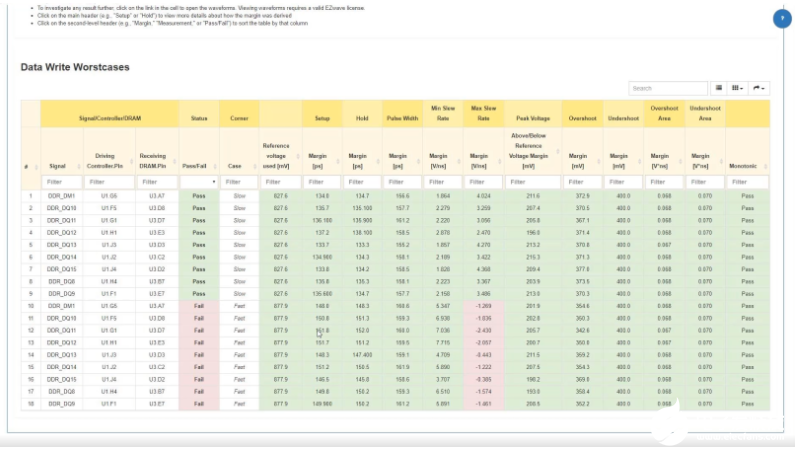

仿真完成后,HTML報告表明對于慢速模型拐角情況,所有網(wǎng)絡都通過了數(shù)據(jù)寫入命令,但是快速模型拐角情況沒有達到最大擺率裕度(圖20)。可能需要對這些錯誤進行進一步調查,并進行其他模擬。HTML報告中的每個結果均包含一個超鏈接,該超鏈接將打開該實例的EZwave示波器視圖。

圖20:HTML仿真報告顯示,快速模型拐角情況沒有達到最大擺率裕度

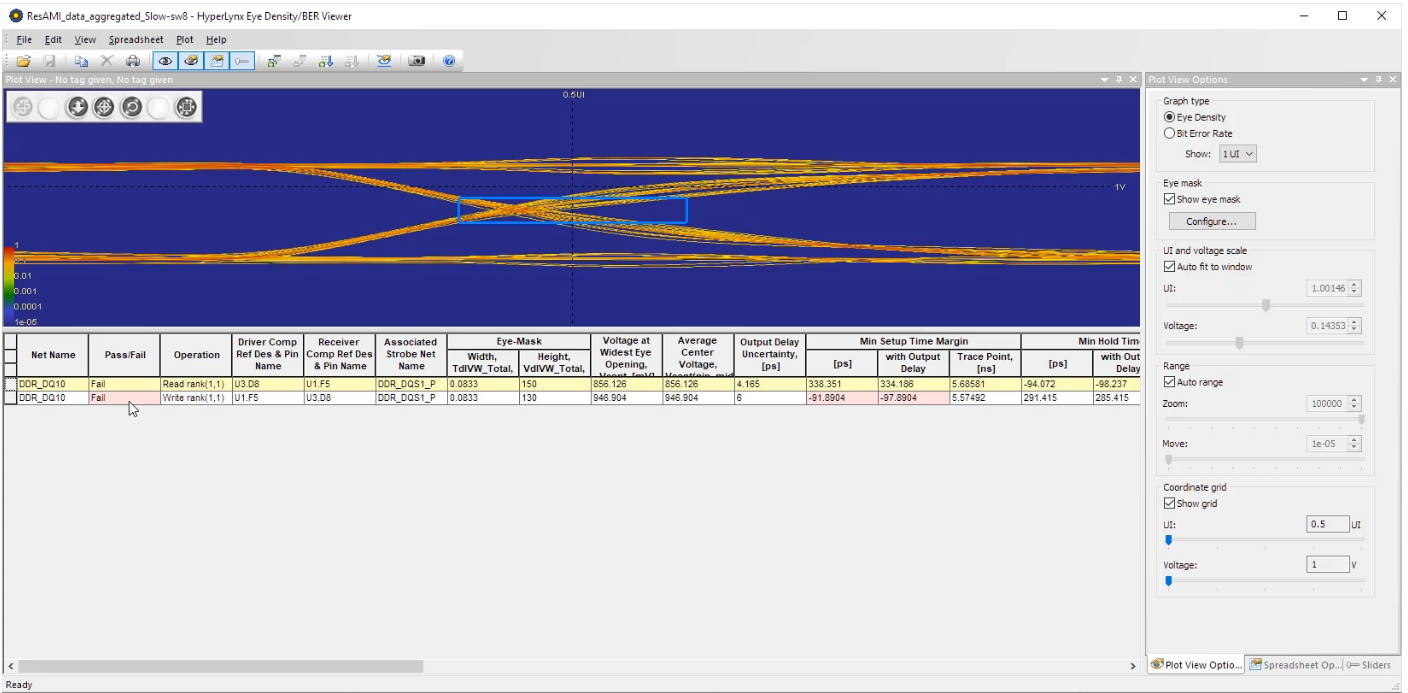

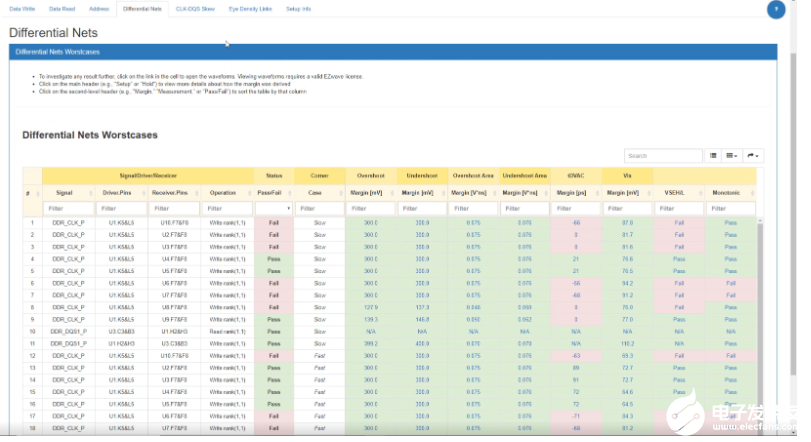

“差分網(wǎng)絡”選項卡顯示了在多條跡線上發(fā)生的許多錯誤,可能需要進一步關注和研究(圖21)。由于在控制器上啟用了寫入均衡選項,因此可以滿足所有偏斜裕量。眼密度鏈接頁面允許進一步調查和可視化每個模擬結果。

圖21:“差分網(wǎng)絡”選項卡顯示了許多錯誤

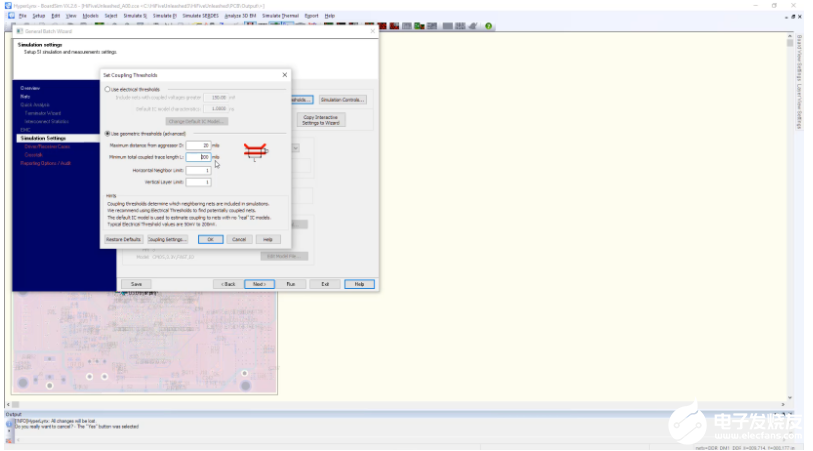

對于本演示的最后部分,將使用常規(guī)批處理向導僅模擬數(shù)據(jù)和數(shù)據(jù)掩碼網(wǎng)絡上的串擾效應。僅模擬快速模型角點將說明大部分串擾都會發(fā)生的情況。然后,工程師將自定義耦合閾值,以具有緊密的參數(shù),與攻擊者的最大距離為20密耳,最小耦合跡線長度為200密耳(圖22)。最后,每個網(wǎng)絡上允許的最大串擾水平將指定為50 mV。

圖22:可以根據(jù)特定設計要求定制耦合閾值

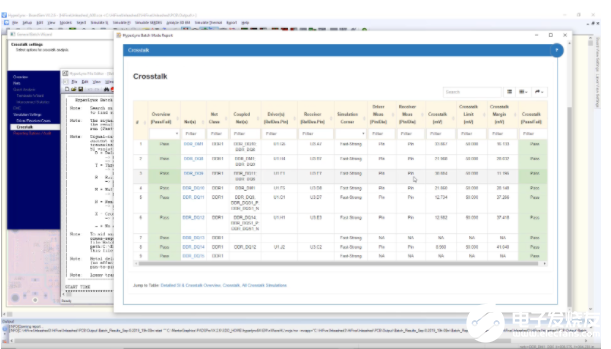

一旦模擬完成并顯示HTML報告,工程師就可以安全地確定數(shù)據(jù)網(wǎng)不會成為無法接受的串擾的犧牲品。任何網(wǎng)絡上的最大串擾都在40 mV以下(圖23),仍遠低于所確定的50 mV閾值。

圖23:沒有一個網(wǎng)絡超過50 mV的串擾閾值

HyperLynx DDR中提供的強大功能使工程師能夠在設計過程的所有階段可視化現(xiàn)實世界中的性能障礙。借助這項技術,可以捕捉和反轉信號,并在發(fā)生嚴重信號完整性之前就完全避免了它們的發(fā)生。借助集成的仿真和設計工具,用戶可以消除DDR設計過程中的麻煩,同時消除了復雜的信號完整性問題并避免了昂貴的電路板重新設計。

編輯:hfy

-

DDR存儲器

+關注

關注

0文章

8瀏覽量

7885 -

RISC-V

+關注

關注

46文章

2477瀏覽量

48229

發(fā)布評論請先 登錄

什么是RISC-V?解讀RISC-V工具鏈設置和開發(fā)板編程

risc-v開發(fā)板那種比較好 高性能RISC-V開發(fā)板BeagleV-Ahead評測

RISC-V中***會子活動之一:基于RISC-V的鴻蒙開發(fā)板設計

【RISC-V專題】芯昇科技RISC-V生態(tài)開發(fā)板首發(fā)試用

【RISC-V專題】御芯微UCM108E開發(fā)板首發(fā)試用

基于DK-START-GW2A18開發(fā)板的RISC-V圖片演示系統(tǒng)

什么是RISC-V?如何找到合適的開發(fā)板

使用Eclipse和MCUXpresso IDE調試RV32M1-VEGA RISC-V開發(fā)板

開發(fā)者看這里!免費申請RISC-V生態(tài)開發(fā)板

BeagleV-Ahead | 全球首款高性能RISC-V開發(fā)板

RISC-V生態(tài)開發(fā)板CM32M433R-START原理圖

SiFive 推出高性能 Risc-V CPU 開發(fā)板 HiFive Premier P550

基于RISC-V開發(fā)板的DDR演示的設計方案

基于RISC-V開發(fā)板的DDR演示的設計方案

評論