隨著消費電子設備尺寸的不斷減小和復雜性的增加,強烈要求將越來越多的功能集成到單個芯片上。進行這種集成的原因很多。電路板設計變得更簡單,需要放置的設備更少,布線的互連更少。

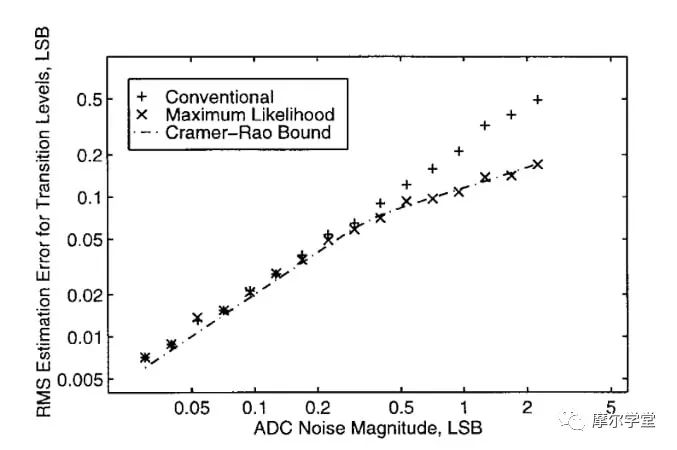

在純數字環境中,集成以驚人的速度發展。在過去的十年中,數字集成已從根本上改變了DVD播放器,AVR和MP3播放器等消費類電子產品的系統設計。消費者已經重復了更快,更便宜和更小的消費電子設備的好處。當人們試圖合并信號路徑的模擬和數字部分時,這種集成路徑變得更加困難。在許多消費電子應用中,大型數字片上系統(SoC)IC已開始包含此模擬功能。這里的挑戰是極端的。盡管進行了許多工藝改進,例如深n阱技術,該技術將模擬電路與數字核隔離開來,設計人員最終試圖將高性能模擬轉換器與快速且嘈雜的數字信號處理器(DSP)放置在同一基板上。迄今為止,很少有設備能夠將其真正的高性能轉換器和高速DSP推向市場。為了解決這一挑戰,有必要研究對芯片上數字電路的干擾較不敏感的新型轉換器架構。

傳統的開關電容架構

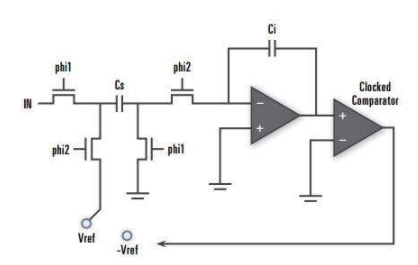

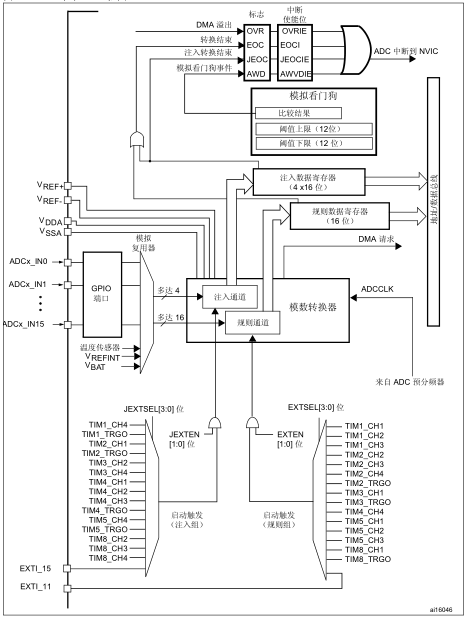

大多數現代音頻轉換器都采用開關電容架構。圖1給出了簡化的開關電容式模數轉換器(ADC)的框圖。

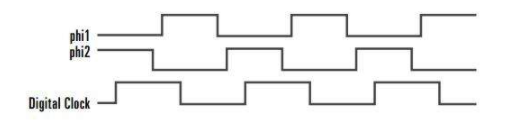

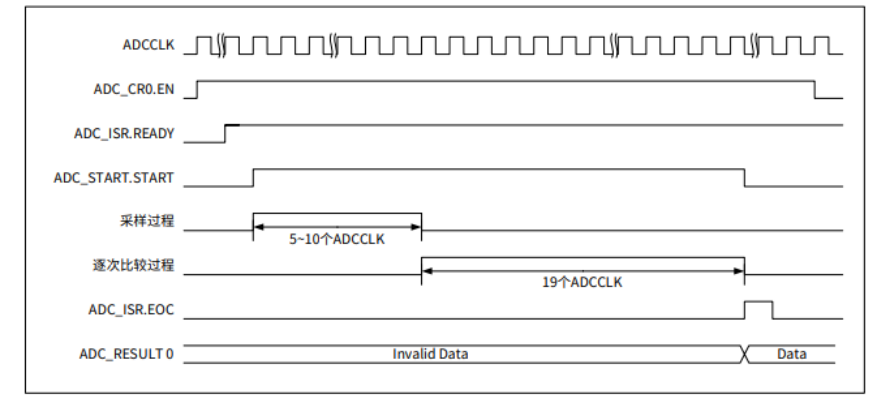

開關電容器DAC的架構相似,盡管隨后的討論將重點放在ADC上,但分析也適用于DAC。在ADC中,將輸入音頻信號采樣到采樣電容器tex_C_ {s} [/ tex],然后傳輸到積分電容器tex(C_ {i})[/ tex]。使用兩相時鐘,其中輸入在phi1上采樣,并與phi2上的反饋信號±Vref一起傳輸到積分電容器。該架構的關鍵時間是phi1開關斷開,而phi2開關閉合。這是采樣輸入信號并將其提供給積分器的時間點。輸入或地面上的任何噪聲都將被采樣并出現在ADC輸出中。轉換器設計中的一種常用技術是對數字時鐘計時,以使其在采樣事件之后發生。

數字時鐘的邊緣將始終將與信號相關的噪聲注入到基板中,該基板將找到通往參考節點或采樣電容器接地節點的路徑。只要在采樣事件之后發生數字邊沿,就不會在ADC輸入端采樣到任何噪聲。

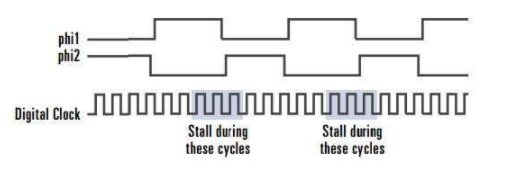

在獨立轉換器中,這種噪聲管理易于實現。所有時鐘通常都來自單一來源,因此確保模擬和數字時鐘之間的時序關系非常簡單。即使數字時鐘比模擬時鐘快,也很容易找到安全區域來放置這些數字邊沿。在一個復雜的DSP上,異步數字內核的運行速度可能比轉換器要快得多,這個問題要困難得多。圖3顯示了問題的性質。

無法保證采樣事件的安全時間。在某些解決方案中,DSP只是停頓了多個周期以創建一個安全的采樣事件,如圖3中的陰影框所示。這可以有效地消除DSP與轉換器之間的耦合,但這樣做的代價是MIPS。假設典型的6.144 MHz轉換器時鐘和98.3 MHz DSP時鐘(轉換器時鐘的16倍)。如果選擇使處理器停頓3個時鐘,以確保采樣事件周圍有一定余量,那么這將消耗芯片處理能力的近20%。

編輯:hfy

-

模數轉換器

+關注

關注

26文章

3294瀏覽量

127938 -

開關電容

+關注

關注

0文章

103瀏覽量

18682 -

數字信號處理器

+關注

關注

5文章

478瀏覽量

27726 -

音頻轉換器

+關注

關注

0文章

24瀏覽量

45389

發布評論請先 登錄

ADC模數轉換器介紹

開關電容式模數轉換器(ADC)的框圖介紹

開關電容式模數轉換器(ADC)的框圖介紹

評論