隨著便攜式電子產(chǎn)品、“智能設(shè)備”和汽車電子產(chǎn)品的普及,IC 中嵌入模擬功能的需求也在不斷增加。這推動(dòng)了對(duì)特定模擬技術(shù)的需求,這些技術(shù)在整個(gè)半導(dǎo)體市場(chǎng)中所占的比例越來越大。

通過一些簡(jiǎn)化,模擬技術(shù)可以分為三個(gè)主要類別:

高功率 BiCMOS:主要目標(biāo)是功率器件的 RDSON 和擊穿電壓。通常具有非常廣泛的組件類型(雙極、CMOS、LDMOS 和 DEMOS 器件),涵蓋從低壓(LV,幾伏)到極高電壓(HV,數(shù)百伏)的應(yīng)用。

高速 BiCMOS:主要目標(biāo)是雙極器件的速度,以支持高達(dá)數(shù)百 GHz 的高速應(yīng)用。

模擬-CMOS:主要特點(diǎn)是高密度 CMOS 邏輯,以及低寄生、低噪聲和高質(zhì)量的無源器件。它們往往是 CMOS 技術(shù)的“衍生物”。

靜電放電 (ESD) 是一種從身體到物體的靜電荷轉(zhuǎn)移,它會(huì)在短時(shí)間內(nèi)(數(shù)百納秒)產(chǎn)生高電流(幾安培)。ESD 事件可能由 IC 在制造過程中的人工處理/測(cè)試引起,并可能導(dǎo)致災(zāi)難性的損壞。為了保證 ESD 對(duì)處理/測(cè)試的穩(wěn)健性,每個(gè) IC 都經(jīng)過標(biāo)準(zhǔn) ESD 測(cè)試,通常是人體模型 (HBM) 和帶電設(shè)備模型 (CDM)。

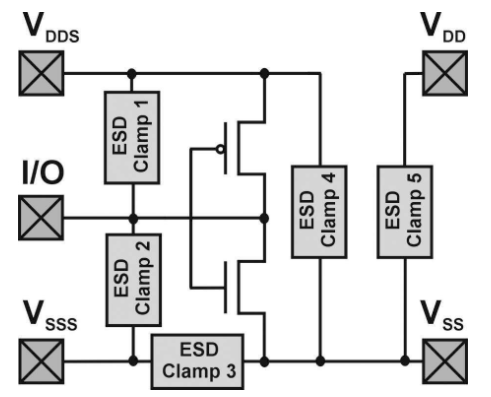

為了達(dá)到所需的 ESD 穩(wěn)健性水平,在每個(gè)焊盤上添加了專用的片上電路(通常稱為“ESD 保護(hù)”或“ESD 鉗位”),以將 ESD 能量吸收到受保護(hù)電路的安全水平。在典型的 ESD 保護(hù)實(shí)施中,每個(gè)焊盤到焊盤的組合都必須具有通過 ESD 保護(hù)的有效 ESD 放電路徑(圖 1)。模擬技術(shù)對(duì) ESD 穩(wěn)健設(shè)計(jì)提出了許多挑戰(zhàn)。

ESD 技術(shù)挑戰(zhàn)

CMOS 和模擬技術(shù)之間的一個(gè)根本區(qū)別在于后者通常是模塊化構(gòu)建的。這允許 IC 設(shè)計(jì)人員僅選擇一部分可用的工藝掩模,以精確定制設(shè)計(jì)需求(并非給定工藝中可用的所有組件都可用于設(shè)計(jì))。

從 ESD 設(shè)計(jì)的角度來看,這意味著 ESD 設(shè)計(jì)人員必須支持具有不同掩模組的相同 ESD 應(yīng)用。這可能非常具有挑戰(zhàn)性,因?yàn)?ESD 保護(hù)的實(shí)際行為在很大程度上取決于掩模組。換句話說,可能需要構(gòu)建多個(gè)版本的相同 ESD 保護(hù),具體取決于可用的掩模組。

模擬技術(shù)的另一個(gè)具有挑戰(zhàn)性的方面在于利用模型。雖然最先進(jìn)的 CMOS 技術(shù)只有幾年的壽命,但模擬技術(shù)可能使用 10-15 年,甚至 20 年。在此生命周期內(nèi)產(chǎn)生的應(yīng)用程序組合對(duì) ESD 設(shè)計(jì)來說是一個(gè)相當(dāng)大的挑戰(zhàn)。

ESD 設(shè)計(jì)挑戰(zhàn)

漏極擴(kuò)展 MOS

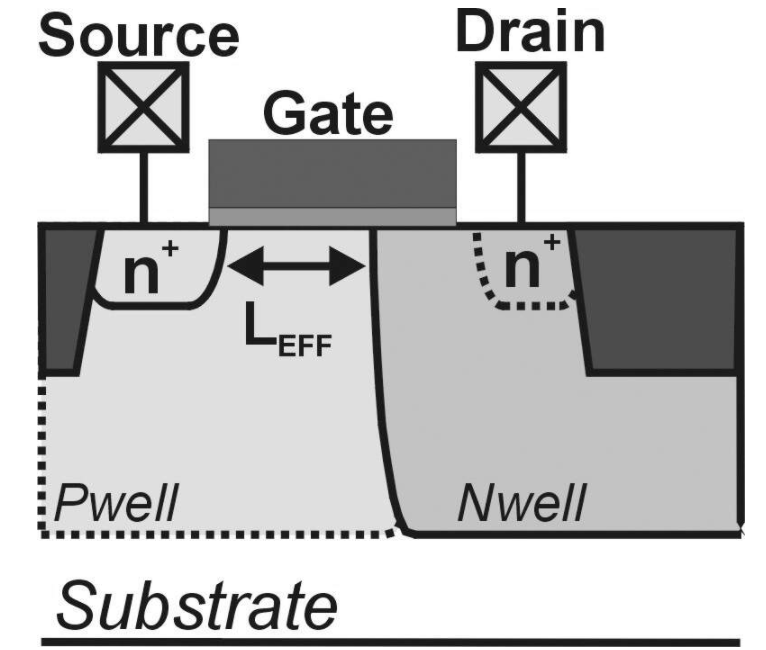

漏極擴(kuò)展 MOS (DEMOS) 是一種器件,其中將同類型的低摻雜區(qū)添加到高摻雜漏極區(qū)或漏極擴(kuò)展區(qū)(圖 2)。這會(huì)影響額定電壓(即擊穿增加)和漏柵壓降(與柵氧化層可靠性相關(guān))。另一方面,這種類型的設(shè)計(jì)會(huì)降低驅(qū)動(dòng)電流特性,因?yàn)橥ǖ劳ǔ]有針對(duì)該結(jié)進(jìn)行優(yōu)化。更復(fù)雜的版本,橫向擴(kuò)散 MOS (LDMOS),具有更好的電流驅(qū)動(dòng)特性。

從 ESD 的角度來看,DEMOS 晶體管具有非常低的 ESD 魯棒性,即在 ESD 條件下能夠承受高電流密度的能力。DEMOS 的 ESD 弱點(diǎn)是高效 ESD 設(shè)計(jì)的主要挑戰(zhàn),因?yàn)樗枰厥獾?ESD 保護(hù)電路,在 ESD 事件(這對(duì)面積有影響)期間不會(huì)使用 DEMOS 晶體管。在過去的 15 年中,多項(xiàng)研究已經(jīng)解決了這個(gè)特定問題,這也歸功于在最先進(jìn)的 CMOS 技術(shù)中使用這些組件。

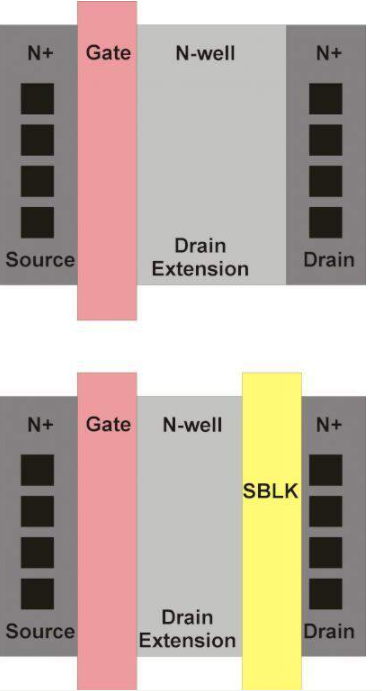

最近的一項(xiàng)工作 [1] 表明,在高摻雜/低摻雜漏區(qū)(圖 3 中的“SBLK”區(qū))上阻止硅化工藝可以顯著提高 DEMOS 晶體管的 ESD 穩(wěn)健性。

這種結(jié)構(gòu)基本上增加了漏極側(cè)的電阻。雖然它的具體影響相當(dāng)復(fù)雜,但它可以被視為一種防止非均勻電流傳導(dǎo)通過器件整個(gè)寬度上的 ESD 電流分布的方法。

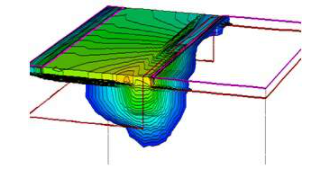

3 維 TCAD 電熱模擬清楚地描繪了沿器件整個(gè)寬度的均勻 ESD 電流分布,并阻止了漏區(qū)的硅化(圖 4)。這將允許一些 ESD 能量被具有這種結(jié)構(gòu)的 DEMOS 耗散,從而減少對(duì) ESD 保護(hù)設(shè)計(jì)的限制。

高壓有源 FET

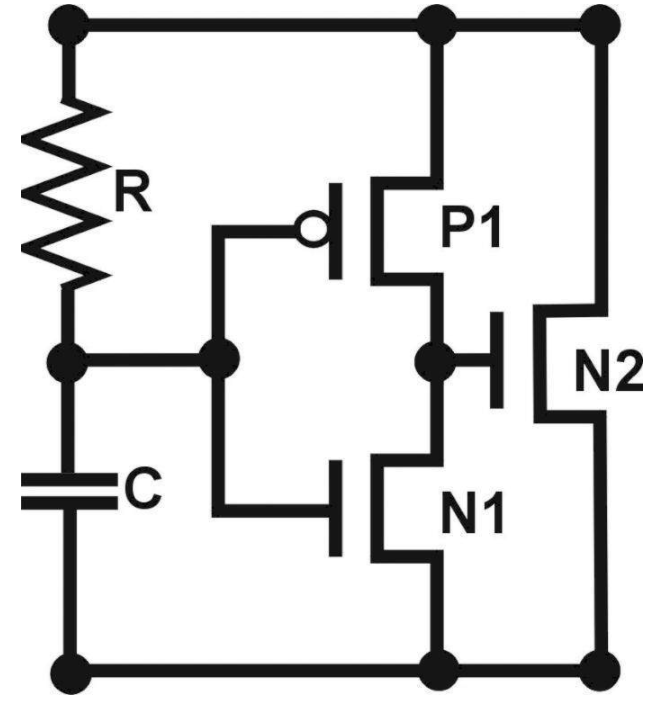

“有源 FET”是非常流行的 ESD 保護(hù)器件,通常用于低電壓應(yīng)用。該名稱指的是 ESD 電流在主動(dòng)操作模式下通過 MOS 器件分流的事實(shí)。此模式僅在 ESD 條件下通過 ESD 事件檢測(cè)器啟用。該電路被定時(shí)以在 ESD 事件的整個(gè)持續(xù)時(shí)間(1-2 微秒)內(nèi)保持導(dǎo)通狀態(tài)。

在 CMOS 技術(shù)中,氧化物和漏極結(jié)共享相同的額定電壓,通態(tài)是通過將漏極與柵極瞬態(tài)耦合來實(shí)現(xiàn)的。此概念的基本實(shí)現(xiàn)如圖 5 所示。

對(duì)于 HV 器件(如前面提到的 DEMOS 和 LDMOS),漏極額定值可能遠(yuǎn)高于柵極額定值(例如,漏極額定值為 20V,而柵極僅為 3.3V)。因此,如圖所示的電路將無法工作,因?yàn)槁O和柵極基本上具有相同的電壓,從而導(dǎo)致柵極可靠性問題(圖 5)。

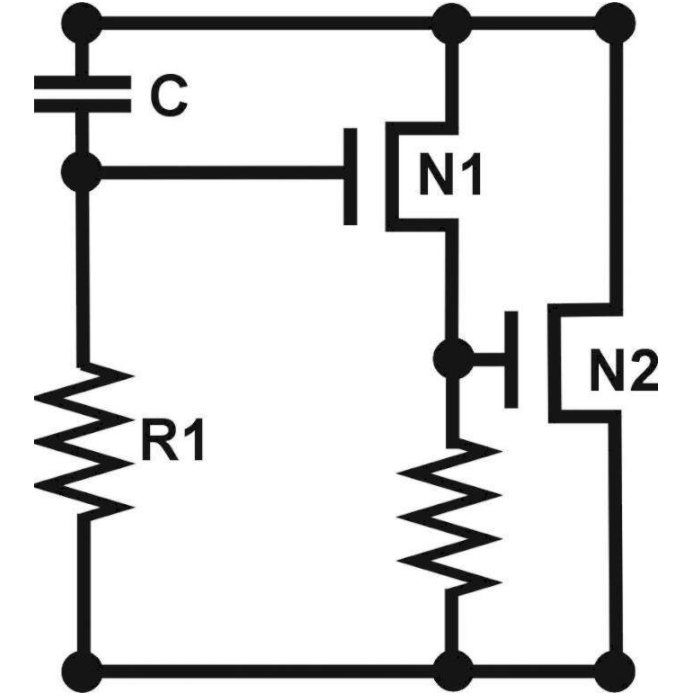

需要一種將焊盤電壓分壓以實(shí)現(xiàn)適當(dāng)柵極電壓的方法。這可以通過源跟蹤級(jí)實(shí)現(xiàn)(圖 6)。該方案允許典型的高壓器件在正常的漏極和柵極工作額定值內(nèi)工作。此外,它還提供了優(yōu)于電路的兩個(gè)顯著優(yōu)勢(shì)(圖 5):

電容小得多,因?yàn)樗?qū)動(dòng)一個(gè)小得多的晶體管。

開啟/關(guān)閉時(shí)間常數(shù)是分開的,可以單獨(dú)優(yōu)化。

高壓可控硅整流器 (SCR)

可控硅整流器 (SCR) 是 pnpn 結(jié)構(gòu)。由于垂直pnp晶體管和嵌入在這種pnpn結(jié)構(gòu)中的橫向npn晶體管的相互耦合,就ESD功耗而言,SCR是最有效的器件。一旦兩個(gè)雙極中的一個(gè)打開,它就會(huì)打開另一個(gè),依此類推。

參考圖 2,通過在漏阱擴(kuò)展中添加高摻雜 P 型擴(kuò)散,將 SCR 集成到任何 DeMOS(或 LDMOS)中非常簡(jiǎn)單。從圖 6 中可以看出,形成了具有相互耦合的 npn 和 pnp 的 pnpn 結(jié)構(gòu)。此外,柵極的存在可用于進(jìn)一步調(diào)整 HV-SCR ESD 特性。

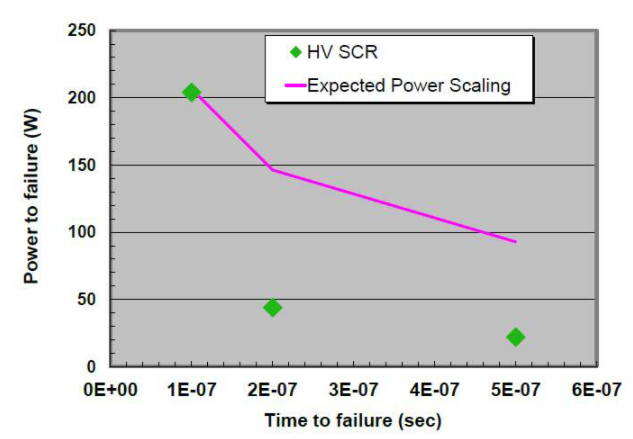

SCR 類型的基本問題是它們能夠保持功率縮放特性 [2],因?yàn)樗┘拥?ESD 應(yīng)力的脈沖寬度增加。更具體地說,基于 SCR 在 100ns ESD 脈沖下消耗的最大功率,人們可以預(yù)期 [2] 在 200ns 和 500ns ESD 脈沖下消耗一定的功率。

然而,在 200ns 和 500ns ESD 脈沖下實(shí)際消耗的最大功率遠(yuǎn)低于預(yù)期(圖 8)。這是一個(gè)重大問題,尤其是在源自系統(tǒng)級(jí)事件的 ESD 脈沖的情況下,應(yīng)力持續(xù)時(shí)間可能大大超過標(biāo)準(zhǔn) HBM 事件的持續(xù)時(shí)間。

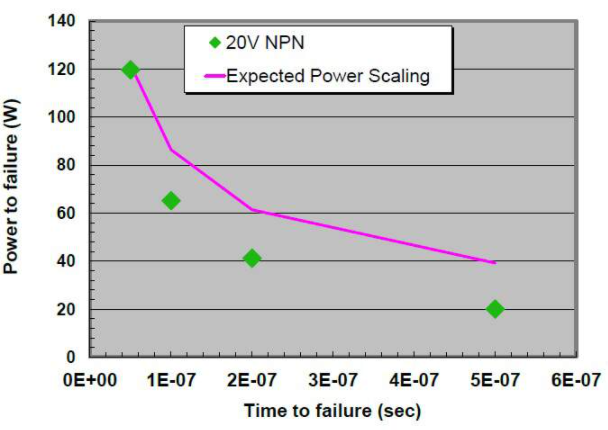

高壓雙極

正如 HV SCR 所強(qiáng)調(diào)的那樣,高壓雙極器件無法避免較差的縮放功率縮放特性。這在圖 9 中可以看到,其中實(shí)際最大功耗從 100ns 開始不遵循功率縮放定律。

除了與設(shè)計(jì)為 ESD 保護(hù)電路的 HV 雙極器件相關(guān)的功率縮放問題外,還有另一個(gè)與 HV 雙極相關(guān)的問題需要考慮:由連接到相鄰焊盤的?? N 擴(kuò)散形成的寄生雙極。

參考圖 10,焊盤(PAD1 和 PAD2)通常具有以公共接地 (GND) 為參考的 ESD 保護(hù)。在從 PAD1 到 PAD2 的 ESD 事件的情況下,ESD 電流(圖 10 中的紅色實(shí)線)將從 ESD 保護(hù) 1 流過公共 GND 和 ESD 保護(hù) 2,到達(dá) PAD2。由于 N 擴(kuò)散與 PAD1 和 PAD2 相關(guān),現(xiàn)在形成了一個(gè)寄生 npn 雙極(公共 p 襯底充當(dāng)雙極的基極),它可以在 ESD 事件期間傳導(dǎo)電流并最終失效。

這種配置的主要問題是由于 ESD 電流在 ESD 保護(hù) 2 中流動(dòng),寄生雙極(公共接地)的基極具有升高的電位。這使得寄生雙極非常容易被觸發(fā),因此,容易失敗。

與 CMOS 技術(shù)不同,在模擬技術(shù)中,具有多個(gè) N 型擴(kuò)散以支持許多不同的額定電壓和隔離技術(shù)是很常見的。因此,任何 N 型擴(kuò)散的排列都會(huì)在類似于圖 10 所示的情況下產(chǎn)生寄生效應(yīng)。考慮到發(fā)射極、集電極、基極類型和幾何效應(yīng)的數(shù)量,很有可能在一個(gè)電路中產(chǎn)生數(shù)百個(gè)寄生雙極給定的技術(shù)。這對(duì)于 ESD 設(shè)計(jì)來說頗具挑戰(zhàn)性,因?yàn)?ESD 保護(hù)網(wǎng)絡(luò)必須能夠充分保護(hù)上述寄生效應(yīng)。

ESD 資格挑戰(zhàn)

“片上”系統(tǒng)級(jí)要求

為保證 IC 制造過程中對(duì) ESD 事件的穩(wěn)健性,進(jìn)行了 HBM 和 CDM 測(cè)試。在過去的幾年中,需要在 IC 級(jí)別進(jìn)行系統(tǒng)級(jí) ESD 保護(hù)的新趨勢(shì)正在出現(xiàn)。通常系統(tǒng)級(jí) ESD 保護(hù)是在系統(tǒng)級(jí)解決的,方法是在電路板上(靠近 ESD 應(yīng)力源)放置專用瞬態(tài)電壓抑制器 (TVS) 電路。這一趨勢(shì)背后的基本原理是,如果單個(gè) IC 具有 ESD 系統(tǒng)級(jí)穩(wěn)健性,則可以消除 TVS(從而降低成本和系統(tǒng)設(shè)計(jì)復(fù)雜性)。

在不深入探討為什么這個(gè)理由存在缺陷的情況下,這些要求對(duì) IC 級(jí) ESD 設(shè)計(jì)的影響是巨大的,不僅在 ESD 面積方面,而且在設(shè)計(jì)復(fù)雜性和所需的學(xué)習(xí)周期方面。

自定義 ESD 級(jí)別要求

IC 級(jí) ESD 穩(wěn)健性的典型 ESD 級(jí)要求是 2000V HBM 和 500V CDM。盡管已明確證明 1000V HBM 和 250V CDM 在當(dāng)今的制造環(huán)境中提供了非常可靠的 ESD 設(shè)計(jì),但某些客戶可能需要在所選引腳上具有 >8KV HBM 性能以處理未指定的系統(tǒng)級(jí)事件。這些要求的影響同樣在面積和開發(fā)時(shí)間方面非常重要。

可持續(xù)發(fā)展戰(zhàn)略

模擬技術(shù)組件產(chǎn)品組合的廣度以及隨后需要保護(hù)的大量應(yīng)用,并不適合滿足所有要求的“單一 ESD 策略”。因此,模擬技術(shù)領(lǐng)域的 ESD 工程師正在研究所有 ESD 保護(hù)策略,仔細(xì)權(quán)衡利弊以找到最合適的解決方案。

有源 FET:它們非常有效,在低壓應(yīng)用中很受歡迎。然而,對(duì)于高電壓應(yīng)用,低 FET 的驅(qū)動(dòng)電流和大面積的結(jié)合使它們不太吸引人。

基于擊穿的設(shè)備:它們依賴于寄生雙極 npn 或 pnp。由于出色的面積/ESD 性能權(quán)衡,基于 Npn 的技術(shù)非常受歡迎。主要缺點(diǎn)是難以通過過程變化來控制性能。

SCRs:這些解決方案在面積/ESD 性能方面是最有效的,而且它們很容易設(shè)計(jì)。然而,從 DRC-LVS 的角度來看,固有的閂鎖風(fēng)險(xiǎn)和難以實(shí)現(xiàn),在某種程度上限制了它們的使用。

自我保護(hù):這種解決方案在大輸出驅(qū)動(dòng)器的情況下非常有效,它也可以設(shè)計(jì)為承受 ESD 事件。缺點(diǎn)是需要在 IP 和 ESD 之間進(jìn)行協(xié)同設(shè)計(jì)。

近年來,模擬技術(shù)的相關(guān)性迅速增加,在這項(xiàng)工作中,我們回顧了與技術(shù)、設(shè)計(jì)和資格要求相關(guān)的 ESD 挑戰(zhàn)。

參考文獻(xiàn)

[1] A. Salman 等人,國(guó)際可靠性物理研討會(huì)論文集,2012

[2] DC Wunsch 和 RR Bell,IEEE Trans。核。Sci., 1968

[3] IEC61000-4-2:電磁兼容性 (EMC) – 第 4-2 部分

編輯:hfy

-

ESD

+關(guān)注

關(guān)注

49文章

2265瀏覽量

175105 -

模擬技術(shù)

+關(guān)注

關(guān)注

17文章

469瀏覽量

40200

發(fā)布評(píng)論請(qǐng)先 登錄

半導(dǎo)體制冷技術(shù):從原理到應(yīng)用深度解析

邊緣AI MPU深度盤點(diǎn):品牌、型號(hào)與技術(shù)特性全解析

解鎖未來汽車電子技術(shù):軟件定義車輛與區(qū)域架構(gòu)深度解析

移動(dòng)設(shè)備中的MDDESD防護(hù)挑戰(zhàn):微型化封裝下的可靠性保障

深度解析模擬技術(shù)中 ESD 穩(wěn)健設(shè)計(jì)的挑戰(zhàn)

深度解析模擬技術(shù)中 ESD 穩(wěn)健設(shè)計(jì)的挑戰(zhàn)

評(píng)論