當我們啟動Flex Logix時,eFPGA面臨的挑戰是有許多客戶和應用程序,他們似乎都希望eFPGA位于不同的代工廠,不同的節點和不同的陣列大小。每個人都希望eFPGA與在同一節點上的FPGA領導者一樣快且密度高。哦,客戶似乎要等到最后一刻,才需要盡快使用eFPGA。

Xilinx和Altera(現在為Intel PSG)需要大約3年的時間,需要數十或數百個人才能在新的工藝節點中推出新的FPGA系列。Flex Logix如何以更少的團隊開發不到一年的速度和密度的eFPGA?

革命性的FPGA互連

Flex Logix聯合創始人兼高級副總裁程望(Cheng Wang)在加州大學洛杉磯分校(UCLA)攻讀博士學位期間設計了多個復雜度不斷提高的FPGA芯片。在此過程中,他意識到FPGA中使用的傳統網狀互連占據了80%的面積:可編程邏輯僅占20%。因此,他發明了一種新型互連,該互連與網狀結構一樣好,但可以使用一半的晶體管和一半的金屬層來實現!

Cheng,UCLA的Dejan Markovic教授和其他人在ISSCC上發表了有關在他們最終的FPGA項目中使用的這種新互連的論文,并獲得了享有盛譽的杰出論文獎。今天,其中四分之三與Flex Logix有關。

UCLA在互連上申請了專利:Flex Logix是唯一的被許可人。自創立Flex Logix以來,Cheng對互連進行了大量改進,Flex Logix專利涵蓋了這些互連。Flex Logix現在擁有20多項美國已發布專利,這是我們在中國的第一項專利。

我們如何使用專利互連來設計eFPGA

FPGA公司擁有非常龐大的設計團隊,并且需要花費數年的時間,因為他們進行的是全定制設計,這通常保留給包括微處理器在內的超大批量產品使用。

跨多個代工廠和數十個節點需要eFPGA。如果我們每個版本必須雇用50多人,那么eFPGA永遠不會變得經濟或及時可用。

如今,大多數ASIC設計都是使用標準單元完成的:鑄造廠通常免費提供簡單的構建塊,并且已經在工藝,電壓和溫度范圍內進行了表征。可以按照邏輯設計規則組裝標準單元設計,并保證其能正常工作。

但是標準單元設計通常是優化的全定制設計面積的2倍。

FPGA是80%的互連,而Cheng的互連需要?個晶體管。因此,與其使我們的eFPGA變小,不如讓我們的eFPGA全部來自標準單元:使用標準單元增加2倍的面積可以抵消Cheng互連的面積減少50%的影響。因此,在給定的過程節點中,我們最終得到與FPGA領導者相同的密度和性能。

但是,因為我們使用標準單元進行設計,所以從開始之日起不到一年就可以進入市場。并且擁有更小的設計團隊。

因此,如果客戶想要從180nm到5nm的代工廠/節點所需的eFPGA,我們可以在他們的設計進度約束內快速交付。

結論

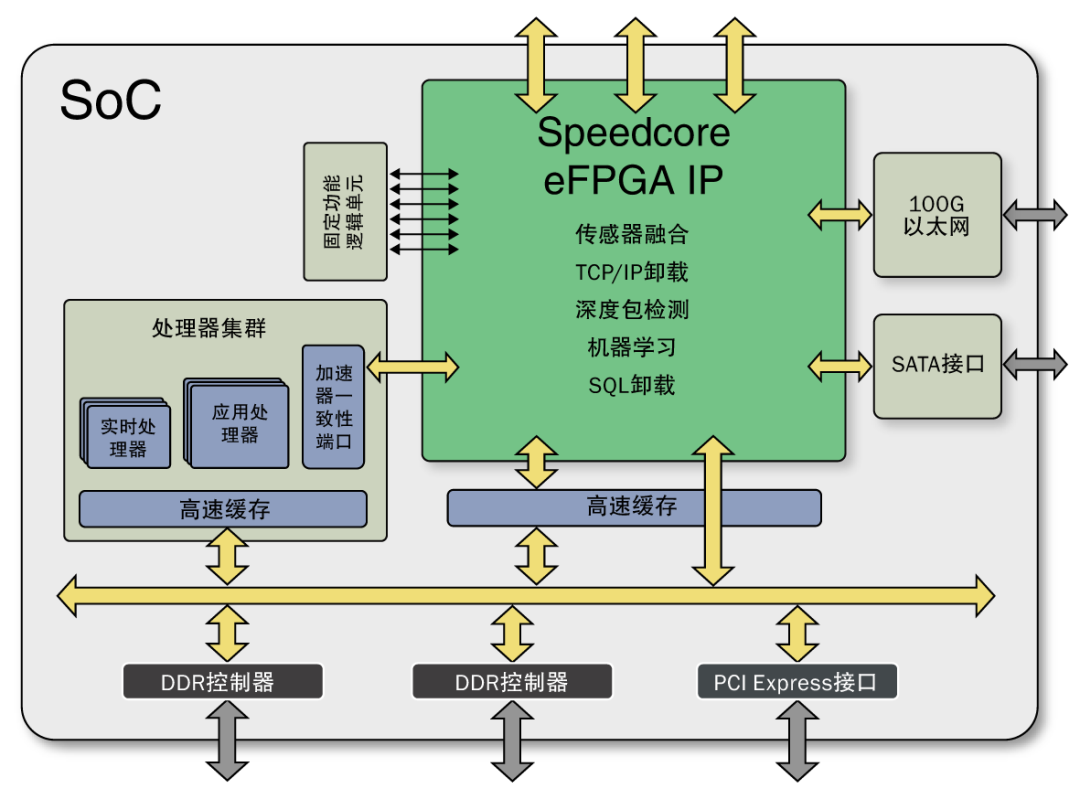

eFPGA對于加速關鍵工作量并使SoC適應不斷變化的算法和協議非常有價值。借助Flex Logix革命性的互連技術和設計方法,我們可以在不到一年的時間內經濟性地在任何鑄造工藝節點上使用它。

責任編輯:tzh

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613951 -

芯片

+關注

關注

459文章

52145瀏覽量

435955 -

asic

+關注

關注

34文章

1242瀏覽量

121974 -

晶體管

+關注

關注

77文章

9977瀏覽量

140621

發布評論請先 登錄

新能源汽車驅動電機專利信息分析

fpga和cpu的區別 芯片是gpu還是CPU

基于微軟專利的帶蝴蝶出瞳擴展的光波導結構

華進半導體榮獲中國專利優秀獎

研究透視:芯片-互連材料

蘋果公開新專利:可折疊設備鉸鏈

基于微軟專利的帶蝴蝶出瞳擴展的光波導結構

Samtec新型評估和開發套件~技術支持,我們是認真的!

Achronix Speedcore eFPGA的特性和功能

今日看點丨ADI收購eFPGA公司Flex Logix;業界首款!湖北發布高性能車規級芯片DF30

Primemas選擇Achronix eFPGA技術用于Chiplet平臺

探索通用互連解決方案的強大之處

我們如何使用專利互連來設計eFPGA?

我們如何使用專利互連來設計eFPGA?

評論