1 系統(tǒng)級設(shè)計與驗證簡介

片上電子系統(tǒng)的速度和復(fù)雜度的不斷提高不僅使得底層的設(shè)計實現(xiàn)易于出問題,而且頂層的系統(tǒng)架構(gòu)、通訊機制、軟硬件劃分等都可能使系統(tǒng)的功能、性能或成本、開發(fā)周期等指標不滿足要求。一旦在底層的實現(xiàn)階段發(fā)現(xiàn)了這種頂層的設(shè)計問題,會有大量的設(shè)計工作重新進行;此外,工程師對設(shè)計規(guī)格的理解偏差,或設(shè)計規(guī)格本身的不完整及二義性也是造成設(shè)計錯誤的原因之一;底層硬件的設(shè)計在驗證時需要大量的輸入激勵和檢驗響應(yīng),在信號級完成這樣的工作不但速度很慢而且容易遺漏。

由于電子系統(tǒng)中相當部分的工作是由軟件完成,所以必須確保在應(yīng)用環(huán)境下軟硬件能夠正確地協(xié)同工作。以前軟件中依賴于硬件的部分通常要等到樣機加工好后才能調(diào)試,使得嵌入式軟件的完整驗證只能在系統(tǒng)設(shè)計周期的后端進行,此時發(fā)現(xiàn)的設(shè)計錯誤通常要花費較高的修改代價,特別是那些牽涉到軟硬件劃分等系統(tǒng)層次的問題。

所有這些都要求我們用跟以往大不相同的方式看待電子系統(tǒng)的設(shè)計流程:設(shè)計規(guī)格必須用形式化的、語法嚴格且語義明確的高級語言描述;從系統(tǒng)的頂層到底層的每一適當?shù)某橄髮哟味疾捎煤线m的高級語言建立相應(yīng)的模型;每一層次的模型都要進行驗證,并可作為下一層次系統(tǒng)模型的參考模型和子模塊的測試平臺。如此,便可形成一系列可執(zhí)行的設(shè)計規(guī)格( Executable Specification ),并將驗證工作左移到系統(tǒng)設(shè)計的早期階段,從而達到消除設(shè)計規(guī)格的歧義性和及早發(fā)現(xiàn)較高層次的設(shè)計錯誤的目的。

目前國際上已普遍做到用高級語言來進行系統(tǒng)的規(guī)格描述和底層實現(xiàn),從而形成從系統(tǒng)頂層到底層的一系列可驗證的模型;軟件與硬件的相互驗證不必等到實物樣機加工好再進行,而是與硬件的RTL模型聯(lián)合仿真。其存在的主要問題有:頂層設(shè)計如算法等用的是傳統(tǒng)的軟件高級語言C++、Fortran等,而底層的硬件設(shè)計用的是硬件描述語言VHDL、Verilog,這樣造成整個設(shè)計和驗證流程不夠順暢,各層次之間難以做到無縫連接;對于更復(fù)雜或運算量非常大的系統(tǒng),驗證的速度尤其是軟硬件聯(lián)合仿真的速度太慢,難以進行有效的驗證。上述問題的解決方法是:規(guī)定軟硬件設(shè)計和驗證統(tǒng)一的高級描述語言;規(guī)范抽象方式和級別,特別是在RTL之上規(guī)范硬件平臺的建模方法。

國際上EDA界經(jīng)過幾年的發(fā)展與討論,公認最有前途成為電子系統(tǒng)設(shè)計與驗證統(tǒng)一語言的就是SystemC,它是在C++的基礎(chǔ)上加上一套適合于硬件描述的模板庫和仿真內(nèi)核構(gòu)成,并不斷地擴充進有望成為標準的附加庫,如驗證庫SCV、事務(wù)級建模庫TLM API等。

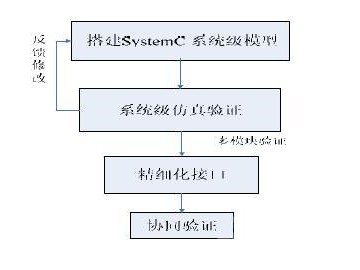

在基于SystemC的系統(tǒng)級建模和驗證流程中,首先在頂層建立較高抽象級的模型,主要用于完成系統(tǒng)控制與算法的設(shè)計分析,進行物理架構(gòu)的功能性能的設(shè)計分析。通過建立系統(tǒng)級的抽象模型,執(zhí)行仿真分析和評估給出量化的指標,從而對系統(tǒng)級的功能性能作出正確的設(shè)計,并在此基礎(chǔ)上進行軟硬件模塊劃分。

2 模型層次

為便于后面敘述的方便,這里先簡要介紹一下系統(tǒng)建模的幾種抽象方式和應(yīng)用類型。

抽象方式可分為:

非定時功能UTF(UnTimed Functional):可用于模型的接口和內(nèi)部功能,進程的執(zhí)行和數(shù)據(jù)傳輸都不耗費時間, 時間只可能作為定序機制而使用。

定時功能TF(Timed Functional):可用于模型的接口和內(nèi)部功能,進程的執(zhí)行和數(shù)據(jù)傳輸都都分配了有限的時間。

總線周期精確BCA(Bus Cycle Accurate):僅用于模型的接口,而非內(nèi)部功能,定時精確到時鐘周期,通常與系統(tǒng)時鐘相關(guān),不引入管腳級的細節(jié),信息傳輸通常以事務(wù)的方式建模。

管腳周期精確PCA(Pin Cycle Accurate):僅用于模型的接口,而非內(nèi)部功能,定時精確到時鐘周期,通常與系統(tǒng)時鐘相關(guān),描述精確到管腳級。

寄存器傳輸精確RT(Register Transfer accurate):同時用于模型的接口和內(nèi)部功能,所有的事情都被安排了時間,時鐘用于同步,需要做完整的詳細的功能說明,每個寄存器、每條總線、每一位在每個周期的行為都有描述,能夠直接被邏輯綜合器綜合成硬件實現(xiàn),等同于RTL模型。

應(yīng)用類型可分為:

系統(tǒng)架構(gòu)模型SAM(System Architectural Model):是系統(tǒng)的一份不含時間信息的可執(zhí)行規(guī)格,描述系統(tǒng)的硬件和軟件成分。模型接口用不含管腳細節(jié)的UTF方式,通常描述通訊協(xié)議;模型功能也用UTF方式,行為用算法來建模,且主要以順序方式描述。此種模型主要用于架構(gòu)探索和算法驗證。

系統(tǒng)性能模型SPM(System Performance Model):是系統(tǒng)的一份含時間信息的可執(zhí)行規(guī)格,描述系統(tǒng)的硬件和軟件成分。模型接口用不含管腳細節(jié)的UTF或TF方式,通常描述通訊協(xié)議,通訊行為可以是定時的但不一定達到周期精確;模型功能可用TF或UTF方式,行為用算法來建模,順序或并發(fā)方式都可以采用,定時不是周期精確的。此種模型主要用于高層次性能建模和時間預(yù)算。

事務(wù)級模型TLM(Transaction Level Model):用于建模可執(zhí)行的平臺,通常只描述硬件。模型接口用不含管腳細節(jié)的TF方式,可以是也可以不是周期精確的,數(shù)據(jù)傳輸用事務(wù)方式建模;模型功能用TF方式,但不必是周期精確的。

功能模型(Functional Model):指抽象級別在TLM之上的模型,包括SAM和SPM。

系統(tǒng)級模型(System Level Model):指抽象級別在RTL之上的模型,包括SAM、SPM和TLM。

3 事務(wù)級建模方法TLM

事務(wù)級建模方法TLM(Transaction Level Modeling)是為了解決以下問題而發(fā)展起來的,這些問題包括提供軟件開發(fā)的早期平臺;系統(tǒng)架構(gòu)探索與驗證;系統(tǒng)級模型在模塊級驗證中的應(yīng)用。它用于建模可執(zhí)行的平臺,通常只描述硬件。

所謂事務(wù),一方面指把低層次的信息傳輸組合成的較高級別的傳輸,比如把讀寫一大塊數(shù)據(jù)作為一個事務(wù),它包含總線上的若干次突發(fā)傳輸,每個突發(fā)傳輸又會包含地址連續(xù)的多個數(shù)據(jù)傳輸;另一方面指不牽涉具體的信號,而是把傳輸中涉及到的信息分類作為整體表示。事務(wù)級建模方法把模塊的功能和模塊間的通訊分開建模,模塊間通訊用事務(wù)來表示,接口用不含管腳細節(jié)的TF方式,功能也用TF方式,是否周期精確根據(jù)需要而定。通過提高抽象級別,并把分散在各模塊中的通訊協(xié)議處理功能集成在專門的通訊模塊中完成,極大地加快了系統(tǒng)仿真的速度。

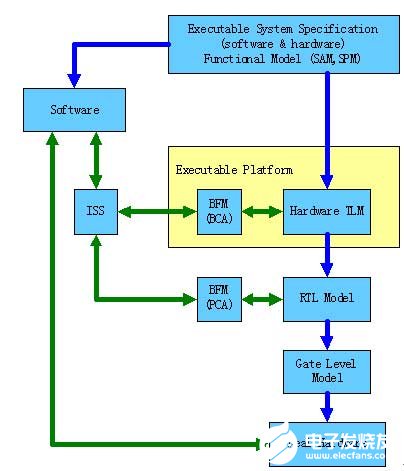

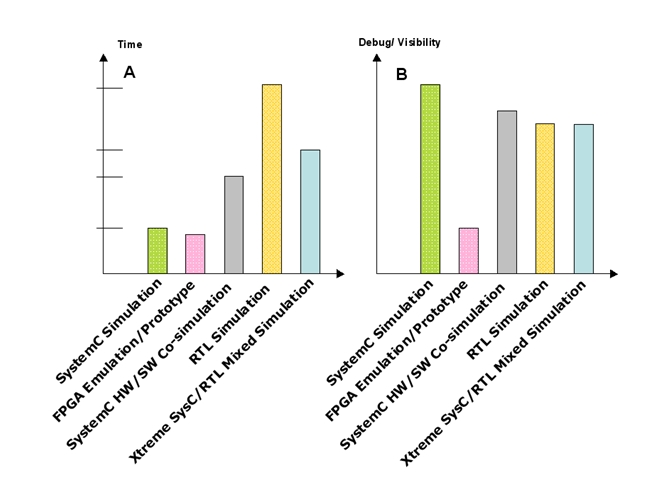

軟件工程師可以使用處理器指令集仿真器ISS(Instruction Set Simulator)來測試程序,ISS使用總線事務(wù)訪問外部設(shè)備,總線事務(wù)通過總線功能模型連接到硬件模型,從而使軟硬件測試過程無縫連接。以前的總線功能模型是PCA,相應(yīng)的硬件模型是RTL,導(dǎo)致仿真速度很慢, 現(xiàn)在通過使用事務(wù)作為內(nèi)部模塊間通信的方式,總線功能模型是BCA,相應(yīng)的硬件模型是TLM,軟件模型、硬件模型和測試平臺可以在較高的抽象級連接成整體,仿真速度快100倍以上,并可在設(shè)計周期中更早的階段與ISS一起作為軟件運行的平臺。具體可見示意圖1。

在TLM級實現(xiàn)可執(zhí)行的規(guī)格有助于進行系統(tǒng)架構(gòu)的性能分析,探索不同的架構(gòu)方案;為RTL設(shè)計提供參考模型和驗證平臺;可以作為軟件開發(fā)的平臺,優(yōu)化軟硬件劃分方案。所以事務(wù)級的系統(tǒng)硬件可執(zhí)行規(guī)格又稱為可執(zhí)行平臺EP( Executable Platform )。它是架構(gòu)精確的,為軟件開發(fā)和模塊級的驗證提供一個快速全功能的環(huán)境。當EP作為底層RTL模塊的測試平臺時,需要將相應(yīng)的TLM模塊替換為目標RTL模塊與transactor的組合,transactor是SystemC的術(shù)語,作用是將一種抽象級的接口轉(zhuǎn)換為另一種抽象級的接口。

圖1 由TLM構(gòu)成的可執(zhí)行平臺

由于高層模型(如算法模型)的仿真速度通常要比低一層的模型快10倍或更多,同時高層模型可重用為低層次設(shè)計的參考模型,高層的可執(zhí)行規(guī)格可作為低層設(shè)計模塊的驗證平臺,因此經(jīng)常需要將不同層次的模型混合仿真。把高層模型的對外接口用transactor形式轉(zhuǎn)換成低層模型的接口,就可以連接到整個系統(tǒng)上。

4 總結(jié)

系統(tǒng)級設(shè)計和驗證包括從系統(tǒng)規(guī)格開始的設(shè)計輸入、架構(gòu)評估、功能驗證、多層次多語言混合驗證、軟硬件協(xié)同開發(fā)及驗證等高抽象度的描述方法和驗證技術(shù)。

SystemC作為一種適用于多層次建模和仿真的高級語言,已被廣泛應(yīng)用于系統(tǒng)級設(shè)計和驗證的多個領(lǐng)域,為研究不同的系統(tǒng)結(jié)構(gòu)、進行算法評估、軟硬件任務(wù)劃分和軟件開發(fā)提供了有效的方法。它能使整個團隊使用一種語言來靈活地組合不同的抽象層次,使設(shè)計者優(yōu)化系統(tǒng)的設(shè)計和驗證流程。

事務(wù)級模型(TLM)與寄存器傳輸級(RTL)模型相比較,是在更高抽象級別上對系統(tǒng)硬件建模,在結(jié)構(gòu)級的組件上交換數(shù)據(jù)或執(zhí)行事件。事務(wù)級描述抽象度較高,比RTL容易開發(fā),這樣在設(shè)計早期就可得到系統(tǒng)的硬件模型;TLM比相應(yīng)的RTL模型仿真速度快100倍以上,在TLM級的平臺上可以很快地運行軟件,非常適合于架構(gòu)和性能分析、早期的軟硬件協(xié)同驗證。

責任編輯:gt

-

接口

+關(guān)注

關(guān)注

33文章

8918瀏覽量

153123 -

eda

+關(guān)注

關(guān)注

71文章

2869瀏覽量

176255

發(fā)布評論請先 登錄

SystemC的隨機驗證過程是怎樣的?

關(guān)于功能驗證、時序驗證、形式驗證、時序建模的論文

如何在ModelSim下用SystemC的做驗證?

請問數(shù)字電路的系統(tǒng)級設(shè)計驗證工具及流程?

用SystemC進行SoC的系統(tǒng)級設(shè)計與仿真

基于SystemC事務(wù)級的建模仿真研究

基于SystemC的系統(tǒng)驗證研究和應(yīng)用

利用基于SystemC/TLM的方法學進行IP開發(fā)和FPGA

片上網(wǎng)絡(luò)的SystemC建模研究

SystemC 的驗證方法和流程介紹

基于SystemC的系統(tǒng)級建模和驗證流程

基于SystemC的系統(tǒng)級建模和驗證流程

評論