之前介紹了 SelectIO 邏輯資源,本篇咱們就聊一聊與SelectIO 邏輯資源水乳交融、相得益彰的另一個(gè)概念——IO_FIFO。

1個(gè)IO_FIFO包括1個(gè)IN_FIFO 和1個(gè)OUT_FIFO,它是7系列FPGA新設(shè)計(jì)的IO專用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)邏輯功能的擴(kuò)展。

FPGA的每個(gè)BANK有4個(gè)IN_FIFO和4個(gè)OUT_FIFO,相當(dāng)于每12個(gè)IO對(duì)應(yīng)1個(gè)IN_FIFO和1個(gè)OUT_FIFO。

IN_FIFO從ILOGIC接收4bit位寬的輸入數(shù)據(jù),但卻可以輸出4bit或者8bit位寬的數(shù)據(jù)到FPGA內(nèi)部SLICE。OUT_FIFO正好相反,從OLOGIC接收4bit或者8bit位寬的輸入數(shù)據(jù),但卻輸出4bit位寬數(shù)據(jù)。

每一個(gè)IO_FIFO的存儲(chǔ)大小為768bit,可以配置成12組4X4位寬數(shù)據(jù)的FIFO,也可以配置成10組4X8bit位寬數(shù)據(jù)的FIFO。每個(gè)IO_FIFO的深度為9。如圖1所示為IO_FIFO的結(jié)構(gòu)示意圖:

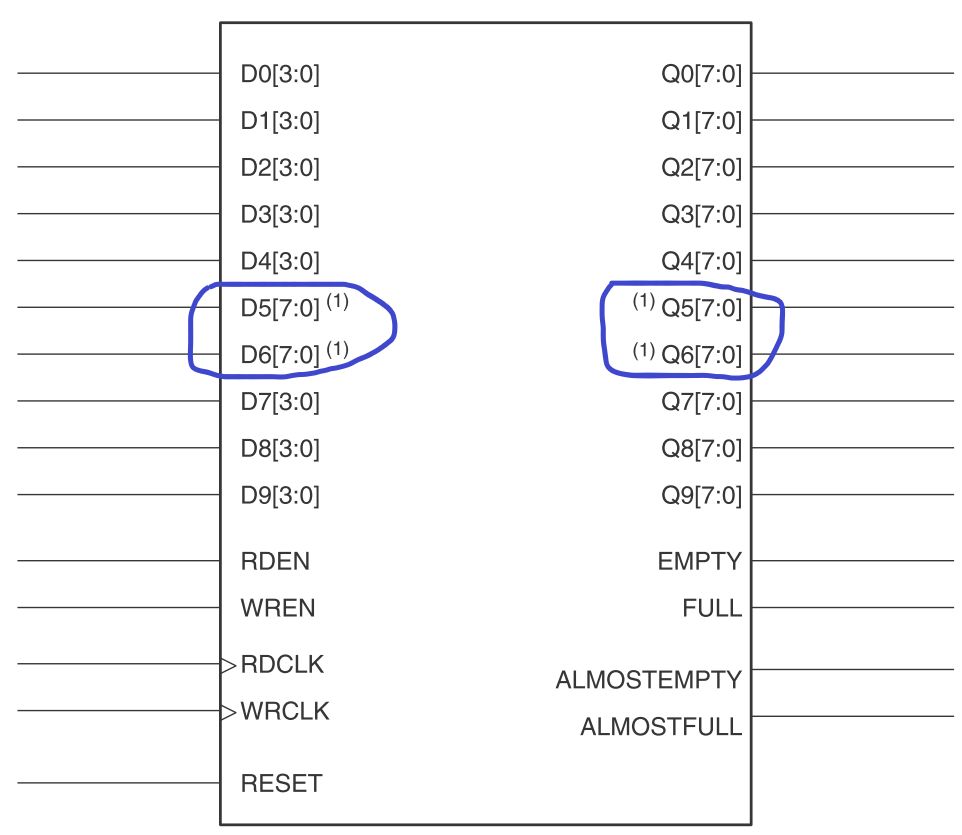

如圖2所示為IN_FIFO的原語(yǔ)框圖:

正如前面所說(shuō),當(dāng)配置成12組的4bit位寬輸入,4bit位寬輸出時(shí),輸入D0[3:0]~ D9[3:0]對(duì)應(yīng)輸出Q0[3:0]~ Q9[3:0];輸入D10[3:0]即為輸入D5[7:4],對(duì)應(yīng)輸出Q5[7:4];輸入D11[3:0]即為輸入D6[7:4],對(duì)應(yīng)輸出Q6[7:4]。

當(dāng)配置成10組4bit位寬輸入,8bit位寬輸出時(shí),D0[3:0]~D9[3:0]對(duì)應(yīng)輸出Q0[7:0]~ Q9[7:0],此時(shí)寫(xiě)時(shí)鐘頻率是讀時(shí)鐘頻率的2倍。OUT_FIFO和IN_FIFO操作過(guò)程正好相反,咱們這里就不羅嗦了。

總的來(lái)說(shuō),IO_FIFO其實(shí)就是存儲(chǔ)深度比較小、位寬固定為4/8bit的普通FIFO ,7系列FPGA單獨(dú)設(shè)計(jì)了這樣的FIFO,更適用于IO接口處的字節(jié)/半字節(jié)數(shù)據(jù)緩存。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613986 -

數(shù)據(jù)緩存

+關(guān)注

關(guān)注

0文章

24瀏覽量

7315

發(fā)布評(píng)論請(qǐng)先 登錄

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

Altera Agilex 7 M系列FPGA正式量產(chǎn)出貨

SDRAM控制器的設(shè)計(jì)——Sdram_Control.v代碼解析(異步FIFO讀寫(xiě)模塊、讀寫(xiě)SDRAM過(guò)程)

xilinx FPGA IOB約束使用以及注意事項(xiàng)

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】Key-test

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】測(cè)試一

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒(méi)有?

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+04.SFP之Aurora測(cè)試(zmj)

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+01.開(kāi)箱(zmj)

FIFO Generator的Xilinx官方手冊(cè)

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

xilinx7系列FPGA新設(shè)計(jì)的IO專用FIFO解析

xilinx7系列FPGA新設(shè)計(jì)的IO專用FIFO解析

評(píng)論