ROM是只讀型存儲器,寫入數(shù)據(jù)之后就不能在對數(shù)據(jù)進行更改。下面提供3種創(chuàng)建ROM的方法:

一、自己動手通過readmemh或readmemb函數(shù)來將自己寫的文件與ROM進行關聯(lián);有幾點需要注意的地方:寄存器rom的大小(位寬和深度)如下面的代碼中位寬為8,深度為1024

// An highlighted block module myrom( clk, addr, q ); input clk; input [9:0] addr; output reg[9:0] q; reg [7:0] rom [1023:0]; initial begin $readmemh("./xxx.txt",rom,0,1023); //讀16進制的數(shù)據(jù) //格式$readmemh("file_name",memory_name[,start_addr[,finish_addr]]); //file_name:文件名;memory_name:ROM名;start_addr:開始地址;finish_addr:結束地址 //[]的內容為可選內容, //readmemb 讀2進制的數(shù)據(jù) end always(posedge clk) q<=rom[addr]; endmodule

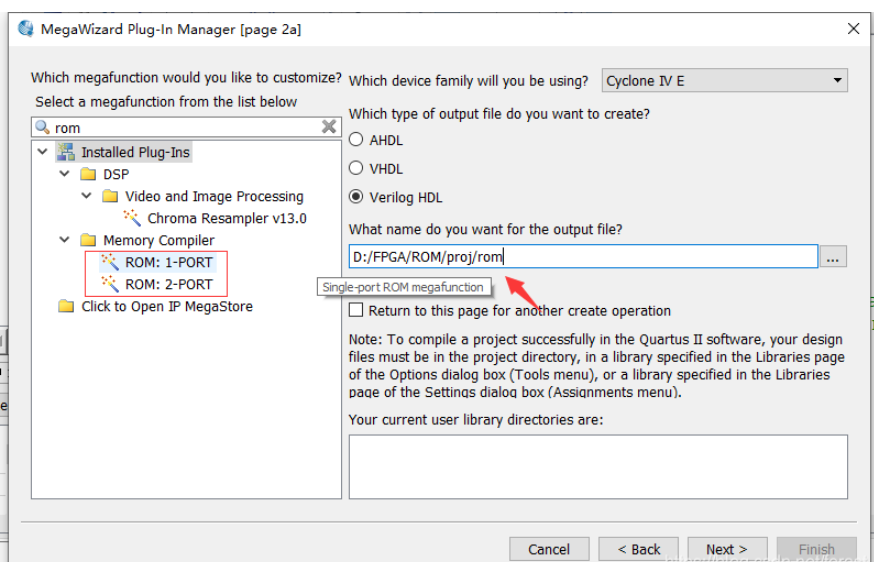

二、第二中方法是通過ip核創(chuàng)建rom。選擇菜單欄中的Tools下的ip核配置工具,搜索rom,選著Verilog語言,并命名文件。點擊下一步

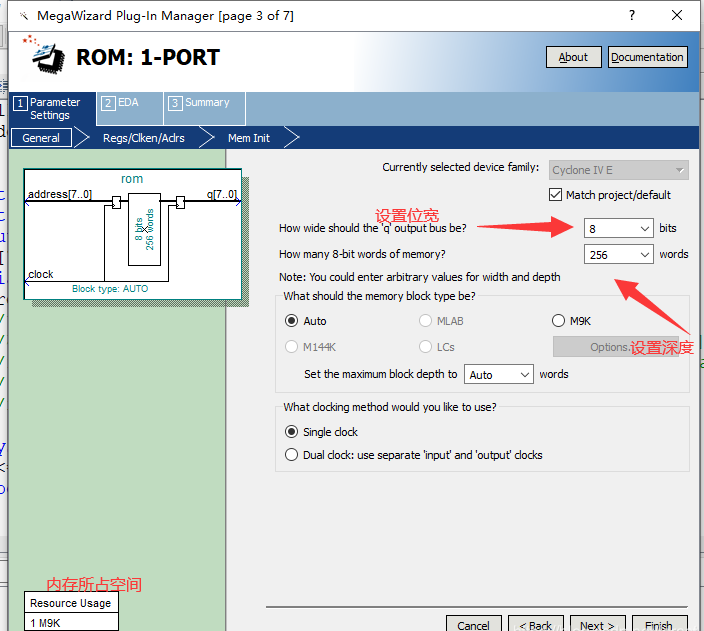

可以看到,在配置工具中依然需要設置位寬和深度。

在mem init中的文件名,這里需要注意的是文件必須是.mif和.hex文件。

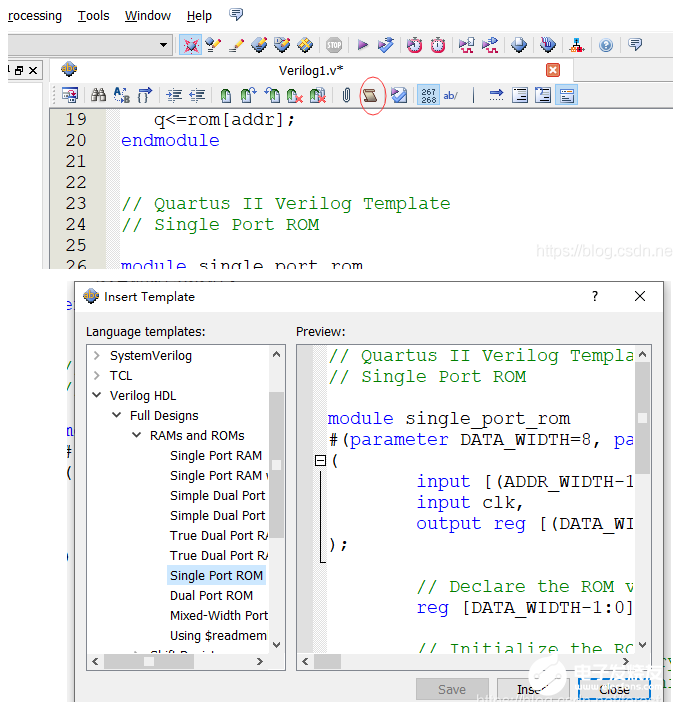

三、第三中方法是直接生成代碼,在代碼段上進行修改。

生成的代碼段如下:這里需要修改的是兩個參數(shù)DATA_WIDTH、ADDR_WIDTH。然后將對應的文件名修改了就可以了。

// Quartus II Verilog Template // Single Port ROM module single_port_rom #(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=8) ( input [(ADDR_WIDTH-1):0] addr, input clk, output reg [(DATA_WIDTH-1):0] q ); // Declare the ROM variable reg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0]; // Initialize the ROM with $readmemb. Put the memory contents // in the file single_port_rom_init.txt. Without this file, // this design will not compile. // See Verilog LRM 1364-2001 Section 17.2.8 for details on the // format of this file, or see the "Using $readmemb and $readmemh" // template later in this section. initial begin $readmemb("single_port_rom_init.txt", rom); end always @ (posedge clk) begin q <= rom[addr]; end endmodule

編輯:hfy

-

存儲器

+關注

關注

38文章

7632瀏覽量

166371 -

ROM

+關注

關注

4文章

578瀏覽量

86993

發(fā)布評論請先 登錄

啟動Redis的三種方法

如何使用三種方式進行文件的創(chuàng)建

STM32的三種Boot模式的差異

記錄一下MCU存在ROM中的bootloader的三種方法

解決電池問題有三種方法

三種不同的“防 Ping”技巧

用示波器快速捕獲異常的三種方法

三種IGBT驅動電路和保護方法

直接進入TIVA系列MCU存在ROM中的bootloader的三種方法(轉載)

三種種創(chuàng)建ROM的方法解析

三種種創(chuàng)建ROM的方法解析

評論