在DRAM Storage Cell章節中,介紹了單個 Cell 的結構。在本章節中,將介紹 DRAM 中 Cells 的組織方式。

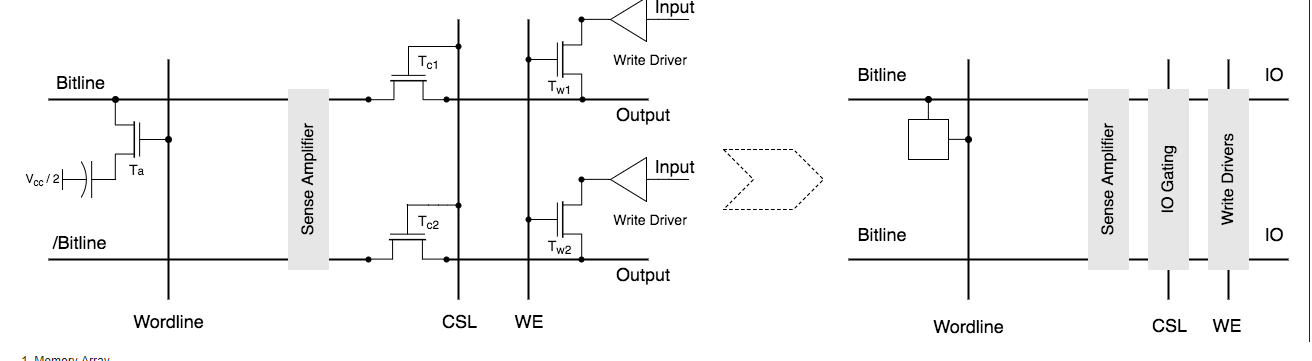

為了更清晰的描述 Cells 的組織方式,我們先對上一章節中的 DRAM Storage Cell 進行抽象,最后得到新的結構圖,如下:

1. Memory Array

DRAM 在設計上,將所有的 Cells 以特定的方式組成一個 Memory Array。本小節將介紹 DRAM 中是如何將 Cells 以 特定形式的 Memory Array 組織起來的。

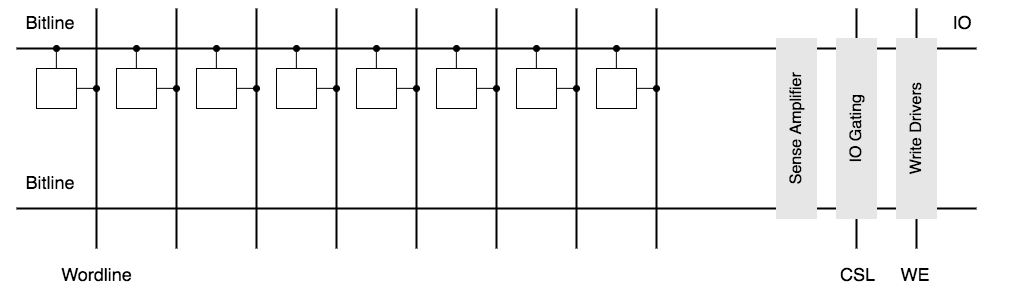

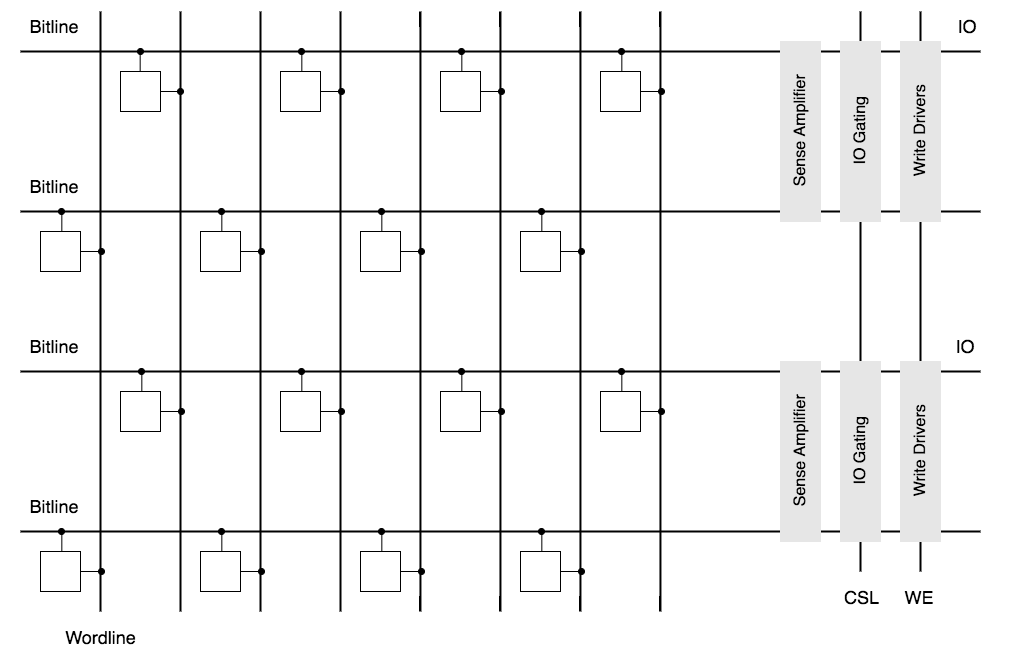

首先,我們在不考慮形式的情況下,最簡單的組織方式,就是在一個 Bitline 上,掛接更多的 Cells,如下圖所示:

然而,在實際制造過程中,我們并不會無限制的在 Bitline 上掛接 Cells。因為 Bitline 掛接越多的 Cells,Bitline 的長度就會越長,也就意味著 Bitline 的電容值會更大,這會導致 Bitline 的信號邊沿速率下降(電平從高變低或者從低變高的速率),最終導致性能的下降。為此,我們需要限制一條 Bitline 上掛接的 Cells 的總數,將更多的 Cells 掛接到其他的 Bitline 上去。

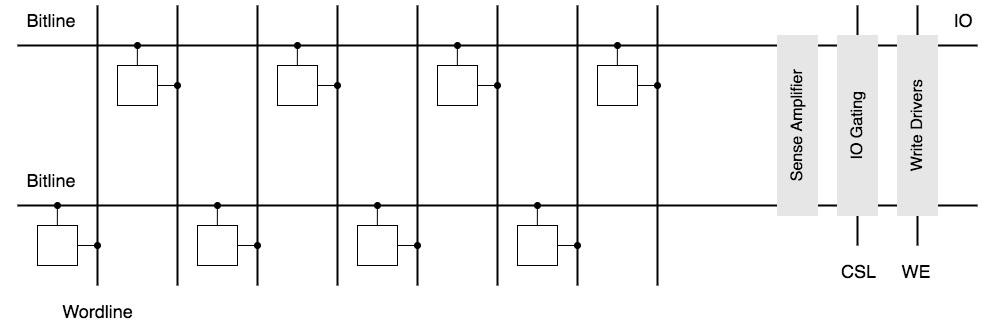

從 Cell 的結構圖中,我們可以發現,在一個 Cell 的結構中,有兩條 Bitline,它們在功能上是完全等價的,因此,我們可以把 Cells 分攤到不同的 Bitline 上,以減小 Bitline 的長度。然后,Cells 的組織方式就變成了如下的形式:

當兩條 Bitline 都掛接了足夠多的 Cells 后,如果還需要繼續拓展,那么就只能增加 Bitline 了,增加后的結構圖如下:

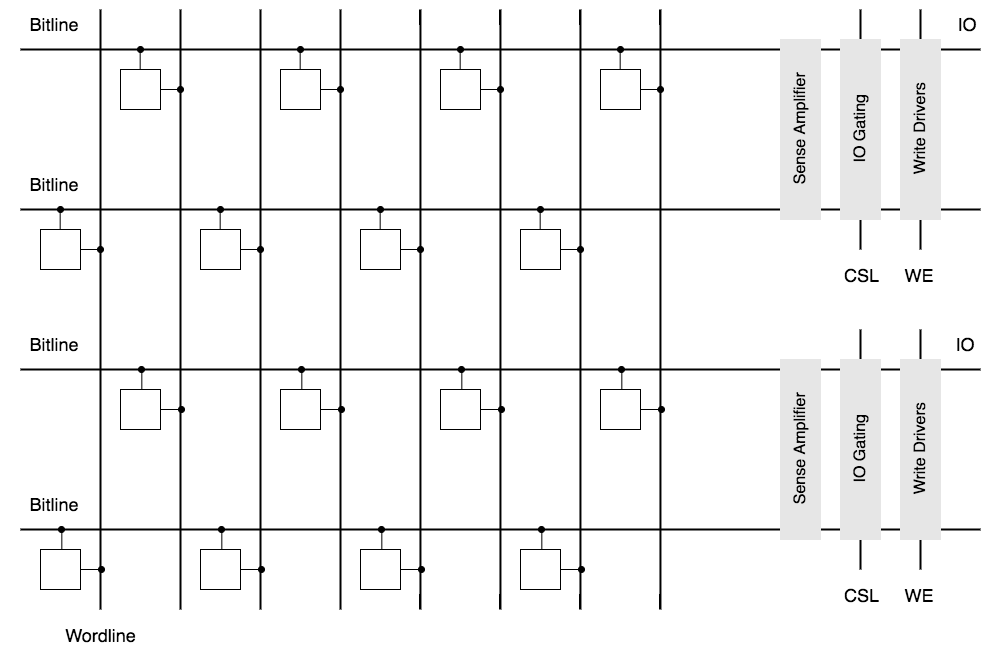

從圖中我們可以看到,增加 Bitline 后,Sense Amplifier、Read Latch 和 Write Driver 的數量也相應的增加了,這意味著成本、功耗、芯片體積都會隨著增加。由于這個原因,在實際的設計中,會優先考慮增加 Bitline 上掛接的 Cells 的數量,避免增加 Bitline 的數量,這也意味著,一般情況下 Wordline 的數量會比 Bitline 多很多。

上圖中,呈現了一個由 16 個 Cells 組成的 Memory Array。其中的控制信號有 8 個 Wordline、2 個 CSL、2 個 WE,一次進行 1 個 Bit 的讀寫操,也就是可以理解為一個 8 x 2 x 1 的 Memory Array。

如果把 2 個 CSL 和 2 個 WE 合并成 1 個 CSL 和 1 個 WE,如下圖所示。此時,這個 Memory Array 就有 8 Wordline、1 個 CSL、1 個 WE,一次可以進行 2 個 Bit 的讀寫操作,也就是成為了 8 x 1 x 2 的 Memory Array。

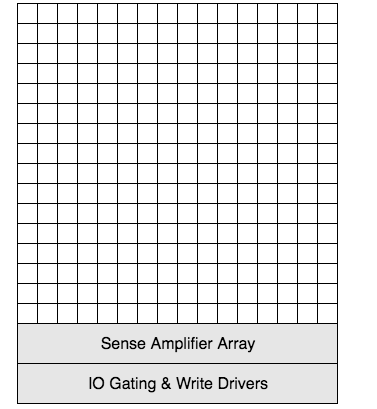

按照上述的過程,不斷的增加 Cells 的數量,最終可以得到一個 m x n x w 的 Memory Array,如下圖所示

其中,m 為 Wordline 的數量、n 為 CSL 和 WE 控制信號的數量、w 則為一次可以進行讀寫操作的 Bits。

在實際的應用中,我們通常以 Rows x Columns x Data Width 來描述一個 Memory Array。后續的小節中,將對這幾個定義進行介紹。

1.1 Data Width

Memory Array 的 Data Width 是指對該 Array 進行一次讀寫操作所訪問的 Bit 位數。這個位數與 CSL 和 WE 控制線的組織方式有關。

1.2 Rows

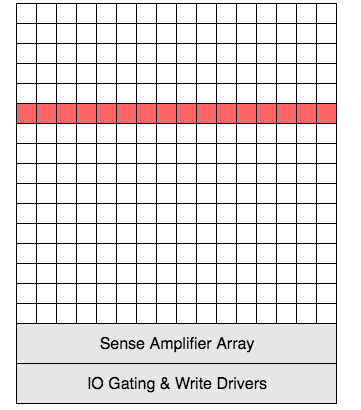

DRAM Memory 中的 Row 與 Wordline 是一一對應的,一個 Row 本質上就是所有接在同一根 Wordline 上的 Cells,如下圖所示。

DRAM 在進行數據讀寫時,選中某一 Row,實質上就是控制該 Row 所對應的 Wordline,打開 Cells,并將 Cells 上的數據緩存到 Sense Amplifiers 上。

Row Size

一個 Row 的 Size 即為一個 Row 上面的 Cells 的數量。其中一個 Cell 存儲 1 個 Bit 的信息,也就是說,Row Size 即為一個 Row 所存儲的 Bit 位數。

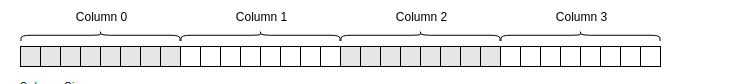

1.3 Columns

Column 是 Memory Array 中可尋址的最小單元。一個 Row 中有 n 個 Column,其中 n = Row Size / Data Width。下圖是 Row Size 為 32,Data Width 為 8 時,Column 的示例。

Column Size

一個 Column 的 Size 即為該 Column 上所包含的 Cells 的數量,與 Data Width 相同。Column Size 和 Data Width 在本質上是一樣的,也是與 CSL 和 WE 控制線的組織方式有關(參考Memory Array小節中關于 CSL 的描述)。

2. Memory Bank

隨著 Bitline 數量的不斷增加,Wordline 上面掛接的 Cells 也會越來越多,Wordline 會越來越長,繼而也會導致電容變大,邊沿速率變慢,性能變差。因此,一個 Memory Array 也不能無限制的擴大。

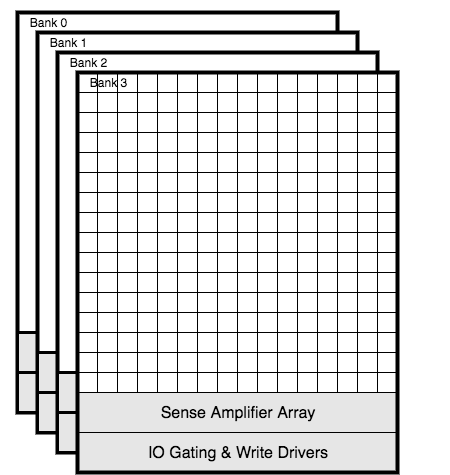

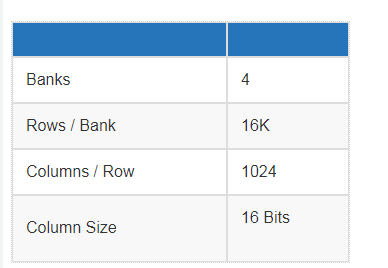

為了在不減損性能的基礎上進一步增加容量,DRAM 在設計上將多個 Memory Array 堆疊到一起,如下圖所示:

其中的每一個 Memory Array 稱為一個 Bank,每一個 Bank 的 Rows、Columns、Data Width 都是一樣的。在 DRAM 的數據訪問時,只有一個 Bank 會被激活,進行數據的讀寫操作。

以下是一個 DRAM Memory Organization 的例子:

-

DRAM

+關注

關注

40文章

2341瀏覽量

185141 -

Cells

+關注

關注

0文章

2瀏覽量

5122

發布評論請先 登錄

存儲DRAM:擴張與停產雙重奏

DRAM基本單元最為通俗易懂的圖文解說

飛凌嵌入式ElfBoard ELF 1板卡-初識設備樹之設備組織架構

ADC_PRO能分析其用其他方式保存的文數據嗎?

DRAM的基本構造與工作原理

一文解 DRAM 中Cells 的組織方式

一文解 DRAM 中Cells 的組織方式

評論