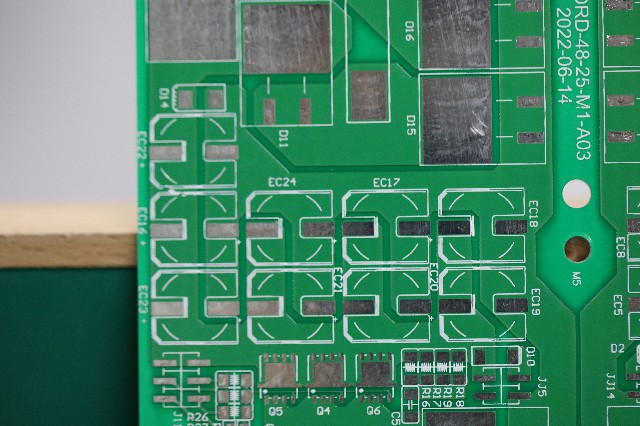

在PCB設計中,您希望時鐘信號迅速到達其集成電路(IC)的目的地。但是,一種稱為時鐘偏斜的現象會導致時鐘信號早晚到達某些IC。當然,這會導致各個IC的數據完整性不一致。

什么是時鐘偏斜

時鐘偏斜是一種現象,其中時鐘信號以不同的間隔到達不同的目的地。時鐘信號通常用于PCB設計中的同步通信。例如,串行外設接口(SPI)使用時鐘信號在設備之間發送和接收數據。

在理想的主機到多個從機組件的配置中,時鐘信號的傳播時間沒有延遲。時鐘總線上連接的所有組件均應同時接收信號。

但是,在實際應用中,會發生傳播延遲,并且時鐘脈沖可能以各種間隔到達目標組件。時鐘偏斜的根源在于寄生電容和時鐘信號的不同走線長度。

想象一下一個來自驅動器的時鐘信號,它分成兩個不同的路徑。路徑A是路徑B長度的一半,并且它們都連接到不同的接收器。很自然,路徑A上的時鐘信號比路徑B上的時鐘信號更早到達目的地。

在電子產品中,時鐘信號用作組件的時間參考,以將接收引腳上的數據位鎖存。一些協議在向上的時鐘脈沖上鎖存數據,而其他協議在向下的時鐘脈沖上鎖存數據。無論采用哪種鎖存機制,可靠的時鐘參考都是重要的。

如果出現時鐘偏斜,則時鐘信號可能比預期的早或晚匹配。當時鐘在數據信號更新之前更改時,接收組件會將舊數據鎖存到其寄存器中。如果協議基于時鐘穩態而不是跳變來鎖存數據,則時鐘偏斜可能會導致接收器用兩個后續數據覆蓋存儲器。

通常,時鐘偏斜對于低速設計不是問題,因為存在大量誤差。但是,如果您要在數百MHz的范圍內設計高速應用程序,則時鐘偏斜將成為真正的問題。

閂鎖錯誤可能會導致數據完整性嚴重受損,并且在實際應用中可能造成災難性的后果。對于時鐘偏斜引起的出牙問題,預防總是比治療更好。

防止PCB設計出現時鐘偏移的技巧

當您了解時鐘偏斜的原因時,防止這種現象就變得容易了。防止時鐘偏斜的關鍵在于確保時鐘信號同時到達不同的接收器。

為此,您需要確保源組件和目標組件之間的走線長度應相等(長度匹配)。這意味著最短的走線長度可能不再是最佳路徑。

在典型的同步設計中,您需要將一個驅動程序連接到多個接收器。可能是,某些接收器將更靠近驅動器,而另一些接收器將更靠近PCB。您需要先將時鐘信號路由到最遠的引腳,并確保其他時鐘信號走線以相同的長度路由。

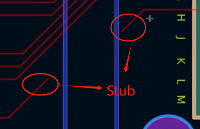

避免時鐘信號分支以防止反射也很重要。這可以通過使用時鐘驅動器來完成,而不是直接從源組件路由到接收器。此外,在時鐘信號上使用阻抗匹配電阻也有助于確保時鐘信號的完整性。

-

PCB設計

+關注

關注

396文章

4775瀏覽量

89135 -

PCB布線

+關注

關注

21文章

468瀏覽量

42503 -

PCB設計軟件

+關注

關注

0文章

55瀏覽量

10369 -

華秋DFM

+關注

關注

20文章

3501瀏覽量

5230

發布評論請先 登錄

原理圖和PCB設計中的常見錯誤

PCB設計中容易遇到的問題

SMT貼片前必知!PCB設計審查全攻

深度解析:PCB高速信號傳輸中的阻抗匹配與信號完整性

PCB設計中的爬電距離:確保電路板安全可靠

pcb設計中布局的要點是什么

pcb設計中如何設置坐標原點

CDCM7005-SP高性能、低相位噪聲和低偏斜時鐘同步器數據表

在PCB設計中如何避免時鐘偏斜

在PCB設計中如何避免時鐘偏斜

評論