如果說摩爾定律預(yù)言了前50年的半導(dǎo)體工藝技術(shù)發(fā)展路線,那么近兩年以來半導(dǎo)體工藝可謂被智能手機等智能終端設(shè)備的軍備競賽瘋狂驅(qū)動著向前。從28nm到22nm、14nm、10nm甚至7nm,在先進半導(dǎo)體工藝激烈競爭下,對數(shù)字電路越來越高的性能要求使半導(dǎo)體供應(yīng)商面臨著更多的挑戰(zhàn),基于這些要求,全行業(yè)的合作將成為一種必然,而EDA廠商、設(shè)備廠商等產(chǎn)業(yè)鏈均卯足全力因應(yīng)客戶需求。

先進設(shè)計/工藝帶來的寄生提取挑戰(zhàn)

一代又一代的半導(dǎo)體晶圓工藝提升使不斷增加的IC設(shè)計密度、性能提升和功耗節(jié)省得以實現(xiàn),但也為電路設(shè)計工程師帶來了許多新興的挑戰(zhàn)。包括創(chuàng)新的工藝特性,諸如FinFET晶體管等代表著向低功耗設(shè)計模式的轉(zhuǎn)變,這就需要EDA軟件在性能和精度方面也要有相應(yīng)的飛躍提升。

在整個設(shè)計周期內(nèi),電路設(shè)計工程師必須在性能和精準度之間權(quán)衡取舍。寄生電路參數(shù)提取也不例外。在使用較為復(fù)雜的FinFET組件的先進工藝節(jié)點上,設(shè)計工程師始終致力于追求更為嚴苛的精準度,也需要更高的性能和容量來實現(xiàn)十億級晶體管設(shè)計。事實上,在現(xiàn)代 IC 中,所有制程節(jié)點都隨著內(nèi)存、模擬電路、標準單元庫以及定制化數(shù)字內(nèi)容的混合變得日益復(fù)雜,當工藝尺寸縮小到低于.35u或深亞微米(DSM)以下時,物聯(lián)連線所產(chǎn)生的互連寄生(電阻、電容等)變得越來越普遍的。這種復(fù)雜性為電路參數(shù)提取工具帶來了一系列不同的挑戰(zhàn),設(shè)計人員需要必須平衡精度、性能和復(fù)雜性等多重因素。

Mentor Graphics代工廠項目總監(jiān)Shu-Wen Chang解釋說:“在前段制程中,例如FinFET的推出標志著CMOS晶體管進入真正的三維器件時代。由于其源漏區(qū)以及與其周圍連接的三維結(jié)構(gòu)方式(包括本地互連和接觸通孔),導(dǎo)致了復(fù)雜性和不確定性。更新更復(fù)雜的制造工藝以及更嚴格的設(shè)計規(guī)則,使得設(shè)計師和代工廠在建模時精確地捕獲FinFET器件內(nèi)部的寄生電阻、電容,以及器件之間的相互作用是至關(guān)重要的。”她補充到,“又例如在后段制程,雙重乃至多重曝光工藝在先進節(jié)點工藝中發(fā)揮越來越重要的作用,互連corners的數(shù)量也將顯著增多。在28納米節(jié)點,可能存在5個互連corners,但在16納米節(jié)點,會看到11至15個corners。多層掩膜版之間對不準產(chǎn)生誤差,漂移等更多復(fù)雜情況,要求設(shè)計人員評估更多寄生參數(shù)提取的corners,以驗證集成電路的時間選擇和性能,為寄生參數(shù)提取工作帶來了更大的挑戰(zhàn)。”

為了應(yīng)對這些挑戰(zhàn),Mentor Graphics推出了全新 Calibre xACT寄生電路參數(shù)提取平臺。Shu-Wen Chang表示,Calibre xACT平臺可滿足包括 14nm FinFET 在內(nèi)廣泛的模擬和數(shù)字電路參數(shù)提取需求,同時最大限度地減少 IC 設(shè)計工程師的猜測和設(shè)置功夫。 Calibre xACT 平臺可借由自動優(yōu)化電路參數(shù)提取技術(shù),針對客戶特定的工藝節(jié)點、產(chǎn)品應(yīng)用、設(shè)計尺寸大小及電路參數(shù)提取目標,實現(xiàn)精準度和周轉(zhuǎn)時間 (TAT) 的最佳組合。采用 Calibre xACT 平臺進行電路寄生參數(shù)提取在滿足最嚴格的精準度要求的同時,還讓客戶體驗到了減少高達 10 倍的周轉(zhuǎn)時間。“xACT平臺采用了Mentor獨特的算法,擁有一個可擴展架構(gòu),能在現(xiàn)代化的計算環(huán)境中充分利用多個 CPU,在不同的情況下降計算分配到不同的CPU內(nèi)核進行并行運算。”她解釋說,“然而,對于全芯片而言,我們需要處理數(shù)十億晶體管的設(shè)計,還包括頂層的數(shù)千萬條內(nèi)部互連。經(jīng)過客戶使用驗證,在使用8個CPU的情況下,通常每小時可提取4~8百萬個網(wǎng)表,比其他競爭產(chǎn)品快2~3倍。”

同時Shu-Wen Chang強調(diào),CalibrexACT電路參數(shù)提取平臺與整個Calibre產(chǎn)品線整合,實現(xiàn)了無縫驗證流程,其中包括用于完整晶體管級模型的CalibrenmLVS 產(chǎn)品,以及用于針對極高精準度電路參數(shù)提取應(yīng)用的CalibrexACT 3D 產(chǎn)品。此外,它還納入了第三方設(shè)計環(huán)境和格式,以確保與現(xiàn)有的設(shè)計和仿真流程相兼容。

用于先進封裝技術(shù)的檢測設(shè)備

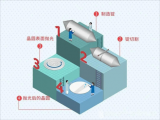

物聯(lián)網(wǎng)和移動消費電子的爆發(fā)驅(qū)動了半導(dǎo)體市場的增長,而電子行業(yè)的最終驅(qū)動力來自于客戶對終端產(chǎn)品的需求。“消費類移動電子產(chǎn)品持續(xù)不斷地推動著生產(chǎn)更小、更快,且更強大的設(shè)備,消費者要求產(chǎn)品具有更長的續(xù)航能力,更低的價格,更豐富多彩的功能,以及更便捷的網(wǎng)絡(luò)連接。這對半導(dǎo)體技術(shù)提出了更多技術(shù)挑戰(zhàn)和風險。例如EUV等先進的光刻工藝,新材料存儲技術(shù),2D到3D工藝轉(zhuǎn)換,工藝視窗控制以及先進封裝技術(shù)等挑戰(zhàn)。” KLA-Tencor(科天)銷售總經(jīng)理任建宇表示。“對先進封裝技術(shù)而言,它可以帶來設(shè)備性能優(yōu)勢,例如增加帶寬以及改善能效。但是,封裝生產(chǎn)方法則更為復(fù)雜,這涉及典型的前端 IC 生產(chǎn)工藝的實施如化學(xué)機械拋光和高縱橫比蝕刻,以及獨一無二的工藝如臨時焊接和晶圓再造。例如,在封裝中,最初的鍵合尺寸是100微米,后來逐漸發(fā)展到今天的10微米。同時,線寬和間距也在不斷的縮小,由之前的10微米一直發(fā)展到今天的1微米。更多新的封裝技術(shù)仍在不斷的涌現(xiàn),比如TSV,3D封裝等。封裝復(fù)雜度在提升,導(dǎo)致封裝的成本在提高。諸如缺陷、良率等問題,‘找到才能解決’,‘能量測才能控制’,因此,在封裝技術(shù)中,檢測和量測也變得越來越重要。結(jié)合科天在前端半導(dǎo)體工藝控制中的專業(yè)技術(shù),以及在與世界級的先進封裝研發(fā)公司和產(chǎn)業(yè)聯(lián)盟合作過程中取得的經(jīng)驗,科天開發(fā)出了靈活而高效的缺陷檢測解決方案,可幫助解決從晶圓級至最終組件所遇到的封裝挑戰(zhàn),例如提升良率,降低成本,縮短上市周期,降低風險等等。”

科天資深營銷總監(jiān)Prashant Aji認為,在封裝技術(shù)領(lǐng)域面臨著如下轉(zhuǎn)折:由移動設(shè)備驅(qū)動的縮小尺寸,晶圓級封裝的出現(xiàn),轉(zhuǎn)向OSAT(外包半導(dǎo)體封裝測試),采用工藝前端IC步驟,封裝成本等等。“消費電子產(chǎn)品一直朝著輕薄短小演進,這就要求硬件電路連線和空間、焊球尺寸和間距、產(chǎn)品封裝等尺寸等都要更小,而晶圓上做TSV越來越多,傳統(tǒng)的封裝過程被打破,復(fù)雜性提高,先進封裝被引入到中端制成過程。尺寸要求和封裝要求都越來越小,線寬越來越窄,硅片堆疊層數(shù)越來越多,在高成品率的要求下,檢測良測成了重中之重。他表示,KLA-Tencor是目前唯一一家擁有全線檢測裝置的廠商,晶圓級到RDL、TSV直到最后的封裝,KLA-Tencor都有相應(yīng)的檢測設(shè)備可以使用。

為了滿足封裝市場逐漸上升的需求,科天推出兩款新產(chǎn)品CIRCL-AP和 ICOST830以支持先進半導(dǎo)體封裝技術(shù)檢測。據(jù)Prashant Aji介紹,CIRCL-AP 針對晶圓級封裝中多種工藝制程的檢測與工藝控制而設(shè)計,不僅擁有高產(chǎn)量,還能進行全表面晶圓缺陷檢測、檢查和測量。ICOS T830 可提供IC 封裝的全自動化光學(xué)檢測,利用高度靈敏的 2D 和 3D 來測量廣范的器件類型和不同尺寸的最終封裝品質(zhì)。這兩款系統(tǒng)都可以幫助 IC 制造商和封測代工廠 (OSAT) 在采用創(chuàng)新的封裝技術(shù)時應(yīng)對各類挑戰(zhàn),例如更細微的關(guān)鍵尺寸和更緊密的間距要求。

這兩款系統(tǒng)都可以幫助 IC 制造商和封測代工廠在采用創(chuàng)新的封裝技術(shù)時應(yīng)對各類挑戰(zhàn),例如更細微的關(guān)鍵尺寸和更緊密的間距要求。Prashant Aji表示,中國已經(jīng)成為世界最大的電子市場,未來也具有無限的潛力。”雖然現(xiàn)在中國封裝技術(shù)仍較落后,但是也看到一些封裝企業(yè)在快速成長,例如長電、南通富士通、天水華天等,我們與他們也有合作。整體封裝技術(shù)水平雖然仍有差距,但是我認為他們最大的挑戰(zhàn)是在取得市場方面。因為后進者意味著目前的市場已經(jīng)被占有,而他們要經(jīng)過客戶的測試驗證還需時間。但是對他們而言,反而更容易采用更先進的技術(shù)。未來,科天將與客戶一起,持續(xù)不斷的努力提升良率,改進技術(shù),幫助客戶降低成本,更好的面對新的技術(shù)挑戰(zhàn)。

責任編輯:tzh

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28856瀏覽量

236785 -

IC

+關(guān)注

關(guān)注

36文章

6115瀏覽量

179168 -

eda

+關(guān)注

關(guān)注

71文章

2919瀏覽量

177720

發(fā)布評論請先 登錄

蘇州芯矽科技:半導(dǎo)體清洗機的堅實力量

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測

先進封裝工藝面臨的挑戰(zhàn)

先進碳化硅功率半導(dǎo)體封裝:技術(shù)突破與行業(yè)變革

合科泰榮獲2024-2025中國半導(dǎo)體封測最佳品牌企業(yè)

全面剖析倒裝芯片封裝技術(shù)的內(nèi)在機制、特性優(yōu)勢、面臨的挑戰(zhàn)及未來走向

砥礪創(chuàng)新 芯耀未來——武漢芯源半導(dǎo)體榮膺21ic電子網(wǎng)2024年度“創(chuàng)新驅(qū)動獎”

半導(dǎo)體貼裝工藝大揭秘:精度與效率的雙重飛躍

芯和半導(dǎo)體將參加重慶半導(dǎo)體制造與先進封測產(chǎn)業(yè)發(fā)展論壇

7納米工藝面臨的各種挑戰(zhàn)與解決方案

半導(dǎo)體行業(yè)工藝知識

半導(dǎo)體三巨頭格局生變:英特爾與三星面臨挑戰(zhàn),臺積電獨領(lǐng)風騷

人工智能半導(dǎo)體及先進封裝技術(shù)發(fā)展趨勢

先進半導(dǎo)體工藝面臨哪些挑戰(zhàn)?

先進半導(dǎo)體工藝面臨哪些挑戰(zhàn)?

評論