為CPU 或其它高密度邏輯器件供電從來都不是一件容易的事情,盡管技術的進步最終會降低計算任務所需的電力。相對于不斷提高的運算能力需求,技術的高速發展所帶來的改進仍然入不敷出。這個矛盾在筆記本電腦中尤為突出,盡管每瓦特電能所能提供的運算能力已大大提高,但電池壽命的擴展卻日益接近極限。

無論是由于需求和技術的同步提高導致了性能的停滯或者反之,便攜系統中越來越高的電源電流需求正迫使設計者去熟悉更新的電源技術。本文將探索一些這方面的新技術。

CPU、DSP 和其它大規模邏輯器件芯片尺寸的縮小使其電源電壓不斷下降,目前在+1.5V 至+2.5V 范圍,不久會降低到 1V。高效率地產生這樣低電壓的電源會有一些困難,尤其是在輸出電流達到 10A 或更高時。

和大多數電子設計一樣,高效的電源設計必須綜合考慮多種相互沖突的因素,包括成本和元件數量、效率和散熱、電路尺寸及瞬態特性(如負載階躍響應)等。電池壽命是便攜系統(由電池供電)的主要考慮,而熱耗散問題(也就是效率問題)無論對于電池供電或者是交流供電系統來講都至關重要。

嚴格的負載調整 + 高速響應 = 難以贏得的挑戰

今日的 CPU 內核要求非常嚴格的負載調整。至少到目前為止,一些主要的 CPU 制造商都有如此要求。隨著電源電壓的降低,電源電流和時鐘頻率卻更高了,使得對于電源的要求急劇提高—特別是瞬態響應。日益嚴格的性能要求使設計的難度和成本越來越高,促使人們重新考慮電源的設計。更高的負載電流和更大負載瞬變帶來的后果之一,便是在處理器周圍多出一片電容“叢林”,增加了系統的尺寸和成本。

最快的開關型穩壓器也無法對負載階躍造成的輸出瞬降做出響應,面對這個現實,以及前面所提到的一些問題,迫使我們必須改變思路(以及規格)。以當今 CPU 的速率,只有完全依靠輸出電容來應付其高速階躍。另一方面,更為嚴格的負載調整需要更高的環路增益,而更高增益的環路需要更大的輸出電容來保持穩定。由此看來,某種程度上放松對于負載調整的要求,對于元件數量的降低及其它諸多方面都極為有利。

典型的 DC-DC 轉換器對于負載階躍的響應可劃分為 5 個基本部分(圖 1):

電壓瞬降,幅度等于階躍負載電流乘以輸出電容等效串聯電阻(ESR)。

瞬降之后、DC-DC 轉換器響應之前會有一段電壓緩降,電容上的電壓隨著電容向負載供電而跌落。

電壓恢復期,電感接通并供出負載電流,同時使輸出電容得到補充。

負載撤離引起“ESR 上跳”(與電壓瞬降效應相反)。

電壓過沖,前一個開關周期儲存于電感的能量(負載撤離后)被轉儲到輸出電容。

其中 2、3 和 5 可以通過仔細的設計和正確選擇 DC-DC 控制器而控制到最小。但其中的瞬態電壓階躍部分(1 和 4)則無法消除,除非降低輸出電容的 ESR。快速調節器能夠在發生跳變之后更快地將輸出拉回,但也無法消除跳變本身。即便是最快速的 DC-DC 轉換器(例如 MAX1711,可以在不足 100ns 的時間內響應)對于運行于 600MHz 的 CPU 來講也太慢了。

圖 1. 該波形表示一次瞬態負載階躍響應的主要組成部分

電壓定位

顯然,強迫 DC-DC 達到不切實際的瞬態響應是沒有希望的。一個 600MHz 的 CPU 在 MAX1711 的 100ns 響應時間內已經飛馳了 60 個時鐘周期。既然電源電壓總是要跌落 ESRCOUT × ILOAD STEP 并保持若干個時鐘周期,那么,是否將它拉回正常值能有多大關系呢? 從 CPU 的角度來看,無關緊要。從電源的角度來看,很有關系。

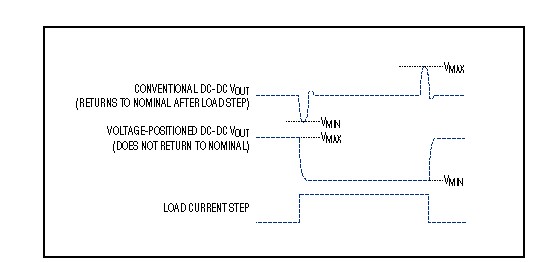

從電源的角度考慮,更愿意使負載電壓不再恢復“正常”。這樣,當負載移去時,將能夠適應將近兩倍的瞬態電壓上升。同樣,當負載接入時也可允許兩倍的瞬態跌落。圖 2 可以說明兩種電壓轉換器負載階躍響應的不同。

圖 2. 由于電壓定位調節器在每次負載階躍后并不試圖恢復輸出電壓至“正常”,它們能夠允許更大的瞬態偏移。而且這個額外的裕量還可以降低功率消耗和輸出電容數量。

基于這種思想,產生了一種新型的 CPU 電源規范(見圖 1 中的灰色方框)。標稱電壓為 1.6V,允許被負載拉低 7.5% (根據目前 CPU 標準)。當負載從滿載變為零時,允許有 7.5%的上升(短暫脈沖式)。穩態輸出電壓包括噪聲和紋波在內不應超過 1.65V。這些數據十分有助于降低電容數量,同時在延長電池壽命及降低熱量耗散方面獲得可觀的收益。

為了充分利用 CPU 電源規格放寬所帶來的好處,可以為給定電源規定一個電壓 / 負載曲線。根據這個特征曲線,實現一種受控形式的負載抑制—有時稱為電壓定位—輸出電壓按照某種負載電流的函數而定位。這種電壓定位允許一定的輸出跌落,而不耗費能量和成本試圖將其拉回。隨著負載電流的升高,輸出按照預先規定的軌跡下落。相比于強行拉回的方式,這種方法對于瞬態問題能夠給出更為圓滿的解決,前者僅提供有限的好處,卻要求更大的電容和更高速的 DC-DC 轉換器。

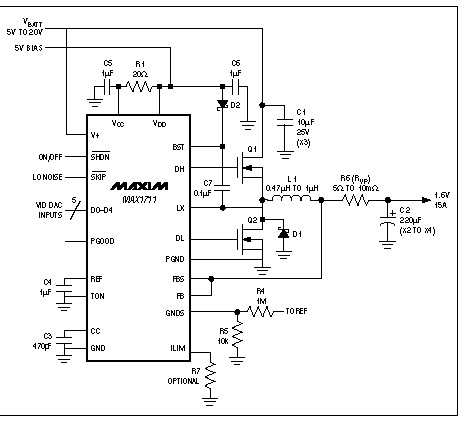

只需不超過三只電阻,就可為許多 DC-DC 轉換器增加電壓定位功能(圖 3)。R4 和 R5 使輸出電壓產生一個很小的正向偏移,使其從(本例中的)標稱 1.6V 升高至 1.62V。R6 (RVP)串聯于輸出,匹配于最差情況下的輸出電容 ESR。RVP 的作用是產生一個確定的、與負載相關的電壓跌落。

圖 3. 這個高效的 15A 穩壓電源很容易轉變為電壓定位設計,只需增加三只電阻:R4、R5 和 R6 (RVP)。

C1 = 陶瓷電容,C2 = Panasonic SP 系列:EEFUEOE221R.

*對于連續 15A 負載電流的情況,由于 IR7809 的散熱限制,請使用(2) IRF7811 或(2) IRF7805。

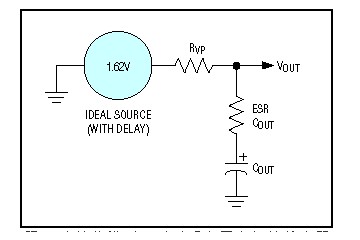

如果 RVP 與濾波電容的 ESR 相匹配,輸出電壓在經歷了負載階躍造成的瞬降(ESR × ILOAD)之后將停留在原位,直到負載再次發生變化。降低負載會引起(ΔI × ESR)的電平上移。經過一個短暫的、因上一次電感放電造成的瞬態脈沖之后,在控制器的 100ns 響應之前(在 7.5%門限以內),直流電平就能夠恢復到預定的空載電壓(本例中為 1.62V)減去 ILOAD × RZ。

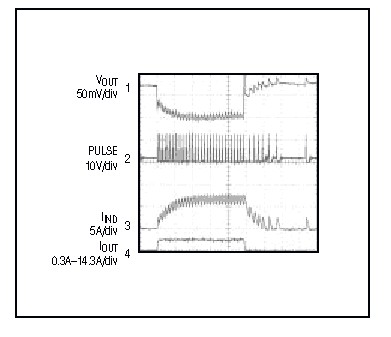

圖 4. 圖 3 所示電路的階躍響應可以說明電壓定位輸出帶來的好處

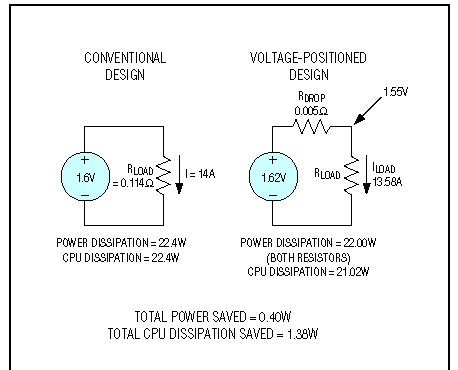

輸出端增加 5mΩ的串聯電阻會降低轉換效率。然而,它也降低了重載時的 CPU 工作電壓,有利于降低功耗并延長電池壽命。和傳統的(無電壓定位的)調節器相比,電壓定位設計可以降低 CPU 功耗 1.38W,降低系統整體功耗 0.4W (圖 5、圖 6)。

圖 5. 該簡化模型可以說明電壓定位的基本原理。當 RVP 等于 ESR (COUT 的等效串聯電阻)時,對于負載階躍可得到理想的“方波”電壓響應(圖 2)。

圖 6. 盡管輸出電阻的增加降低了轉換效率,電壓定位設計同時也降低了消耗在電源和 CPU 內部的功率。

等效效率

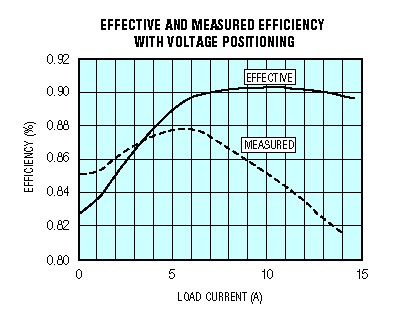

這種改善是以犧牲一部分轉換效率為代價的,為便于將其與傳統的(無電壓定位的)電路相比較,引入一個新的概念“等效效率”。等效效率是指無電壓定位的設計要達到和電壓定位設計相同的性能所需具備的效率。

要確定電壓定位調節器的等效效率,首先用傳統方法[(VOUT × IOUT)/(VIN × IIN)]測出其效率,然后,在每個測點將負載等效為一個電阻(RLOAD = VOUT/IOUT)。對每個測點的 RLOAD 數據,利用無電壓定位時的輸出電壓計算輸出電流(INP = VNP/RLOAD,其中本例中 VNP = 1.6V)。然后,在每個 INP 測點計算等效效率,將對應的無電壓定位時的輸出功率(VNP × INP)除以實際測得的帶有電壓定位的輸出功率(VOUT × IOUT)便得到等效效率。注意,等效效率超出 100%理論上來講是可能的,不過還未能實現。

圖 7 可以說明,對于一個典型的 CPU 電源,這種改善有多明顯。一個傳統設計需要將其滿載效率提高將近 8%才能和電壓定位所帶來的好處相比。

圖 7. 這些曲線顯示,電壓定位的 CPU 電源在滿載時獲得 8%的改善。14A 負載時,傳統設計必須有 90%的轉換效率才能與 82%效率的電壓定位設計相匹敵。

責任編輯:pj

-

芯片

+關注

關注

459文章

52089瀏覽量

435273 -

邏輯器件

+關注

關注

0文章

88瀏覽量

20331 -

調節器

+關注

關注

5文章

873瀏覽量

47261

發布評論請先 登錄

LP8758-B0系列 四相、單通道 16A 輸出 DC-DC 降壓轉換器數據手冊

DC-DC 轉換器無法對負載階躍的開關型穩壓器造成輸出瞬降

DC-DC 轉換器無法對負載階躍的開關型穩壓器造成輸出瞬降

評論