1、 引言

一般的雷達信號源實現(xiàn)主要有三種方式:第一種方式是采用DDS和MCU控制器件結合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結合的方式:第三種是由FPGA等可編程器件實現(xiàn)DDS的方式。第一種方式利用專用DDS器件可以產(chǎn)生具有較好的雜散抑制和諧波抑制性能的雷達波形。控制簡單。但不易于實現(xiàn)復雜波形的控制時序,靈活性差:第二種方式不僅可以產(chǎn)生有較好雜散抑制性能的雷達波形。還易于產(chǎn)生各種復雜的雷達信號,但附加了控制器和時序生成器,增大了電路的復雜性:第三種方式適用于產(chǎn)生特定要求的信號,但開發(fā)周期長,雜散抑制和諧波抑制指標難以達到專用DDS的水平。

隨著FPGA工藝的不斷發(fā)展,設計人員在FP-GA上嵌入軟核處理器成為可能,即所謂的SoPC(System on a Programmable Chip)解決方案,它是指在FPGA內(nèi)部嵌入包括CPU在內(nèi)的各種IP,組成一個完整系統(tǒng).在單片F(xiàn)PGA內(nèi)部實現(xiàn)一個完整系統(tǒng)功能。本文采用Altera公司提供的SoPC Builder工具將Nios II CPU軟核嵌入到Cyclone II系列FPGA內(nèi)部以控制高性能DDS器件AD9858,并采用該片F(xiàn)PGA產(chǎn)生其他控制時序。這樣既充分利用了專用DDS的良好特性和完備功能,同時又大大減少處理器外圍擴展元件數(shù)目,提高系統(tǒng)集成度,降低外圍電路布局走線的復雜度,提高系統(tǒng)的抗干擾能力,便于今后升級擴展。

2、 器件簡介

2.1 CycloneⅡ系列FPGA及NiosⅡ簡介

Cyclone II系列FPGA采用TSMC 90 nm低k絕緣工藝,具有完備的性能和極低的功耗,而價格與ASIC相當。它具有多達68 416個邏輯單元(LE)和1.1 Mbit嵌入式存儲器,具備很多優(yōu)化的特性,包括多達150個嵌入18×18乘法器、專用外部存儲器接口電路、4 Kbit嵌入存儲塊、鎖相環(huán)(PLL)和高速差分I/O能力。其差分I/O信號可提供更好的噪聲容限,產(chǎn)生更低的電子干擾(EMI),并降低了功耗。其增強型鎖相環(huán)(PLL)能提供先進的時鐘管理能力。它還支持:Nios II系列32位RISC嵌入式處理器。

Nios II是Altera公司推出的第二代IP軟核處理器,具有超過200 DMIP的性能,并與其他IP核構成SOPC系統(tǒng)的主要部分。用戶可以通過自定義邏輯的方法在SoPC設計中添加自己開發(fā)的IP核,充分體現(xiàn)了SoPC設計靈活和高效的優(yōu)越性。Nios II系列嵌入式處理器包括三種CPU內(nèi)核:高性能內(nèi)核(Nios II/f,快速)、低成本內(nèi)核(Nios II/e,經(jīng)濟)和性價比均衡內(nèi)核(Nios II/s,標準)。采用Quartus II設計軟件集成的SoPC Builder工具,可以在系統(tǒng)中輕松嵌入Nios II處理器。本系統(tǒng)設計采用該系列EP2C8Q208C7。

2.2 AD9858簡介

AD9858是ADI公司推出的直接數(shù)字頻率合成器(DDS),其10-bit DAC具有高達1 GS/s模擬輸出,頻率高達400 MHz。它具有快速調(diào)頻和精細調(diào)諧分辨率的特性,可快速產(chǎn)生單頻脈沖、線性調(diào)頻及相位編碼信號。AD9858的雜散抑制性能和諧波抑制性能也非常突出,當輸出40 MHz信號時,±1 MHz帶寬內(nèi)的數(shù)模轉換SFDR為一87 dBc;輸出180 MHz信號時。±1 MHz帶寬內(nèi)的數(shù)/模轉換SFDR為-84 dBc,能滿足高性能雷達低雜散、低相位噪聲的要求。AD9858內(nèi)部集成有電荷泵(CP)、相頻檢測器(PFD)和模擬混頻器,可以將高速DDS和鎖相環(huán)(PLL)及混頻器結合使用。AD9858具有對輸入時鐘二分頻功能,外部時鐘高達2 GHz。對AD9858進行配置也非常容易,只需把控制字通過并行或串行方式寫入片上的控制寄存器即可。AD9858比先前的解決方案速度提高了3倍,功耗卻沒有增加,還具有可編程的全睡眠模式,因而適應用于無線設備以及軍事系統(tǒng)的設計。

AD9858的優(yōu)勢在于其具有四套頻率調(diào)諧寄存器(FTW)及四個相位調(diào)整寄存器(POW),這使得它可以方便快速產(chǎn)生線性調(diào)頻信號以及相位編碼信號,而且這四個控制寄存器的選擇是由外部選擇信號PS1、PS0實現(xiàn)的,可大大減少了子碼間的轉換時間。

3、 統(tǒng)設計方案

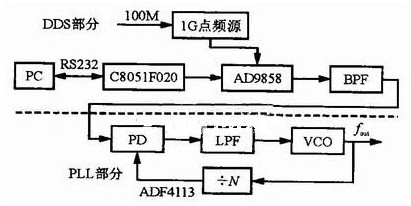

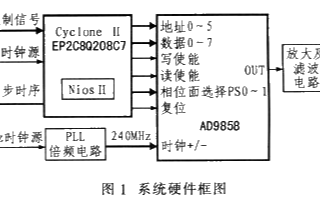

3.1 硬件結構

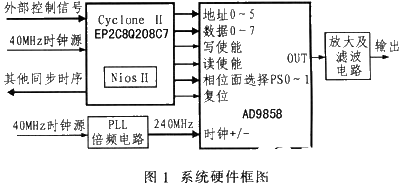

本系統(tǒng)硬件框圖如圖1所示。FPGA和AD9858的并行數(shù)據(jù)/地址總線相連,提供讀/寫信號、復位信號和PS0、PS1信號。AD9858的輸入時鐘由外部時鐘源電路提供,采用差分電平標準。AD9858的輸出首先經(jīng)過放大電路,使其滿足功率要求,然后再經(jīng)過濾波電路。FPGA接收主機的波形選擇控制信號,產(chǎn)生各種同步時序,并為內(nèi)嵌Nios II CPU提供中斷信號。Nios II CPU響應不同的中斷,通過并行方式為AD9858提供各種控制字和初始化,從而產(chǎn)生不同的雷達波形。

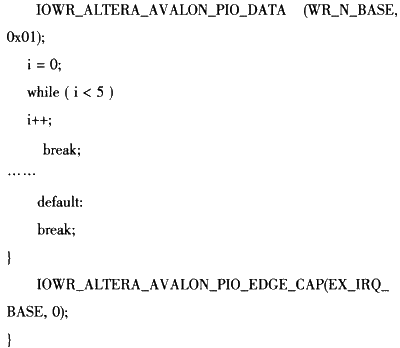

其中Nios II CPU是由Quartus II設計軟件集成的SoPC Builder工具生成。用戶可以通過SoPCBuilder的圖形用戶界面從Ahera公司提供的IP元件庫中選取一些組件,如Nios II、DMA、SRAM、Flash等等,并根據(jù)實際需要設置這些IP的配置參數(shù)。用戶還可以自行編寫HDL代碼模塊作為用戶自定義邏輯添加到SoPC Builder中。由于本系統(tǒng)功能相對簡單,所以采用Cyclone II片內(nèi)的嵌入式RAM構成Nios II的數(shù)據(jù)和程序存儲區(qū)。對于其他功能復雜、控制程序較大的設計,應擴展片外SRAM和Flash作為Nios II的數(shù)據(jù)和程序存儲區(qū)。

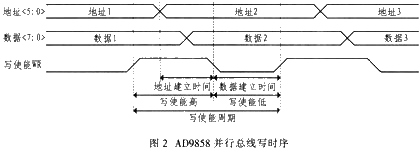

對AD9858的控制實質就是通過其并行數(shù)據(jù)和地址總線傳送控制字,可通過在SoPC Builder中為AD9858生成一個用戶自定義邏輯接口實現(xiàn)。但考慮到AD9858的讀寫時序比較簡單,也可以直接采用Nios II現(xiàn)有IP元件庫里的PIO來生成所需要的讀寫時序。PIO (Parallel Input/Output)是SoPCBuilder中最常用的IP之一,它有輸入、輸出以及雙向口三種類型。另外,它還支持中斷檢測,不過中斷檢測及處理只在其作為輸入設備時可用。AD9858并行總線的寫時序如圖2所示。

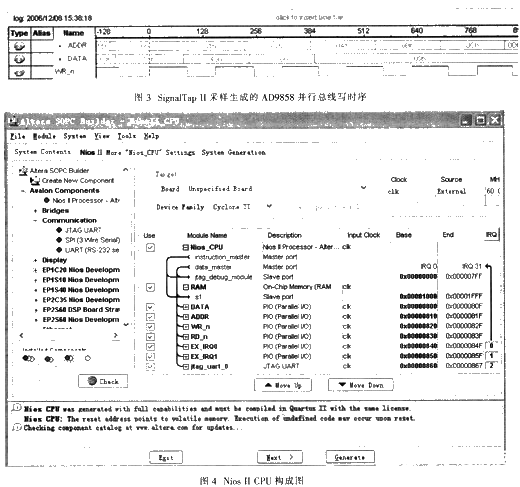

需要注意的是,寫使能信號(低有效)的最小周期為9 ns,為低電平的時間最少是3 ns,為高電平的時間最少是6 ns,而地址和數(shù)據(jù)信號的建立時間分別為3 ns和3.5 ns。圖3為用嵌入式邏輯分析儀SignalTap II采樣的一段用PIO生成的AD9858并行總線寫時序。完全滿足設計要求。

最終生成的Nios II系統(tǒng)如圖4所示。其中,jtag_uart_0是為了調(diào)試時便于Nios II和主機通信而編寫的,也可以省去。外部中斷EX_IRQ0和EX_IRQ1也是用PIO實現(xiàn)。

DDS輸出信號的質量取決于為AD9858提供工作時鐘的外部時鐘源,本系統(tǒng)采用40 MHz高性能晶體振蕩器,然后通過PLL倍頻電路獲得240 MHz參考時鐘。同時將時鐘轉換成符合AD9858要求的差分信號,以降低共模干擾。輸出信號的濾波器設計好壞也直接影響到最終輸出信號的質量。若采用單一的帶通濾波器抑制DDS輸出雜散,對頻率合成器帶內(nèi)雜散性能并沒有提高。采用濾波器組則會帶來電路復雜、增大體積以及延長頻率切換時間等問題。目前,一般是通過DDS輸出驅動倍頻器鏈,達到提高輸出頻譜和拓展頻譜帶寬的要求,但同時也會導致DDS輸出帶內(nèi)頻譜純度惡化。印制板設計要滿足高速數(shù)模混合電路電磁兼容方面的設計原則,以使系統(tǒng)性能更佳。

3.2 軟件設計

本系統(tǒng)的軟件設計采用Altera公司提供的E-DA設計工具Quartus II,主要包括兩個部分:首先是由Ouartus II集成的SoPC Builder工具生成Nios IICPU并進行相應的設置,用原理圖和HDL語言設計。FPGA的其他時序控制程序;其次是用Quarus II集成的Nios II IDE綜合開發(fā)環(huán)境為Nios II CPU編寫控制AD9858的程序,采用C/C++語言編寫,分為主程序模塊和中斷響應程序模塊。

因為本設計只采用片內(nèi)RAM作為Nios II(CPU的程序和數(shù)據(jù)存儲區(qū),所以在Nios II IDE綜合開發(fā)環(huán)境下前先對項目進行一些編譯設置,以使編譯器編譯出效率更高、占用空間更小的代碼。在用戶工程屬性對話框內(nèi)將Optimization Level設為“Opti-mize size(-Os)”,在系統(tǒng)庫工程屬性對話框內(nèi)也做同樣的設置,同時將Max file descriptors設為4,清除“Clean exit(flush buffers)”和“Link with profiling li-brary”前的選中框,選中“Reduced device drivers”和“Small C Library”。

AD9858有兩種工作模式:單頻模式和掃頻模式。單頻模式的配置比較簡單,只需將控制寄存器(CFR)、頻率調(diào)諧字(FTW)配置完畢,即可打開該功能。頻率掃描模式需要配置的寄存器有控制寄存器(CFR)、頻率調(diào)諧字(Frw)、增量頻率調(diào)諧字(DFTW)、增量頻率斜率控制字(DFRRW)和相位偏移字(POW)。其中,控制寄存器一共有4個字節(jié),地址分別為0x00、0x01、0x02和0x03。在本設計中,未用到PLL功能.故與PLL有關的控制字均置為無效。0x01的Bit7為掃頻使能位,將其置1打開掃頻功能。上電復位以后,Nios II CPU處于等待中斷狀態(tài),它根據(jù)FPGA的時序控制程序發(fā)出的中斷信號執(zhí)行相應的中斷響應程序,通過對各種寄存器賦值可產(chǎn)生線性調(diào)頻或相位編碼信號。

關于采用AD9858產(chǎn)生線性調(diào)頻信號還需進一步說明,其工作原理是:指定頻率起始點和步進頻率,頻率以系統(tǒng)時鐘的1/8或其整數(shù)倍累加,但是在沒有指定上限頻率的情況下,會一直掃到1/2參考時鐘頻率處,即奈奎斯特頻率,所以需要外部定時器控制何時停止頻率累加。通過FPGA的時序控制程序可以靈活地設定定時器,實現(xiàn)對上限頻率精確控制。

Nios II的中斷程序編程需要調(diào)用API函數(shù)alt_irq_register()向系統(tǒng)。ISR注冊用戶ISR。其原形為:

![]()

其中,id代表被服務的中斷向量號;context是運行參數(shù)指針,作為第一個參數(shù)傳給用戶。ISR;isr是函數(shù)指針。指向用戶。ISR入口。如果注冊成功,函數(shù)返回0,并允許全局中斷及被服務中斷;如果不成功則返回非0值。

用戶定義的用戶ISR程序要符合統(tǒng)一的原形定義,即:

![]()

其中,入口參數(shù)與返回值要嚴格按標準形式定義。否則系統(tǒng)ISR,將不能正確對其調(diào)用。

中斷程序的部分代碼如下:

4、 結束語

系統(tǒng)通過一片F(xiàn)PGA實現(xiàn)內(nèi)嵌CPU軟核控制外圍DDS,同時形成各種系統(tǒng)所需的同步控制時序。實驗證明其調(diào)頻性能和穩(wěn)定精度等各項指標均達到設計要求。SoPC是目前嵌入式系統(tǒng)設計的一個新趨勢,由于FPGA的可編程特性,可以在不改變?nèi)魏瓮鈬娐返那闆r下靈活地對系統(tǒng)進行重新配置,軟硬件升級。此外,還可以實現(xiàn)對Nios II CPU的RTOS操作系統(tǒng)的移植,以實現(xiàn)更豐富的功能和產(chǎn)生更為復雜的雷達波形,從而簡化雷達信號源的設計,提高系統(tǒng)的集成度。

責任編輯:gt

-

芯片

+關注

關注

459文章

52091瀏覽量

435366 -

控制器

+關注

關注

114文章

16933瀏覽量

182709 -

雷達

+關注

關注

50文章

3066瀏覽量

119311

發(fā)布評論請先 登錄

AD9858實現(xiàn)雷達寬帶調(diào)頻源設計

采用AD9858和AD4360_2實現(xiàn)UHF波段頻率合成系統(tǒng)的設計

基于EP2C8Q208C7和AD9858實現(xiàn)雷達信號源的應用方案

用DDS器件AD9858實現(xiàn)復雜雷達信號源 (圖)

EP2C8Q208C JTAG下載的奇怪現(xiàn)象,大家討論下

請問AD9858參考信號REFCLK是采用的何種方式提供的

采用AD9858實現(xiàn)雷達信號源的應用設計

回收EP2C8Q208C8N,收購EP2C8Q208C8N

DDS工作原理是?用DDS芯片AD9858寬帶雷達信號源要設計最佳?

如何利用AD9858設計雷達寬帶調(diào)頻源?

基于AD9858寬帶雷達信號源的設計及應用

DDS器件AD9858實現(xiàn)復雜雷達信號源

基于EP2C8Q208C和AD9858芯片實現(xiàn)雷達信號源的應用設計

基于EP2C8Q208C和AD9858芯片實現(xiàn)雷達信號源的應用設計

評論