轉(zhuǎn)自:EDN電子技術(shù)設(shè)計(jì)

總的來說疊層設(shè)計(jì)主要要遵從兩個(gè)規(guī)矩:

1. 每個(gè)走線層都必須有一個(gè)鄰近的參考層(電源或地層);

2. 鄰近的主電源層和地層要保持最小間距,以提供較大的耦合電容;

下面列出從兩層板到八層板的疊層來進(jìn)行示例講解:

一、單面PCB板和雙面PCB板的疊層

對于兩層板來說,由于板層數(shù)量少,已經(jīng)不存在疊層的問題。控制EMI輻射主要從布線和布局來考慮;

單層板和雙層板的電磁兼容問題越來越突出。造成這種現(xiàn)象的主要原因就是因信號回路面積過大,不僅產(chǎn)生了較強(qiáng)的電磁輻射,而且使電路對外界干擾敏感。要改善線路的電磁兼容性,最簡單的方法是減小關(guān)鍵信號的回路面積。

關(guān)鍵信號:從電磁兼容的角度考慮,關(guān)鍵信號主要指產(chǎn)生較強(qiáng)輻射的信號和對外界敏感的信號。能夠產(chǎn)生較強(qiáng)輻射的信號一般是周期性信號,如時(shí)鐘或地址的低位信號。對干擾敏感的信號是指那些電平較低的模擬信號。

單、雙層板通常使用在低于10KHz的低頻模擬設(shè)計(jì)中:

1)在同一層的電源走線以輻射狀走線,并最小化線的長度總和;

2)走電源、地線時(shí),相互靠近;在關(guān)鍵信號線邊上布一條地線,這條地線應(yīng)盡量靠近信號線。這樣就形成了較小的回路面積,減小差模輻射對外界干擾的敏感度。當(dāng)信號線的旁邊加一條地線后,就形成了一個(gè)面積最小的回路,信號電流肯定會(huì)取到這個(gè)回路,而不是其它地線路徑。

3)如果是雙層線路板,可以在線路板的另一面,緊靠近信號線的下面,沿著信號線布一條地線,一線盡量寬些。這樣形成的回路面積等于線路板的厚度乘以信號線的長度。

二、四層板的疊層

1. SIG-GND(PWR)-PWR (GND)-SIG;2. GND-SIG(PWR)-SIG(PWR)-GND;

對于以上兩種疊層設(shè)計(jì),潛在的問題是對于傳統(tǒng)的1.6mm(62mil)板厚。層間距將會(huì)變得很大,不僅不利于控制阻抗,層間耦合及屏蔽;特別是電源地層之間間距很大,降低了板電容,不利于濾除噪聲。

對于第一種方案,通常應(yīng)用于板上芯片較多的情況。這種方案可得到較好的SI性能,對于EMI性能來說并不是很好,主要要通過走線及其他細(xì)節(jié)來控制。主要注意:地層放在信號最密集的信號層的相連層,有利于吸收和抑制輻射;增大板面積,體現(xiàn)20H規(guī)則。

對于第二種方案,通常應(yīng)用于板上芯片密度足夠低和芯片周圍有足夠面積(放置所要求的電源覆銅層)的場合。此種方案PCB的外層均為地層,中間兩層均為信號 /電源層。信號層上的電源用寬線走線,這可使電源電流的路徑阻抗低,且信號微帶路徑的阻抗也低,也可通過外層地屏蔽內(nèi)層信號輻射。從EMI控制的角度看, 這是現(xiàn)有的最佳4層PCB結(jié)構(gòu)。

注意:中間兩層信號、電源混合層間距要拉開,走線方向垂直,避免出現(xiàn)串?dāng)_;適當(dāng)控制板面積,體現(xiàn)20H規(guī)則;如果要控 制走線阻抗,上述方案要非常小心地將走線布置在電源和接地鋪銅的下邊。另外,電源或地層上的鋪銅之間應(yīng)盡可能地互連在一起,以確保DC和低頻的連接性。

三、六層板的疊層

對于芯片密度較大、時(shí)鐘頻率較高的設(shè)計(jì)應(yīng)考慮6層板的設(shè)計(jì),推薦疊層方式:

1.SIG-GND-SIG-PWR-GND-SIG;對于這種方案,這種疊層方案可得到較好的信號完整性,信號層與接地層相鄰,電源層和接地層配對,每個(gè)走線層的阻抗都可較好控制,且兩個(gè)地層都是能良好的吸收磁力線。并且在電源、地層完整的情況下能為每個(gè)信號層都提供較好的回流路徑。

2.GND-SIG-GND-PWR-SIG -GND;對于這種方案,該種方案只適用于器件密度不是很高的情況,這種疊層具有上面疊層的所有優(yōu)點(diǎn),并且這樣頂層和底層的地平面比較完整,能作為一個(gè)較好的屏蔽層 來使用。需要注意的是電源層要靠近非主元件面的那一層,因?yàn)榈讓拥钠矫鏁?huì)更完整。因此,EMI性能要比第一種方案好。

小結(jié):對于六層板的方案,電源層與地層之間的間距應(yīng)盡量減小,以獲得好的電源、地耦合。但62mil的板厚,層間距雖然得到減小,還是不容易把主電源與地 層之間的間距控制得很小。對比第一種方案與第二種方案,第二種方案成本要大大增加。因此,我們疊層時(shí)通常選擇第一種方案。設(shè)計(jì)時(shí),遵循20H規(guī)則和鏡像層 規(guī)則設(shè)計(jì)。

四、八層板的疊層

1、由于差的電磁吸收能力和大的電源阻抗導(dǎo)致這種不是一種好的疊層方式。它的結(jié)構(gòu)如下:

1.Signal 1 元件面、微帶走線層

2.Signal 2 內(nèi)部微帶走線層,較好的走線層(X方向)

3.Ground

4.Signal 3 帶狀線走線層,較好的走線層(Y方向)

5.Signal 4 帶狀線走線層

6.Power

7.Signal 5 內(nèi)部微帶走線層

8.Signal 6 微帶走線層

2、是第三種疊層方式的變種,由于增加了參考層,具有較好的EMI性能,各信號層的特性阻抗可以很好的控制。

1.Signal 1 元件面、微帶走線層,好的走線層

2.Ground 地層,較好的電磁波吸收能力

3.Signal 2 帶狀線走線層,好的走線層

4.Power 電源層,與下面的地層構(gòu)成優(yōu)秀的電磁吸收 5.Ground 地層

6.Signal 3 帶狀線走線層,好的走線層

7.Power 地層,具有較大的電源阻抗

8.Signal 4 微帶走線層,好的走線層

3、最佳疊層方式,由于多層地參考平面的使用具有非常好的地磁吸收能力。

1.Signal 1 元件面、微帶走線層,好的走線層

2.Ground 地層,較好的電磁波吸收能力

3.Signal 2 帶狀線走線層,好的走線層

4.Power 電源層,與下面的地層構(gòu)成優(yōu)秀的電磁吸收 5.Ground 地層

6.Signal 3 帶狀線走線層,好的走線層

7.Ground 地層,較好的電磁波吸收能力

8.Signal 4 微帶走線層,好的走線層

對于如何選擇設(shè)計(jì)用幾層板和用什么方式的疊層,要根據(jù)板上信號網(wǎng)絡(luò)的數(shù)量,器件密度,PIN密度,信號的頻率,板的大小等許多因素。對于這些因素我們要綜 合考慮。對于信號網(wǎng)絡(luò)的數(shù)量越多,器件密度越大,PIN密度越大,信號的頻率越高的設(shè)計(jì)應(yīng)盡量采用多層板設(shè)計(jì)。為得到好的EMI性能最好保證每個(gè)信號層都 有自己的參考層。

-

pcb

+關(guān)注

關(guān)注

4351文章

23405瀏覽量

406615 -

工程師

+關(guān)注

關(guān)注

59文章

1587瀏覽量

69203 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4775瀏覽量

89139 -

疊層

+關(guān)注

關(guān)注

0文章

29瀏覽量

10054 -

可制造性設(shè)計(jì)

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15980 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3501瀏覽量

5230

發(fā)布評論請先 登錄

工程師應(yīng)該掌握的20個(gè)模擬電路

【華秋DFM】V4.6正式上線:工程師的PCB設(shè)計(jì)“好搭子”來了!

捷多邦專家解讀:如何選擇最優(yōu)PCB疊層方案?

硬件工程師手冊(全套)

Allegro工程師能力升級建議 工程師技能如何升級進(jìn)階

電子工程師的PCB設(shè)計(jì)經(jīng)驗(yàn)

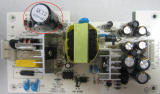

電子工程師的電源設(shè)計(jì)經(jīng)驗(yàn)

不同時(shí)期的硬件工程師,最怕發(fā)生的事 #電子工程師 #硬件工程師 #內(nèi)容過于真實(shí) #YXC晶振 #揚(yáng)興科技

談?wù)?b class='flag-5'>PCB工程師金字塔分級標(biāo)準(zhǔn)

工程師應(yīng)該掌握的幾種正確電容放電姿勢

工程師應(yīng)該掌握的PCB疊層設(shè)計(jì)內(nèi)容

工程師應(yīng)該掌握的PCB疊層設(shè)計(jì)內(nèi)容

評論