技術(shù)應(yīng)用雖然已經(jīng)開始,但哪一種技術(shù)路徑最好、誰家的最好仍不得而知。

經(jīng)過多年研發(fā),幾家晶圓廠設(shè)備供應(yīng)商終于在去年推出了基于原子層刻蝕(ALE)的下一代蝕刻系統(tǒng)。

ALE雖指向16 / 14nm的技術(shù)方向,但其必將在10 / 7nm甚至更遠的技術(shù)領(lǐng)域內(nèi)發(fā)揮重要作用。業(yè)界也正致力于開發(fā)應(yīng)用于先進邏輯處理器和存儲器生產(chǎn)制造的新一代ALE技術(shù)。

傳統(tǒng)蝕刻設(shè)備連續(xù)的無選擇的蝕刻晶圓,該系統(tǒng)在芯片制造商中已應(yīng)用多年。新一代蝕刻技術(shù)ALE有選擇地去除原子尺度上的目標(biāo)材料,而不會損壞結(jié)構(gòu)的其他部分,可以蝕刻出具有10?~15? 或5個原子寬度間隙的溝槽。 (1?=0.1nm)

現(xiàn)在業(yè)界正開發(fā)的幾種類型的ALE,正變得讓人困惑。基本而言,業(yè)界目前有以下方向發(fā)展:

1、ALE設(shè)備供應(yīng)商正在推出的蝕刻系統(tǒng)仍是基于各向異性等離子體蝕刻技術(shù)的ALE。

2、該行業(yè)現(xiàn)在專注于高溫ALE的開發(fā),這種ALE可以各向同性或單向的蝕刻。一些其他廠商也正使用一些不同的ALE方法進行各向同性蝕刻。

3、一些正在開發(fā)混合高溫等離子體ALE。

4、最終目標(biāo)是開發(fā)出有選擇性的ALE,可以有選擇性地去除表面上的單一類型材料或原子。

總而言之,等離子體ALE正協(xié)助各種芯片制造商實現(xiàn)更先進的生產(chǎn)制造。投資銀行Morningstar分析師Abhinav Davuluri表示:“目前,ALE仍處于早期階段。 我們優(yōu)先考慮在邏輯芯片領(lǐng)域和專業(yè)的代工廠里首先應(yīng)用,當(dāng)它逐漸發(fā)揮作用的時候,DRAM的性能就會一點點提升。”

ALE無法取代很多傳統(tǒng)蝕刻步驟,因為它在產(chǎn)能方面相對而言算是慢的。不過,傳統(tǒng)蝕刻無法完成的工作領(lǐng)域,ALE正獲得應(yīng)用。應(yīng)用材料公司蝕刻和掩膜策略方面的副總裁Uday Mitra說:“業(yè)界正在更多的向ALE過渡。隨著3D技術(shù)的發(fā)展,傳統(tǒng)蝕刻技術(shù)的限制越來越多。隨著更先進工藝節(jié)點的進入,我們將看到ALE更快的增長。”

Applied Materials, Hitachi High-Technologies, Lam Research , TEL是市場上ALE設(shè)備的主要供應(yīng)商。如今,ALE只占整個蝕刻設(shè)備市場的一小部分。研究機構(gòu)Gartner的數(shù)據(jù)顯示,全球干法蝕刻市場規(guī)模2017年將達到96億美元,高于2016年的72億美元。

ALE到底是什么?

蝕刻,從晶圓上去除材料以形成圖形特征的工藝步驟,分為濕法和干法兩大類。濕法蝕刻使用液體化學(xué)物質(zhì)去除材料。干法蝕刻通過等離子體轟擊晶圓面上的物質(zhì)來去除材料,市場占比更大。

數(shù)十年來,芯片制造商在工廠中使用了被稱為反應(yīng)離子刻蝕(RIE)的干法刻蝕技術(shù)。RIE中提到的等離子體(plasma)是由部分電子被剝奪后的原子及原子團被電離后產(chǎn)生的正負離子組成的離子化氣體狀物質(zhì),尺度大于德拜長度的宏觀電中性電離氣體,其運動主要受電磁力支配,并表現(xiàn)出顯著的集體行為。它廣泛存在于宇宙中,常被視為是除去固、液、氣外,物質(zhì)存在的第四態(tài)。等離子體是一種很好的導(dǎo)電體,利用經(jīng)過巧妙設(shè)計的磁場可以捕捉、移動和加速等離子體。當(dāng)被加熱到足夠高的溫度或其他原因,外層電子擺脫原子核的束縛成為自由電子,就像下課后的學(xué)生跑到操場上隨意玩耍一樣。電子離開原子核,這個過程就叫做“電離”。這時,物質(zhì)就變成了由帶正電的原子核和帶負電的電子組成的、一團均勻的“漿糊”,因此人們戲稱它為離子漿,這些離子漿中正負電荷總量相等,因此它是近似電中性的,所以就叫等離子體。

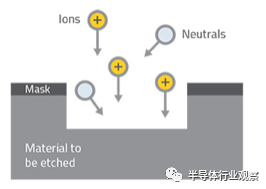

圖1:傳統(tǒng)等離子刻蝕工藝 來源:Lam Research

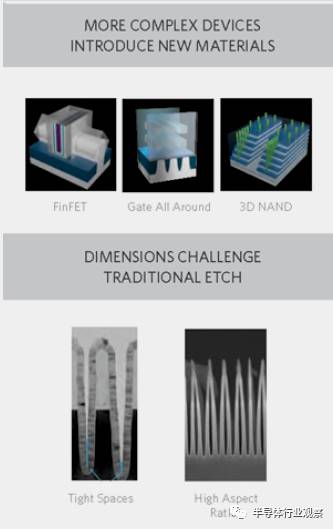

RIE設(shè)備雖快速可靠,但挑戰(zhàn)仍存。首先,芯片制造商必須處理那些很小甚至沒有空間的微小功能。如據(jù)Lam所說,一個晶體管柵極結(jié)構(gòu)可能是10nm寬,制造中只允許在1nm范圍內(nèi)變化。

然后,傳統(tǒng)蝕刻設(shè)備中電極在高溫高壓下激發(fā)等離子體轟擊晶片,這對于微小的結(jié)構(gòu)制造很有效,但也有可能會損壞結(jié)構(gòu)。因此,不論是對于這種結(jié)構(gòu)還是其他某種結(jié)構(gòu),需要有選擇性地去除目標(biāo)材料而不損壞其他部分。

那這就是ALE應(yīng)用的場景。應(yīng)用材料的Mitra認為:“ALE有兩個基本條件:一是它以自我限制的方式去除單個原子層;二是它不會觸及和破壞底層和周圍的材料。”

自20世紀80年代以來,ALE的研發(fā)一度停滯過幾年。它是一個一直在尋找適合應(yīng)用場景的技術(shù)。但在過去的一兩年里,ALE市場開始升溫。 Applied,Lam,TEL等設(shè)備制造商在市場上推出了第一批基于ALE的蝕刻系統(tǒng)。

最后,芯片制造商發(fā)現(xiàn)了未來生產(chǎn)對ALE的需求。 Lam Research高級副總裁兼技術(shù)研究員David Hemker在最近的一次活動中表示:“ALE是使某些集成工藝步驟能夠在7nm和5nm進行蝕刻的唯一方式,而且我們看到ALE將會越來越多地被應(yīng)用。”

ALE正在應(yīng)用于一些特定的領(lǐng)域。TEL公司技術(shù)開發(fā)和工藝工程高級總監(jiān)Peter Biolsi說:“目前ALE在兩個主要領(lǐng)域得到應(yīng)用,一是那些間距或者空間商非常緊密的可能發(fā)生孔洞“堵塞”的蝕刻,二是具有超高選擇性和均勻性應(yīng)用。”

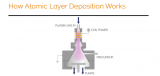

在技術(shù)方面,ALE與原子層沉積(ALD)也有關(guān)系。ALD的原理是反應(yīng)物先被泵入腔室鋪滿表面,然后清除化學(xué)物質(zhì)并重復(fù)該過程,從而一次形成單原子層的單層材料。

ALD是一個緩慢的過程,但是技術(shù)應(yīng)用幾年前就已經(jīng)開始。如今,ALD應(yīng)用于邏輯芯片制造中高K值金屬柵極的堆棧、DRAM中的電容成型及多重掩膜化。

相比之下,ALE與ALD相反。 ALE以一種自我限制且有序的方式在原子尺度逐層去除材料。

ALE可以匹配不同的應(yīng)用場景,可以是在現(xiàn)有蝕刻設(shè)備配備具有針對性的ALE腔室也可以是專用ALE系統(tǒng)。

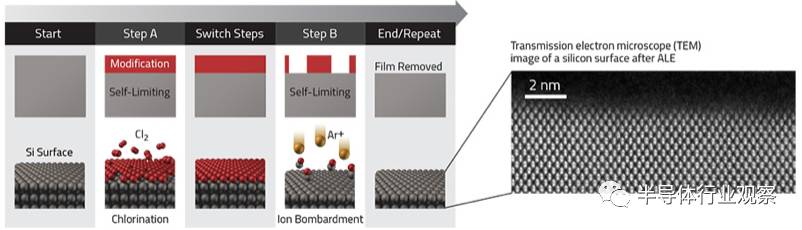

但不管如何匹配,ALE過程都涉及到復(fù)雜的物理化學(xué)反應(yīng)。在Lam提供的事例中,ALE腔內(nèi)注入氯氣,氯分子被吸收到表面形成氯化層,從腔室中除去未反應(yīng)的氯氣,然后注入氬離子轟擊晶圓,除去薄氯化層不需要的部分。

圖2:ALE工藝循環(huán) 來源:Lam Research

還有其他通過大量材料組合來實現(xiàn)ALE的方法。那么最好的是什么呢?

TEL的Biolsi說:“我們覺得沒有最好的辦法,我們需要具備使用所有方法的能力,以最好地適應(yīng)所要蝕刻的材料和應(yīng)用場景。”

盡管可能有多種分類方法,但根據(jù)科羅拉多大學(xué)化學(xué)與生物化學(xué)系教授Steven George的說法,ALE可分為兩大——等離子體ALE和高溫ALE。當(dāng)然也有試圖結(jié)合兩種技術(shù)的高溫等離子體ALE技術(shù)。

等離子ALE和高溫ALE適用于不同類型的蝕刻,盡管在某些相同的過程中它們是一起使用的 。George說:“ALE方面,等離子體ALE使用高能離子或中性物質(zhì)從表面上剔除物質(zhì)的方法來進行蝕刻;而高溫ALE應(yīng)用于特定的高溫氣相反應(yīng)。”

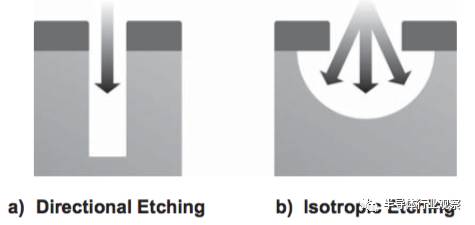

長時間以來,等離子體ALE一直在生產(chǎn)中應(yīng)用。通常是等離子體ALE進行各向異性或定向蝕刻,相反的,高溫ALE執(zhí)行各向同性或單向蝕刻。

“等離子ALE是定向的。例如,如果您需要鉆一個孔,則需要等離子體來完成該操作。等離子體ALE或等離子體處理一般可以做到的事情,你無法用高溫ALE的方式來完成。”George說。

等離子體ALE具有有限的各向同性能力。他解釋說:“被加速的等離子體是有方向性的,而且等離子體也可以產(chǎn)生其他諸如自由基一類的物質(zhì)。這些自由基也來自等離子體源,它們的運動有一定范圍,不會四處游走。”

相反,高溫ALE針對更具挑戰(zhàn)的各向同性蝕刻。高溫只是一種各向同性蝕刻方法,但并不唯一。有些廠家正在使用更加激進的方法。

圖3:定向蝕刻(a)垂直方向的蝕刻速率遠大于橫向的蝕刻速率,以及各向同性蝕刻(b),其在所有方向上以相同的速率蝕刻材料。來源:Lam Research。

對于各向同性蝕刻,ALE設(shè)備會發(fā)出可以在任何地方傳播的氣體分子。所以蝕刻發(fā)生在氣體分子存在的任何地方。 George說“這些氣體分子對于原有體系來說是活躍的新物質(zhì),就像新闖入一個街區(qū)的小孩,吸引著所有人的注意,這就讓高溫ALE具備一些等離子體ALE所不具備的潛在能力。高溫ALE的互補性使它可以讓你決定如何蝕刻而不需要特定材料。這是一個大問題。”

高溫ALE不會取代等離子體ALE,反之亦然。芯片制造商可以使用兩者來完成不同的任務(wù)。

同時,一些研究機構(gòu)正在開發(fā)高溫等離子體ALE技術(shù)。“這樣就可以獲得一些高溫ALE的優(yōu)點和等離子體方向性上的優(yōu)勢。” George說。

混合技術(shù)仍然在研發(fā)當(dāng)中。等離子ALE已經(jīng)應(yīng)用與生產(chǎn)中,但高溫ALE仍處于早期階段,必須在更廣泛的材料上進行實驗。

然后,不管用何方法,對于ALE的各向異性和各向同性蝕刻都有一些挑戰(zhàn)。據(jù)埃因霍溫科技大學(xué)(EIT)應(yīng)用物理系教授Erwin Kessels介紹,對于各向異性的ALE,挑戰(zhàn)在于維持自我限制機制,這要求精確控制離子能量和工藝條件。

各向同性的ALE更具挑戰(zhàn)性。Kessels說:“我一直在說每個人都想要各向同性,但是還沒有人知道如何去做。開發(fā)各向同性的ALE工藝是一個挑戰(zhàn)。”

通常,高溫ALE利用氣相反應(yīng)來實現(xiàn)各向同性的蝕刻。其他人正在使用不同的方法獲得相同的結(jié)果。

例如,利用其專用的ALE設(shè)備,應(yīng)用材料公司使用它所認為的先進工藝(radical-based)來進行各向同性蝕刻,通過兩個步驟實現(xiàn),首先進行表面特殊化處理,然后基于自由基的蝕刻方法去除目標(biāo)材料。

Applied的Mitra說:“我們不需要繼續(xù)加熱,因為(radical-based)工藝溫度更高,這種方法選擇性非常高。它可以蝕刻一種材料而不接觸另一個表面。”

EIT的Kessels在解釋這個特定的過程時說:“這就是我們所說的各向同性蝕刻過程,它是由自由基驅(qū)動的。所以,你可以用它做各向同性的蝕刻工藝。根據(jù)晶圓上的材料組合,您可以以極佳的選擇性做到這一點。”

總之,ALE實現(xiàn)了廣泛的應(yīng)用。以下是各向異性和各向同性的一些對比:

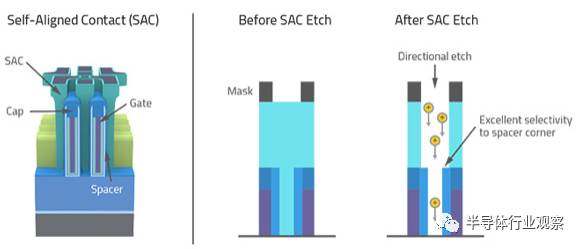

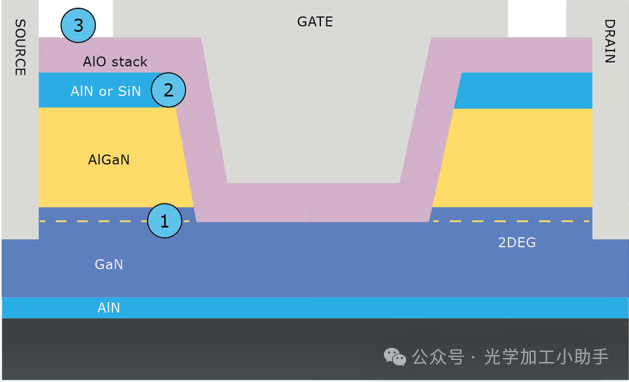

1、晶體管結(jié)構(gòu):目前,ALE正在生產(chǎn)中用于創(chuàng)建自我匹配的連接 (見下面圖3)

2、極紫外光刻:ALE將被用作平滑技術(shù)來解決由EUV掩膜版引起的線邊緣粗糙度問題,ALE也是針對類似應(yīng)用而設(shè)計的。

3、全柵極FET:全柵極(GAA)是一種finFET,其側(cè)面上具有柵極纏繞的,未來可能出現(xiàn)在5nm工藝中。

圖4:自對準接觸的ALE工藝。來源:Lam Research

GAA流程的第一步是制作由硅鍺(SiGe)和硅(Si)交替層組成的超晶格結(jié)構(gòu)。在工藝過程中,硅鍺層必須被去除而不接觸硅層。對于這個工藝流程,ALE是唯一的方法。

圖5:使用ALE的原因。資料來源:應(yīng)用材料

ALE的下一步是什么?

綜上,ALE正在生產(chǎn)中應(yīng)用。但是它未來仍會在業(yè)界取得什么重大的進展?

現(xiàn)在得出討論還為時過早。ALE仍處于起步階段,邏輯芯片廠和代工廠是16nm / 14nm/ 10nm的首批采用者。晨星公司的Davuluri說:“10nm工藝下,ALE主要用于形成接觸。未來最有可能的情況,是當(dāng)我們轉(zhuǎn)向7nm,5nm和3nm工藝時,它將主要應(yīng)用于晶體管成型。”

但是和以前一樣,ALE也有一些挑戰(zhàn) - 成本和產(chǎn)能。他說:“與ALE提高的精確性和準確性相伴,成本也是極高的,工藝流程中的工藝時間和步驟周期,都比一些更傳統(tǒng)的蝕刻方法要大得多。

這將限制英特爾,臺積電和三星采用ALE。他說:“除了絕對必要的地方之外,他們會試圖限制使用AIE。那是一些需要絕對完美的蝕刻的地方。”

還有其他因素。例如,據(jù)報道英特爾在10納米的某些步驟使用ALE。最初英特爾的10nm工藝本來應(yīng)該在今年年底量產(chǎn)。他說:“取代年底量產(chǎn)計劃的,是2018年全面實施。”

考慮到這些問題,ALE市場的總體規(guī)模是一個動態(tài)的目標(biāo)。根據(jù)晨星公司的數(shù)據(jù),目前ALE的業(yè)務(wù)介于5000萬美元到1億美元之間。他說:“這是一個相當(dāng)樂觀的估計,到2020財年,包括ALE在內(nèi)的選擇性蝕刻將具有4.5億美元的市場。”

實際上,應(yīng)用材料公司銷售兩套ALE系統(tǒng)。第一個設(shè)備(Sym3)是一個通用的蝕刻系統(tǒng)。它可以匹配各向異性蝕刻的等離子體ALE,例如自對準接觸和基底間隔物成型。

應(yīng)用材料的Mitra說:“你可以在現(xiàn)有的反應(yīng)腔體里做ALE。通過正確的控制做快速切換和脈沖,升級現(xiàn)有的反應(yīng)腔體。ALE最大的缺點是很慢,關(guān)鍵是如何將反應(yīng)物快速移出。所以你需要一個電導(dǎo)率非常好的反應(yīng)腔體。“

第二個設(shè)備(Selectra)是專門用于各向同性應(yīng)用的ALE系統(tǒng)。“在選擇性蝕刻領(lǐng)域,我們是唯一有設(shè)備能力的公司。”米特拉說。

邏輯芯片是第一個應(yīng)用,但不是唯一的。 Mitra說:“雖然各向異性現(xiàn)在有更多的應(yīng)用,但各向同性蝕刻適應(yīng)新的應(yīng)用和變化。它使客戶能夠解決新的問題,特別是當(dāng)客戶正在越來越多的向3D制程進軍時。如果你看一下3D NAND結(jié)構(gòu),就知道為了深入到結(jié)構(gòu)中進行蝕刻,就可能需要橫向蝕刻。這是傳統(tǒng)的蝕刻系統(tǒng)無法做到的一點。“

然后,在研發(fā)方面,應(yīng)用材料正在為ALE開發(fā)下一代電子束等離子設(shè)備。電子束在腔室中產(chǎn)生等離子體,得到更低的電勢(0.3eV)和離子能量(<2eV)。Mitra說:“這是才真正的原子控制,電子束是用來產(chǎn)生電勢很低的離子。”

電子束ALE仍處于尋路階段。 Mitra說:“你可以用它來做一些奇特的事情。對于接下來的兩三個節(jié)點,我認為你不需要像電子束源那樣的東西。”

所以公司當(dāng)前的ALE設(shè)備可以為未來的兩到三個節(jié)點做好工作。展望未來,目前設(shè)備的目標(biāo)是提高能力和產(chǎn)能。

與此同時,Lam Research發(fā)布了一個具有定向ALE功能的刻蝕系統(tǒng)。現(xiàn)在,Lam正研究在最新的設(shè)備型號(Kiyo和Flex)中應(yīng)用新的定向ALE技術(shù)。

Lam公司蝕刻產(chǎn)品副總裁Thorsten Lill表示:“我們看到ALE可以應(yīng)用的節(jié)點數(shù)量不斷增加,大多數(shù)關(guān)鍵的蝕刻需要方向性,因此定向ALE值得被關(guān)注。”

像應(yīng)用材料一樣,Lam也看到了對各向同性ALE的需求。 Lill說:“垂直器件集成驅(qū)動了對各向同性蝕刻的需求,未來將有必要增加各向同性ALE蝕刻技術(shù)”。

同時,TEL銷售傳統(tǒng)的蝕刻產(chǎn)品以及ALE氣體化學(xué)蝕刻系統(tǒng)(Certas)。TEL的Biolsi說:“TEL已經(jīng)采用各向異性和各向同性的ALE方法進行硅的電介質(zhì)蝕刻和各向異性蝕刻。硅的各向同性ALE仍在改進之中。

晶圓廠設(shè)備供應(yīng)商正在忙于研究不同的ALE方法。該技術(shù)正在被用于有針對性的場景,但是隨著時間的推移,該技術(shù)還將與ALD技術(shù)一起應(yīng)用。

ALE也將在一個名為選擇性沉積的新興領(lǐng)域發(fā)揮作用。將新型化學(xué)品與ALD相結(jié)合,選擇性沉積涉及在確切位置沉積材料和薄膜的工藝。

CU的George說:“ALE將與原子層沉積相輔相成,你可以用ALD控制薄膜。然后使用ALE,就能夠以相輔相成的方式去除材料。”

選擇性ALE是另一項需要關(guān)注的技術(shù)。當(dāng)前的ALE技術(shù)條件下,設(shè)備可以去除目標(biāo)結(jié)構(gòu)。選擇性ALE更進一步,仍然在研發(fā)中。George說:“想象一下你有一個基板或設(shè)備,表面上有許多不同的材料。 當(dāng)你想蝕刻所有的氧化鉿或者蝕刻所有的硅。為了做到這一點,控制將是非常重要的。”

芯片制造商仍在探索ALE的所有可能性。這項技術(shù)還處于起步階段,目前正在整合中。 EIT公司的Kessels說:“蝕刻,表面處理或者沉積技術(shù)的組合將會誕生許多混合工藝,我們正站在原子尺度制造工藝的開端。”

-

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

436006 -

等離子體

+關(guān)注

關(guān)注

0文章

128瀏覽量

14477 -

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4775瀏覽量

89161 -

原子

+關(guān)注

關(guān)注

0文章

89瀏覽量

20551 -

可制造性設(shè)計

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15982 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3501瀏覽量

5235

發(fā)布評論請先 登錄

原子層沉積(ALD)制備高透光摻鈮SnO?電子傳輸層(ETL)實現(xiàn)高效鈣鈦礦太陽能電池

詳解原子層沉積薄膜制備技術(shù)

GNSS馴服銣原子頻標(biāo)基準頻率源介紹

想做好 PCB 板蝕刻?先搞懂這些影響因素

蝕刻基礎(chǔ)知識

原子層沉積(ALD, Atomic Layer Deposition)詳解

芯片濕法蝕刻工藝

原子結(jié)構(gòu)模型及特點 原子的組成及結(jié)構(gòu)解析

AUTOSAR通信組件介紹 AUTOSAR通信層功能分析

濕法蝕刻的發(fā)展

關(guān)于原子層蝕刻的分析和介紹

關(guān)于原子層蝕刻的分析和介紹

評論