目前,幾個晶圓廠工具供應商正在推出新一代自對準圖案化技術,以向10 nm/ 7nm及以上的新器件演進。

應用材料、Lam Research和INTEL正在開發基于各種新方法的自對準技術。最新的方法涉及采用多色材料方案的自對準圖案化技術,該技術旨在用于在邏輯晶體管本身內開發新的finFET和結構。也有其他公司正在開發下一代晶體管和存儲器的新方案。

用于形成邏輯和存儲器的自對準圖案化技術屬于半導體制造中“圖案化”的通用范疇。 圖案化是在芯片上開發微小特性和圖案的“藝術”。 其他技術也屬于寬泛的“圖案化”部分,例如極紫外( EUV )光刻和光學光刻等。

幾年前開發的自對準技術,利用各種工藝步驟來確保結構彼此正確對齊。 一般來說,新的自對準技術分為兩個部分 - 多重構圖 ,以及自對準接觸/過孔和其他結構。有人對第二部分使用不同的名稱。 Imec將其稱為“縮放增強器”,而應用材料公司將其稱為“材料使能縮放”。

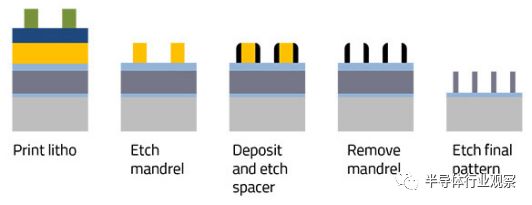

在多重圖案化中,其思路是在工廠中使用一系列工藝步驟來縮放芯片的特征尺寸。 最著名的例子是自對準雙重圖案(SADP)和自對準四重圖案(SAQP)。

除了多重圖案化之外,芯片制造商還使用不同的自對準技術來開發晶體管內部的各種結構,例如接觸和過孔。 業界將這些結構稱為自對準接觸和過孔。

舉一個例子, Intel最近推出了10nm finFET技術。 采用自對準技術,英特爾在finFET內部集成了有源柵極(COAG)結構的觸點。有其他公司正在開發完全自對準的過孔和相關結構。

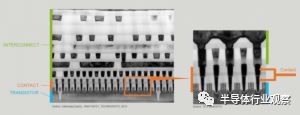

圖1:標準觸點與有源柵觸點。 來源:英特爾

這些經常被忽視的技術正變得越來越重要。 “像COAG這樣的自對準結構是縮放的關鍵,”英特爾高級研究員兼過程架構與集成總監Mark Bohr表示。“英特爾和行業內的其他廠商過去都采用了自對準功能,如自對準接觸和自對準過孔,這些功能都需要實現縮放。”

自對準技術在工廠中使用各種工藝步驟,例如沉積、蝕刻和光刻。 其他方案更多的是以新的材料組合沉積/蝕刻為中心,根據設備而有所不同。 在圖案化領域還有其他選擇,包括直寫電子束、定向自組裝、EUV、光刻和納米壓印。

但為了幫助行業在自對準技術領域走在前列,半導體工程公司正在緊跟、研究多模式圖案、接觸/過孔和未來方案的趨勢。

轉向多重模式

該過程從光掩膜設施開始。 在這個流程中,芯片制造商設計一個IC,將其轉換成文件格式,然后,基于該格式開發光掩膜。

光掩膜是給定IC設計的主模板。 掩膜開發后,它被運送到工廠并放置在光刻掃描儀中。

然后,將晶圓放置在掃描儀中的獨立臺上,晶圓上涂有光敏材料,稱為光刻膠。 掃描儀通過掩膜投影光線,在晶圓上形成微小圖像。

多年來,傳統光刻是一個簡單的過程。 光刻掃描儀使用單次曝光對晶圓上的特征進行成像。 這或多或少是單一模式的過程。 長期以來,業界認為傳統的光刻系統將持續到45nm左右。 理論上,最新的光學技術--193nm波長光刻技術 - 應該以80nm線寬或40nm半線寬達到其物理極限。然后,在45nm處,芯片制造商應該轉向極紫外(EUV)光刻技術,EUV使用13.5nm波長,在納米尺度上圖案化特征。

然而,EUV的開發比以前想象的更復雜,并且技術已經被推遲。 現在,EUV的目標是7nm和5nm。 由于延遲,業界開發了另一種解決方案,即通過多重圖案化技術來延長當今的193nm波長光刻技術。

從單一模式轉向多重模式并不容易。 多年來,該行業在光掩膜上使用了光學鄰近校正(OPC)技術。 OPC使用微小形狀或次分辨率輔助功能(SRAF)。SRAF被放置在掩膜上,這改變了掩膜圖案,從而改善了晶圓上的可印刷性。

然而,在20nm處,SRAF在掩膜上變得太密集,使得在晶圓上印刷可辨別的特征更加困難,而這正是適合使用多重圖案化的地方。

“在多重圖案化中,原始掩膜的形狀被劃分為兩個或更多,使得每個形狀在其周圍具有足夠的空間,以使得OPC操作能夠使其可印刷,” 西門子Mentor的DFM項目主管David Abercrombie在博客中說: “然后將每個掩膜分開打印,最終將整套原始形狀成像到晶圓上。”

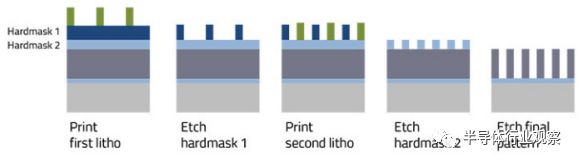

從22nm/ 20nm開始,芯片制造商采用兩步法在晶圓廠實施了各種多重構圖方案。 第一步是使用193nm光刻和多重圖案在晶圓上構圖微小線條。然后,線條被切割成小而復雜的圖案。

對于這些產品線,該行業借鑒了存儲器行業中使用的技術 - SADP和SAQP。 SADP / SAQP使用光刻步驟,以及附加的沉積和蝕刻步驟來定義間隔物狀特征。 使用SADP / SAQP,芯片制造商可以將線寬擴展到40nm以上。

然而,這里有一個很大的挑戰,就是將這些線條切成小圖案。 為此,一些芯片制造商使用SADP和SAQP。

還有廠商使用雙重圖案化,這可以將線寬減少30%。 這個過程使用光刻和蝕刻來定義單個層。 這也被稱為光刻 - 蝕刻 - 光刻 (LELE)。還有廠商使用三重圖案化,這需要三次曝光和蝕刻步驟(LELELE)。

圖2:自對準墊片避免了掩膜錯位。 來源:Lam Research

圖3:雙重圖案增加密度。 來源:Lam Research

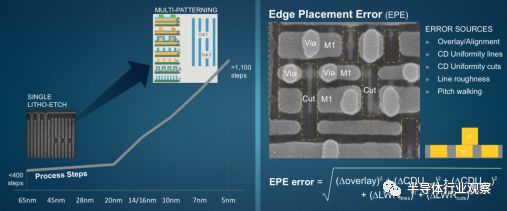

多次構圖延長了IC的縮放比例,但同時也增加了復雜性。 首先,每個節點都有更多的流程步驟,這會轉化為時間和成本。

設備功能在每個節點處變得更弱,這使問題更加復雜。 最重要的是,這些功能必須精確并且放置在設備每層的確切位置上。 28nm器件具有40到50個掩膜層。 相比之下,14nm / 10nm器件具有60層,并且該數量在7nm處預計會上升至80至85層。

總而言之,每個節點的挑戰都在增加,這就增加了在這個過程中出現錯誤的可能性。 “我們可以通過乘法來制作更小的特征。 但將它們相對放置,是一個根本挑戰。當您正嘗試將多個圖層彼此疊加時,可能會出現錯誤,“ 應用材料公司圖案化技術總監Regina Freed表示。

在圖案化處理中,目標是在精確的位置上設置微小的特征。 如果這些不精確,會導致不能對準,這通常稱為邊緣放置誤差(EPE)。

EPE是IC布局的預期功能和打印功能之間的差異。 如果在生產流程中出現一個或多個EPE問題,則該設備會出現短路或收益率低下的情況。

EPE由數值表示,簡而言之,EPE等同于各種度量的組合 - CD均勻性、覆蓋度、線邊緣粗糙度(LER)和變化。

圖4:多重構圖過程和EPE挑戰。 來源:應用材料公司

有些流程可以輕松滿足所需的EPE數值或預算, 但有時,更難的流程可能會超過EPE的目標水平,這將導致收益率下降。

解決方案

所以,對于10nm / 7nm及更高工藝節點來說,什么是最好的圖案化解決方案? 哪一個會符合EPE的目標呢?

沒有單一的解決方案可以滿足所有需求。 與以前一樣,芯片制造商根據復雜性、成本和其他因素選擇特定的制造技術。

應用材料的Freed說:“以某種分辨率獲取圖案有多種方式,會有很多不同的選擇。 你可以做SAQP,可以使用EUV /雙重圖案化,可以進行EUV光刻蝕刻 - 光刻蝕刻。 每個選項都有其優點和缺點。 客戶可以綜合使用這些技術。”

EUV是一種可能性,因為它有望減少流程中的步驟。 DSA , 多光束和納米壓印也是可能的。

自對準是另一種解決方案。 這些技術與其他晶圓廠工具協同工作,以幫助對齊特征。 例如,EUV可以與SADP / SAQP方案結合,用于多重圖案化。

一般來說,該行業已經將今天的自對準技術擴展到10nm / 7nm,而使用傳統方法變得具有挑戰性。 “隨著行業進入高級節點,與尺寸縮放相關的處理挑戰變得越來越重要,” INTEL高級工藝工程師Eric Liu在最近的SPIE會議上發表的一篇論文中表示。

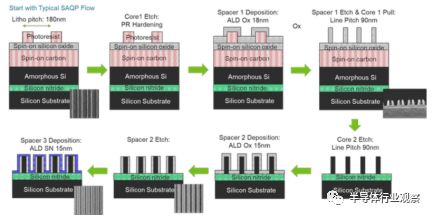

在這篇論文中,INTEL描述了一種新的SAQP方法,用來執行30nm線寬的線切割。 “線切割步驟中最具挑戰性的模式是單線切割,且要求沒有缺陷形成,”Liu說。

為此,INTEL使用多色材料設計了SAQP(這與用于多重圖案化的多色掩膜布局不同。)

傳統上,在SADP / SAQP中,流程涉及各種步驟和不同的材料,通常,每種材料具有相同的顏色。 問題在于,當使用傳統方法以30nm線寬進行線切割時,INTEL計算出EPE預算超過了7.9nm的目標值。

INTEL的新方法是遵循具有各種光刻、沉積和蝕刻步驟的標準SAQP流程。 但是在這種方法中,基于蝕刻選擇率,每種材料被分配不同的顏色,例如,該過程需要兩條不同的生產線, 每條線都分配有不同的顏色,掩膜板被分配不同的顏色。

圖5:從光刻到隔離層3沉積的2L1C的分步多色工藝流程。 來源:INTEL

簡而言之,顏色可以作為流程中的指導,從而實現更精確的特征。 “如果用不同的材料制作長線條/空間圖案中的其他線條,并且這些材料具有不同的蝕刻速率,則可以在蝕刻工藝中切割一條線條,而不用擔心相鄰線條是否因錯位而損壞裁剪圖案“,Fractilia的首席技術官Chris Mack在博客中解釋說。

盡管如此,總體而言,多色彩多重圖案化方法仍然需要權衡。 “ Lam Research技術總監Richard Wise表示:”我們已經將測試架構作為邏輯應用研發活動的一部分,通過構建具有不同顏色(材料)的線條,隨機放置切割工藝可以使用選擇性蝕刻工藝自動對準底層線條。 這可以有效地將這些削減的覆蓋裕度加倍或更多。“

但是它增加了更多的工藝步驟和成本。 “只有在使用標準晶圓廠技術無法滿足覆蓋預算的情況下,這些解決方案才是必需的,而且在復雜性、成本和設計方面的權衡具有較強的成本敏感性,”Wise說。 “在產品中采用需要權衡,用于自對準的多色SAxP以犧牲工藝復雜性/成本和設計靈活性為代價提高了疊加效果。 然而,設計仍然是個挑戰。 在這一點上,業界專注于使用其他不需要這些權衡的技術改進產品覆蓋。“

總而言之,具有多色技術的SADP / SAQP不是唯一的選擇,但它們確實給客戶提供了更多選擇。

觸點和過孔

領先的芯片由三部分組成 - 晶體管、觸點和互連。晶體管由源極,柵極和漏極組成。

位于晶體管頂部的互連由微小的銅布線組成,這些布線將電信號從一個晶體管傳輸到另一個晶體管。 通常情況下,芯片可能具有10到15個級別的銅互連,這些互連使用過孔連接。

晶體管連接和互連通過一個微小的觸點實現,觸點是具有小間隙的3D結構,其縫隙里充滿了鎢。

圖6:各個節點處的互連、觸點和晶體管。來源:應用材料。

直到最近,芯片制造商在觸點和過孔方面幾乎沒有問題。 以觸點為例。 在大多數芯片中,一個柵極位于兩個觸點之間。 在90nm處,從一個觸點到另一個接觸點的長度約為200nm。 但是到了22nm時,器件的尺寸縮小到了觸點很小的地方。

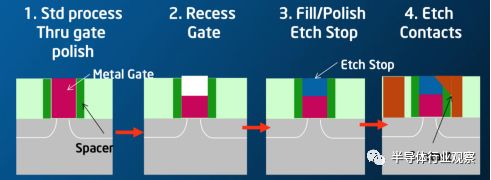

為了解決這個問題,芯片制造商轉向自對準的連接方案。 例如,在22nm處,英特爾將觸點放置在柵極旁邊。 使用自對準方案,金屬柵極凹陷。根據英特爾的說法,氮化硅蝕刻停止層被放置在金屬的頂部,觸點用鎢填充。

圖7:22nm自對準接觸。 來源:英特爾

實際上,自對準接觸使芯片制造商能夠在設備上填充更多結構,這一舉措提高了總體面積縮放比例。

在10nm時代,英特爾又向前邁進了一步。 它將觸點放置在有源柵(COAG)上。 采用不同的自對準工藝,英特爾使用碳化硅材料作為蝕刻停止層。 另外,鈷取代了鎢,以降低線路電阻。

還有其他一些例子,例如完全對齊。 多年來,該行業已經使用damascene般的流程進行接觸和過孔。 在接觸和過孔中,使用193nm浸入式和多圖案技術,可以在表面上形成孔洞,用蝕刻機鉆一個小孔,然后,排好洞并填充不同的材料。

在先進的節點上,芯片制造商面臨幾項挑戰,首先,這些結構與多重模式(如EPE)具有相同的挑戰;每個節點上的觸點和過孔變得越來越小,越來越難以制作。

因此,為了圖案化接觸孔和通孔,芯片制造商希望從193nm光刻切換到7nm / 5nm的EUV。 結構的其他部分也需要更復雜的制造技術。應用材料公司蝕刻和圖案化戰略副總裁Uday Mitra說:”在過去的美好時代,EPE的利潤率很高,現在它不再只是簡單的縮放。實際上是把觸點放在柵極上,這就像3D縮放。“

COAG和完全自對準過孔是晶體管內部復雜的類3D模塊。 許多類似3D的結構更多地依賴于沉積、蝕刻和新材料。 Gartner半導體和電子產品研究總監Gaurav Gupta說:“基本上,光刻一直是縮放的主要驅動因素,但對于3D設備,當你試圖縮放時,它不僅僅是光刻,蝕刻和沉積變得更加重要。“

為了實現這樣的結構,供應商開發了一系列工具、材料和流程。 “采用自對準方案的一種方法是使用多種材料,選擇性蝕刻,選擇性去除和CMP,”Applied的Mitra說。 “你要盡可能使用標準材料。”

還有利用多色材料的自對準技術。“整個世界正在朝這個方向發展,不只是光刻或EUV。有或沒有EUV,都需要自我對準的方案。 你需要材料使能的圖案化處理,”他說。

例如,應用材料公司稱之為“材料使能的縮放”。材料使能的縮放并不完全是一個新技術市場,它基本上是當前自對準技術的演變。 “你仍然必須使用自對準結構,需要不同材料的組合,處理步驟的順序可能會有所不同。 這是一個由材料解決的圖案化問題,而不是經典的光刻收縮或覆蓋,“他說。

下一步怎么走?

還有更多方案。 應用材料和其他公司正在研究一種稱為選擇性沉積的技術,使用原子層沉積工具,選擇性沉積是一個在確切位置沉積材料和膜的過程。

選擇性沉積仍處于研發階段。 隨著時間的推移,這些技術有望促進各種新設備發展。 Gartner公司的Gupta表示:“對于材料驅動的縮放,新材料將用于制造Ge / III-V,納米線、石墨烯、VFET和TFET。

鍺(Ge)和III-V材料是下一代晶體管的目標材料。 納米線、垂直FET(VFET)和隧道FET(TFET)是下一代晶體管類型。

顯然,自對準方案將支持新器件,并為IC縮放提供急需的推動力。 如果沒有這些創新,摩爾定律可能很難演進。

-

芯片

+關注

關注

459文章

52452瀏覽量

439963 -

摩爾定律

+關注

關注

4文章

639瀏覽量

79837 -

晶體管

+關注

關注

77文章

10013瀏覽量

141457

發布評論請先 登錄

是德示波器 MSO 與 DSO 的區別以及如何選擇

永磁體磁角度偏差對電機性能影響的分析

N9020A 頻譜分析儀介紹:性能、特點及應用

HarmonyOS NEXT 原生應用/元服務-性能分析基礎耗時分析Time分析

信道選擇對網絡性能的影響

案例分析,搬運機械手如何選擇電機?

關于Patterning的選擇和性能分析以及應用

關于Patterning的選擇和性能分析以及應用

評論