我們知道閃存磁盤是在HDD以后出現的,由于SSD優異的隨機性能、越來越大的容量和越來越低的成本等優勢,使得閃存熱度上升、乃至大有替換HDD的趨勢。由于歷史繼承性等原因,SSD在設計是也是借鑒了部分HDD技術,包含接口技術。

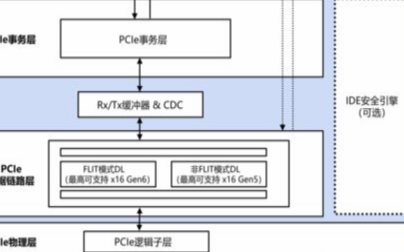

現在絕大多數SSD都是采用SATA/SAS接口,但是通用的SATA/SAS接口是針對HDD設計,但面對閃存速度上百倍的提升,接口的帶寬就成為了I/O的最大瓶頸;隨后PCIe接口的SSD也得到廣泛應用來應對高性能要求;美光也開始探索串行NOR閃存接口。

到目前為止,大部分存儲廠商都推出了對應的PCIe閃存卡(如 EMC XtremSF PCIe SSD卡 )和磁盤。

PCIe-SSD架構解析

PCIe作為CPU的局部總線,最大的特點在于數據傳輸吞吐量大和延遲低。對于NandFlash固態存儲而言,傳統磁盤存儲領域存在的隨機讀寫問題將不復存在,因此,整個存儲系統的瓶頸從存儲介質轉移到了傳輸接口上來了。為存儲而生的SATA/SAS接口在SSD上的表現不是那么理想了,非常影響IO的傳輸延遲。為此,顯而易見,存儲接口應該從傳統的SATA/SAS往離CPU更近的系統總線PCIe或者DIMM方向發展。

大家其實很早就認識到了這一點,當年Fusion-io推出基于PCIe的閃存卡時,讓整個業界為此眼前一亮,原來閃存也可以這么玩?為此,Fusion-io在前幾年都一直非常的紅火。NandFlash本身不是一個新東西,基于NandFlash的存儲在電子設計領域,以及移動存儲領域早就開始應用了。但是,將NandFlash作為數據中心的存儲介質、在消費電子領域替代磁盤,也就發展了沒有多少年。作為磁盤存儲的第二選擇,很多芯片廠商提供了基于SATA、SAS接口的NandFlash控制器,例如Marvell、LSI都有類似的芯片。

但是,為了能夠充分利用NandFlash存儲介質的特性,SATA、SAS接口本身就是一個性能瓶頸點。這兩年基于PCIe接口的SSD存儲一直在蓬勃發展,由于整個行業處于軍閥混戰的年代,nvme標準還沒有充分的得到落實,所以,這方面的接口控制器也就五花八門,個具特色。

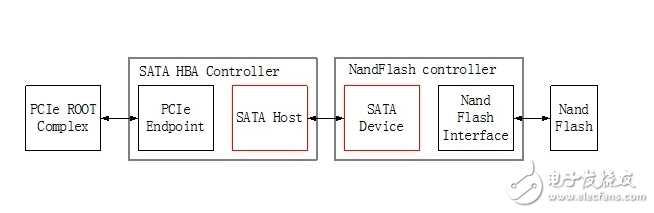

在市場早期,很多廠商為了能夠快速進入市場,利用現有技術很快構建出了PCIe接口的閃存卡。典型的產品如上圖所示,這是一款Oracle(SUN)的PCIe Flash卡,采用4個Marvell閃存控制器的SATA閃存模塊,通過LSISAS1068E控制器連接到PCIe總線上。這種結構將已經成熟的HBA控制器和基于SATA/SAS接口的NandFlash控制器技術結合了起來,具體如下所示:

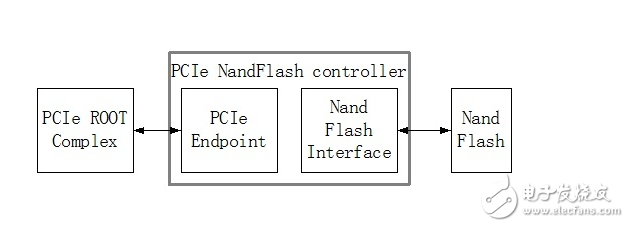

從技術的角度來看,采用這種方案顯然引入了延遲,中間多了一層SATA/SAS接口的轉換。所以,這種卡的性能往往會比Fusion-IO的性能要差。原因在于Fusion-IO沒有采用這種簡單的技術堆疊,而是采用FPGA自己做了一個基于PCIe的NandFlash控制器。采用這種技術方案的結構如下圖所示:

上述方案最大的好處是降低了IO延遲,去除了無謂的SAS/SATA接口層,使NandFlash直接連到了PCI總線上。這種直接基于PCI總線的技術方案也被稱之為Native PCIe方案,并且已經成為各個廠商公認的未來閃存存儲的技術路線之一。所以,從芯片廠商的角度出發,急需需要研制基于PCI接口的閃存控制器,替代現有的接口轉換方式。

如今以Intel為首的Nvme標準如火如荼的推進,并且慢慢的被各大廠商接受。一旦Nvme標準大范圍的應用,基于該標準的控制器將會大量涌現,到那時,基于PCI總線的閃存存儲將會和現在的SATA/SAS存儲一樣,成為應用主流。有時候在想,Fusion-IO為什么當年沒有和Intel進行合作?或者為什么Fusion-IO沒有自己來推動閃存控制器的變革,讓更多的廠商一起加入到這個游戲圈中來?從短期來看,Fusion-IO的產品有很大的價值,但是,從長期來看,更大的價值在于控制器、基于Nandflash存儲軟件的標準化。Flash存儲的市場空間巨大,標準化會是大勢所趨。雖然Fusion-IO發展很早,但是,沒有趕上標準化的快車,因此,標準化的集團軍會對Fusion-IO進行圍剿,從而導致Fusion-IO發展困難。

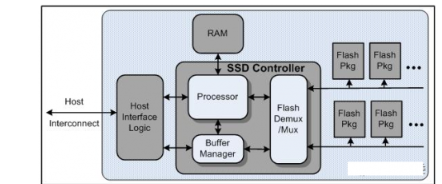

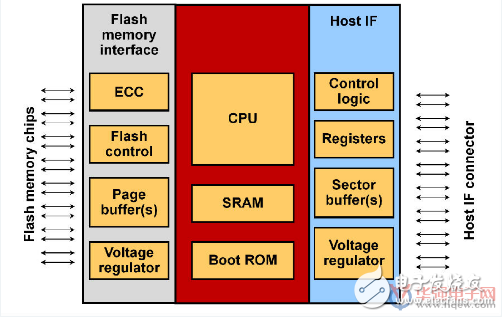

分析閃存控制器的架構,首先得了解SSD。一般來說SSD的存儲介質分為兩種,一種是采用閃存(Flash芯片)作為存儲介質,另外一種是采用DRAM作為存儲介質。我們通常所說的SSD就是基于閃存的固態硬盤,其采用FLASH芯片作為存儲介質。SSD的基本組成結構包括Flash顆粒和Flash控制器,Flash控制器中有芯片,負責Flash的讀寫、磨損均衡、壽命監控等等。

Flash控制器的主要的工作任務包括三大方面:一是后端訪問Flash,管理后端Flash顆粒,包括各種參數控制和數據IO; 二是前端提供訪問接口和協議:實現對應的SAS/SATA target協議端或者NVMe協議端, 獲取Host發出的IO指令并解碼和生成內部私有數據結果等待執行;三是FTL層核心處理。下面我們具體來介紹一下Flash 控制器是怎樣做這幾件事的。

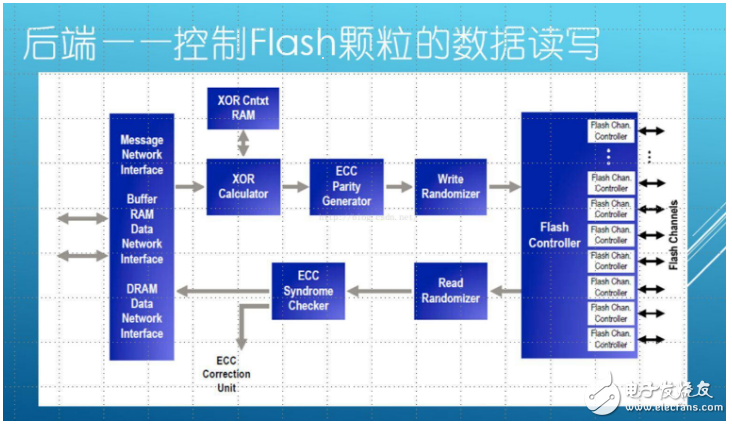

第一,后端訪問Flash的操作內容

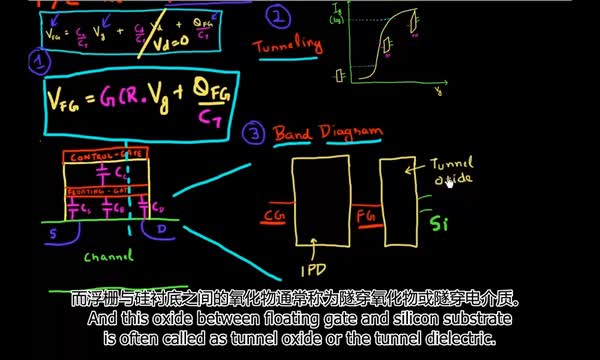

后端訪問Flash首先必須提到的是閃存通道控制器。這個控制器里面有多個通道,每個通道掛多片Flash。它與后端Flash顆粒之間存在托管協議。數據寫入Flash的時候,除了主機發送的數據或者原始數據,其他數據都必須進行ECC校驗。ECC是通用的稱謂,里面有多種算法,其中包括糾錯率較低的BCH算法,LAPC低密度校驗碼等。數據讀出的時候,通過擾碼,加擾,解擾,看ECC是否出現錯誤,若有錯則在糾錯后將芯片發到內部,供后續的程序處理。因此,后端訪問Flash的主要任務即是管理后端Flash顆粒,包括各種參數控制和數據IO。

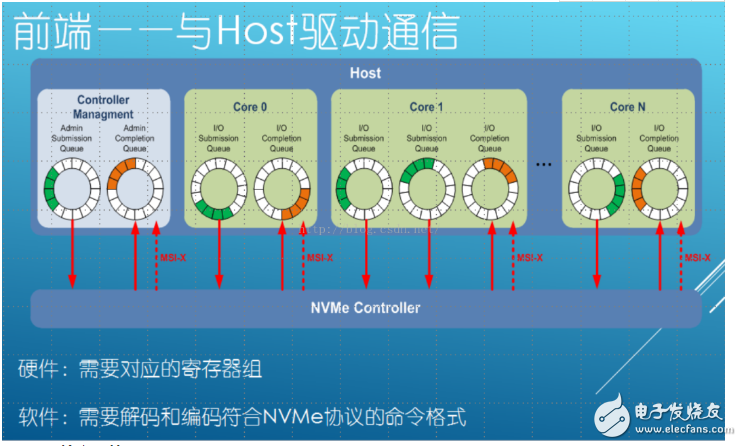

第二,前端提供訪問接口和協議

前端提供訪問接口和協議,跟主機驅動通信,利用標準格式輸配到系統里面,接收主機端發過來的指令,即完成、實現對應的SAS/SATA target協議端或者NVMe協議端,獲取Host發出的IO指令并解碼和生成內部私有數據結構等待執行。如果遵從NVMe標準,包括提交命令的方法、完成命令的處理方法等都定好了,包括各種隊列、隊列深度,Queue Pair的總體數量最大可以達到64K個,隊列深度也可達64K個,所以,系統里同時可能存在64K×64K IO排著,但是目前的系統是用不到這么多Queue的,因為底下的介質速度還不足以支撐。

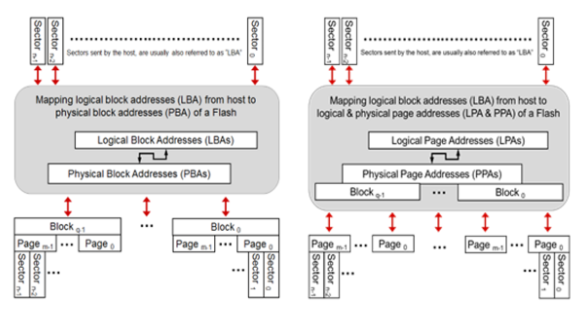

第三,FTL層——核心層處理

核心層FTL層,是一款Flash控制器的關鍵競爭力所在。它既可以是純軟件算法,包括元數據管理,數據布局影射、磨損均衡、垃圾回收、緩存策略、片間RAID和掉電元數據一致性保障等內容。同時,它也可以在進行重復性工作時輔以硬加速引擎。這是非純軟件的,輔有硬加速的成分在里面。硬加速涉及到所使用的芯片。有的芯片支持硬加速,比如說鏈表的維護。這是因為做垃圾回收時需要要用到鏈表,拿傳統的軟件算法,插入一個或者追加一些項目,所耗費的CPU周期較大,此時用硬加速并行,再加上一些硬邏輯的加速,則可節省開銷。

Flash控制器的兩種策略和方式:

現有的Flash控制器可采用兩種方式:一種是少量的強核心加少量硬件加速。所謂強核心就是一個核心的性能高、頻率高,分支預判、并行度、單元數量、執行管道,各種參數都高于一般水平。核心強了以后,硬加速就不需要這么多了,可以用少量的硬加速。

另一種方式則是大量弱核心+大量硬加速。比如說16個核心,每個核心比較弱,但是能夠增加執行的并行度,有16個并發核心執行,跑16套處理程序,這是兩種架構。這是一種多核心協作架構模式,其協作方式可以是同構協作也可以是異構協作

1. 同構協作就是每個核心做的事都是完全一樣的,處理的步驟完全一樣。如果你的控制器陣列里面有16個IO,有16個核心,每個核心都能處理一個IO,這是同構協作。

2. 異構協作則是多個核心做不同的事情。處理同一個IO,第一個IO第一步,第一個核心處理,這個核心處理完以后,把這個IO扔到下一個核心,再處理下一步,等這個核心空出來以后,處理下一個IO的第一步,這就是所謂的流水線了,所謂的異構就是如此。

不管怎么樣,總體看一下基于PCIe的閃存架構,有些PCIe Flash廠商直接采用FPGA自定義閃存控制器;有些PCIe Flash廠商采用現有SATA/SAS閃存模塊結合HBA控制器;有些PCIe Flash廠商直接采用最新的PCIe閃存控制器。個人認為第三種方案是未來的趨勢,雖然,目前能夠提供這種Native PCIe閃存控制器的廠商不多,但是,最近幾年此類芯片將會被大量研發,并且符合Nvme標準的控制器將會成為發展趨勢。下面對目前市場上出現的幾款Native PCIe閃存控制器進行介紹。

Marvell PCIe閃存控制器

Marvell可以說是第一個(2012年初)推出PCIe閃存控制器的廠商。該閃存控制器可以支持4通道NandFlash芯片,并且可以外擴DRAM,內置ARM處理器。看起來,這款控制器的能力不是很強,管理的NandFlash數量有限。在個人電腦領域,基于這款控制器的存儲卡可以替代現有SSD盤。但是,如何利用這款芯片構建存儲容量更大的PCIe卡呢?

其實,采用一個PCI橋就可以將多個基于Marvell控制器的Flash模塊組合在一起,從而形成一塊容量巨大的PCIe存儲卡。Marvell控制器88NV9145內部結構和PCIe卡結構如下圖所示:

通常可以采用8個存儲模塊來構建一個PCIe板卡,每個存儲模塊采用Marvell控制器管理4個閃存芯片,然后通過一個PCIe switch將所有閃存模塊連接起來。采用該方案實現的板卡如下圖所示:

這種方案的優點是去除了SATA/SAS轉換接口,將NandFlash連接到了PCIe總線上。缺點是Marvell的控制器管理能力有限,存儲容量將會很受限制。另外,這種方案還增加一層PCIe總線。在控制器模式下,Marvell控制器能夠提供的性能為9.3萬隨機讀的IOPS和7萬隨機寫IOPS。

另一個問題需要討論的是FTL在何處實現?從理論上來講,FTL可以在Marvell的控制器內部實現。但是,該控制器內部的只提供了一個ARM處理器和ECC校驗引擎,處理能力似乎有限。因此,個人認為,采用該控制實現的Flash卡,FTL在host端實現最佳。在Host端的驅動程序中實現FTL,可以對板卡上的存儲模塊統一管理,從數據冗余角度來看,數據會更加安全,另外,FTL所管理的資源塊也會更多,優化空間更大。

LSI PCIe閃存控制器

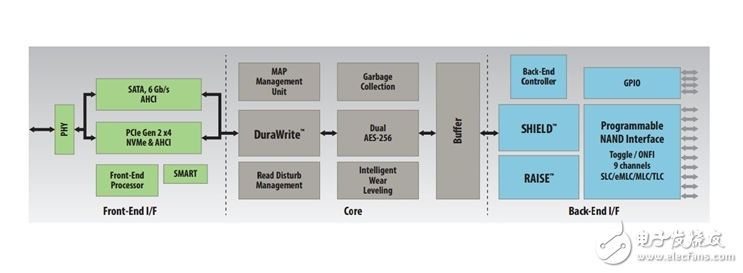

2013年年底的時候,LSI收購Sandforce,獲得了閃存控制器芯片。收購后不久推出了Native PCIe控制器SF3700系列。該控制器的內部結構如下圖所示:

和Marvell閃存控制器相比,LSI控制器顯得更加的高端、大氣、上檔次。該芯片不僅可以支持傳統的SATA接口,而且可以支持PCIe接口。因此如下圖所示,采用該系列控制器,可以實現SATA或者PCIe SSD盤。特別在一些筆記本電腦中,可以直接采用PCIe接口的存儲卡替代SATA-SSD盤。在企業存儲領域,可以采用該芯片實現Native PCIe存儲卡。

LSI控制器內部分成三大部分:第一部分是SATA/PCIe接口,包括一個前端處理器,實現PCIe和SATA數據傳輸的功能;第二部分是SSD控制器的核心,解決NandFlash的寫放大、數據映射、數據加密以及垃圾回收(Garbage collection)功能;第三部分后端NandFlash控制器,包含一個后端處理器。該控制器內部的數據壓縮算法可以減少NandFlash數據寫入量,提高使用壽命。另外,其內部還提供了RAISE(Redundant Array of Independent Silicon Elements)技術,通過該技術增強數據可靠性。RAISE技術類似于RAID,因此會降低空間使用率,每個NandFlash芯片內部都會預留一些資源塊作為數據冗余空間。另外,在單個NandFlash芯片內部采用了Shield錯誤糾正技術,該技術采用了LDPC(Low-Density Parity Check)編解碼方式。Shield技術有意思的地方是自適應動態編解碼。在正常情況下,采用少量的ECC碼,當NandFlash內部的出錯達到一定情況后,增加ECC冗余度。增加冗余度之后,IO延遲將會增大。所以,Shield技術是一種性能和可靠性的動態平衡技術。

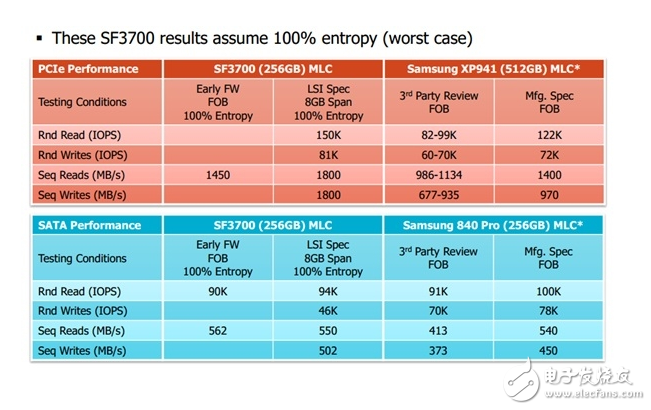

LSI閃存控制器在性能表現方面也不錯,其公布的數據如下:

PMC閃存控制器

2013年中旬的時候PMC收購IDT公司的閃存控制器部門。使得PMC開始進攻閃存控制器市場。IDT公司推出的閃存控制器是業界第一款符合Nvme標準的PCIe閃存控制器。基于該控制器研制的PCIe閃存卡如下圖所示:

通過IDT的控制器89HF32P08可以將Nand Flash芯片直接接入PCIe總線。和Marvell、LSI的控制器不同,PMC(IDT)的控制器顯得更加強悍,其可以管理很多NandFlash芯片顆粒,即單芯片最多可以支持32通道NandFlash芯片。PMC的這款芯片主要的特點如下:

1,可訂制的固件程序(Firmware)

2,支持SLC、MLC閃存芯片

3,支持第三代PCIe接口

4,標準的NVM Express控制接口

5,支持XTS-AES-256加密算法

6,防止電源故障、突然斷電情況下的數據丟失或者損壞

7,數據完整性和可靠性:ECC數據糾錯、閃存通道間RAID保護、端到端的數據保護

采用該控制器可以構建基于PCIe的存儲卡和PCIe設備。一個Demo卡演示如下:

和LSI和Marvell的控制器相比,PMC的控制器很具競爭力。

產品實例:PMC的FlashtecTM NVMe 控制器

這是PMC的控制器,首先它有一個片上網絡,網絡承載16個CPU核心,每個核心里面有一個類似網卡的控制器,網卡連到網絡上,多個CPU之間連起來。簡單說就是4口路由器或者交換機連起來的網絡,多個CPU之間連起來,此外還有硬加速模塊。另外還包括以下幾部分:

RAM控制器,因為芯片上需要有一定量的RAM放臨時數據,寫放大,讀出來寫進去,都要走RAM;

PCIe控制器,這個是跟前端PCIe對等的控制器,IO指令從這兒接收過來;

后端Flash控制器,通過一定數量的通道連Flash顆粒,

加速器(包括緩沖加速器),每做一個操作,都需要有相應的內存,把數據拷到內存里面,內存的維護很費時費力。比如在X86上運行的Linux,其管理內存時需要耗費很多的計算量。對于閃存,精打細算,必須把性能做到極致,因此需用到硬加速。

鏈表加速器,用鏈表來記錄一些信息,哪塊空著,哪塊被應用,這塊用軟件維護很費力,所以需要在這里作加速;

XOR加速器,XOR要用硬加速

最后,來看一下軟件的并行度。16個核心,PMC提供的參考的固件,當然SSD廠商會開發自己的固件,把自己優化的東西放進去,優化的算法放進去。基本上包含了這么一些程序,每個IO讀的地址可能有重疊,重疊就需要有一個鎖定協調,有管命令解析的,有管啟動的,有管日志的,有管磨損均衡的,有管查表的,有管寫數據的,管前端的PCIe Manager,還有負責boot loader的核心,初始化的配置,需要由它處理,data manager,這是主程序,分析IO指令需要干什么,生成一堆的后續步驟下發下去。其實每一塊都可以跑在一個核心上,同一個角色可以復制多份,充分并行。16個核心,達到16份程序并行的運行,16個流水線的Stage,這樣就可以屏蔽處理過程中的時延。

基于PCIe總線的閃存控制器是Flash存儲的關鍵器件,也是未來的發展方向。個人認為基于Nvme標準的PCIe閃存控制器會是市場主力。

電子發燒友App

電子發燒友App

評論