隨著對(duì)缺陷和工藝可變性的日益關(guān)注,DRAM制造商繼續(xù)要求具有成本效益的篩選和工藝改進(jìn)解決方案,但隨著更快接口和多芯片封裝的推出,滿足這一需求變得更加困難。

動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器在各種電子設(shè)備中扮演著重要角色,從電話和個(gè)人電腦到汽車中的ECU和超大規(guī)模數(shù)據(jù)中心內(nèi)的服務(wù)器。同樣,它也是AI/ML中的一個(gè)必要組件,其中需要處理和存儲(chǔ)的數(shù)據(jù)量正在快速增長。曾經(jīng)簡單的內(nèi)存現(xiàn)在是一整個(gè)系列的選項(xiàng),從廉價(jià)到具有更快讀/寫操作事務(wù)的高容量dram(512 GB到1TB)。

不過,DRAM也有一些獨(dú)特的挑戰(zhàn)。盡管這種存儲(chǔ)器的成本歷來很低,但對(duì)質(zhì)量和可靠性的需求卻在不斷增長,尤其是在安全和任務(wù)關(guān)鍵型應(yīng)用中。這與位單元的持續(xù)縮小不一致,這使得它們更容易受到缺陷和工藝可變性的影響。雖然自我修復(fù)和錯(cuò)誤檢測代碼(ECC)方案可以解決制造缺陷,但工程團(tuán)隊(duì)仍然依賴檢查和電氣測試來完成繁重的工作。

質(zhì)量和RAS(可靠性、可訪問性和可維護(hù)性)預(yù)期因應(yīng)用而異。根據(jù)內(nèi)存和處理之間的數(shù)據(jù)量和傳輸速度,數(shù)據(jù)速率和接口有很大不同。這高帶寬存儲(chǔ)器(HBM)接口增加了它自己的復(fù)雜程度,因?yàn)樗笵RAMs能夠從電路板和DIMM插槽遷移到2.5D和3D封裝。

的內(nèi)存和系統(tǒng)工程高級(jí)主管Tadashi Oda表示:“DRAM行業(yè)一直在改進(jìn)其內(nèi)存產(chǎn)品線,以適應(yīng)多樣化的應(yīng)用Advantest America。“起初,DRAM只是計(jì)算機(jī)的一種類型。但今天,應(yīng)用范圍從PC、服務(wù)器、移動(dòng)/平板,到IoT、AI/ML、汽車。結(jié)果,我們有了DDR、LPDDR、GDDR和HBM。每個(gè)DRAM都有獨(dú)特的技術(shù)挑戰(zhàn),我們預(yù)計(jì)會(huì)有越來越多的細(xì)分和挑戰(zhàn)。”

晶片檢測和過程控制

當(dāng)在最接近缺陷和工藝變化發(fā)生的工藝步驟捕獲有意義的數(shù)據(jù)時(shí),新DRAMs的產(chǎn)量上升是最有效的。產(chǎn)量、工藝和器件工程師依靠晶圓生產(chǎn)過程中的檢測來篩選缺陷并提供工藝可變性的反饋。此外,工程團(tuán)隊(duì)通過將工藝變化或缺陷與來自晶片的位圖故障聯(lián)系起來,測量晶片制造期間的關(guān)鍵器件電參數(shù)。

更高的缺陷水平是DRAM單元不斷縮小的直接結(jié)果。Neumonda首席執(zhí)行官Peter p CHMüller解釋說:“現(xiàn)代DRAM技術(shù)使用帶有堆疊電容器的掩埋字線結(jié)構(gòu),其中字線位于硅表面下方,以減少短溝道效應(yīng)。在制造過程中會(huì)出現(xiàn)許多影響DRAM性能的缺陷,這是存儲(chǔ)器制造商通常要測試的。一個(gè)例子是蝕刻過程中的污染,其中顆粒會(huì)阻礙光刻或蝕刻過程。缺陷的另一個(gè)來源是晶片中的污染。如果晶片被污染,銅或其他離子會(huì)在晶片內(nèi)移動(dòng),并導(dǎo)致諸如可變保留時(shí)間的影響。當(dāng)然,制造工藝本身存在變化,導(dǎo)致隔離層厚度的邊際效應(yīng),這會(huì)導(dǎo)致存儲(chǔ)器的電容耦合變化。晶片晶格中的缺陷會(huì)導(dǎo)致DRAM單元機(jī)制中的暫時(shí)或永久泄漏

更高的采樣率,可以高達(dá)100%,有助于更快地發(fā)現(xiàn)缺陷。這在汽車等行業(yè)尤為重要,在這些行業(yè)中,客戶對(duì)極高質(zhì)量的要求——少至十億分之十(ppb)——也推動(dòng)了更高的檢測率。

“總的來說,檢測率實(shí)際上取決于晶圓/組裝制造的工藝步驟和目的,”的產(chǎn)品營銷經(jīng)理Nathan Peng說創(chuàng)新。例如,對(duì)于前端光刻后檢查(開發(fā)后檢查,或ADI ),檢查步驟不一定需要100%取樣。如果客戶希望在光刻過程中監(jiān)控工藝偏差,采樣可能相對(duì)較低,尤其是對(duì)于成熟節(jié)點(diǎn)。另一方面,對(duì)于出貨質(zhì)量保證等過程步驟,100%抽樣是必須的,因?yàn)槠淠康氖菫榱顺鲐浘A質(zhì)量控制,根據(jù)缺陷率要求決定接受或拒絕晶圓或芯片。”

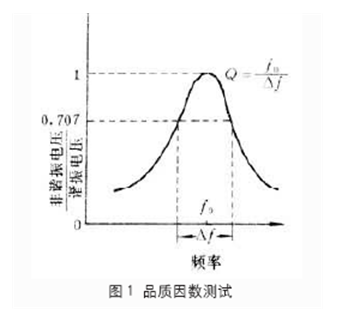

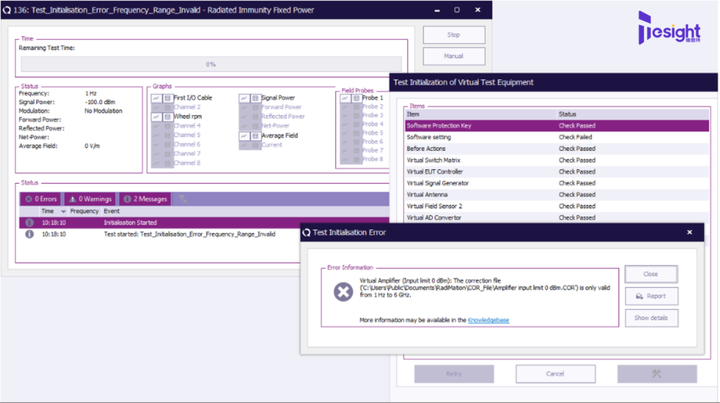

器件和成品率工程師早在FEOL時(shí)就使用電氣測試來深入了解工藝變化。“參數(shù)測試是一種測量電氣特性(閾值電壓、開/關(guān)電流、電容等)的檢查。的晶圓測試解決方案營銷經(jīng)理Yasuhiko Iguchi說道是德科技。“隨著DRAM工藝節(jié)點(diǎn)的進(jìn)步和NAND堆疊層數(shù)的增加,關(guān)鍵存儲(chǔ)元件的設(shè)計(jì)余量不斷縮小。由于這種收縮,存儲(chǔ)器件變得容易受到影響保持力、性能或可靠性工藝變化的影響。使用基本存儲(chǔ)電路元件的電測試的過程控制監(jiān)控在晶片生產(chǎn)中變得更加重要,用于檢查那些基本元件的電特性的變化。典型地,在晶片上制造晶體管層(在線)和在晶片上制造接觸焊盤(生產(chǎn)線末端)之后進(jìn)行測試

晶圓測試后,產(chǎn)量工程師使用故障DRAM單元的位圖來鎖定可能的缺陷源。該位圖來自所有測試的通過/失敗數(shù)據(jù)的光柵化。

Onto Innovation軟件產(chǎn)品管理總監(jiān)Mike McIntyre表示:“內(nèi)建自測(BiST)仍然是創(chuàng)建最適合在單元級(jí)別將線內(nèi)缺陷與器件影響相匹配的內(nèi)存結(jié)果的基礎(chǔ)和黃金標(biāo)準(zhǔn)。當(dāng)與位圖模式分類器結(jié)合使用時(shí),BiST使器件工程師能夠真正了解器件在傾斜時(shí)的靈敏度

制造測試要求

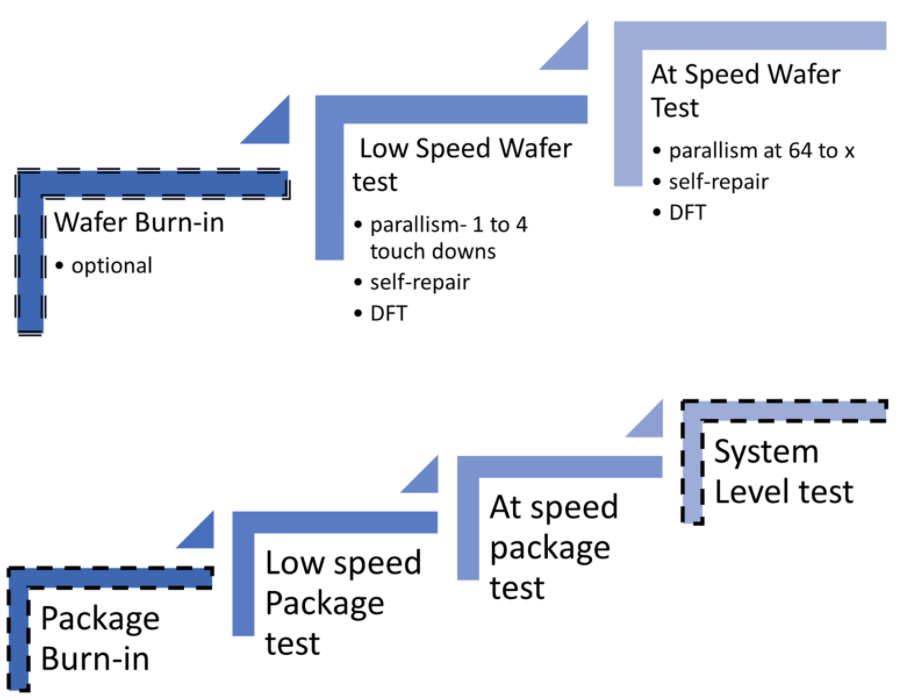

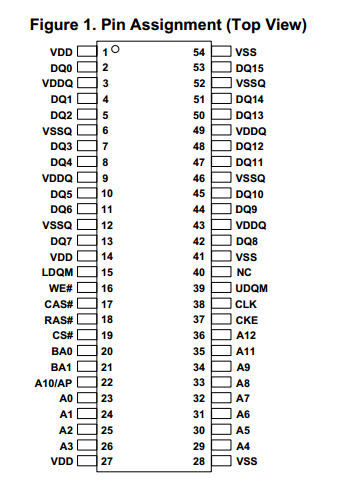

DRAM測試發(fā)生在晶圓探針和封裝測試。最終組裝的封裝、終端系統(tǒng)要求和成本考慮推動(dòng)了測試流程,包括ATE要求和相關(guān)測試內(nèi)容。

工程師使用兩個(gè)插件來管理巨大DRAM陣列的長測試時(shí)間和高速接口的要求。在第一種情況下,所有的內(nèi)存測試算法都以較低的速度應(yīng)用。對(duì)于第二個(gè)芯片(也稱為已知良好的芯片),使用芯片的高速接口,并以運(yùn)行速度運(yùn)行內(nèi)存測試算法。這兩種插入在晶片測試期間執(zhí)行,并且對(duì)于封裝測試可以重復(fù)這兩種插入。

“晶圓測試以大約100MHz的相對(duì)較低的頻率進(jìn)行,以識(shí)別薄弱的單元,然后修復(fù)它們。出于成本原因,平行度需要很高,并且通過每個(gè)晶片大約四次觸地來實(shí)現(xiàn),”Neumonda的p CHMüller說。“這需要具有20,000根針和每根針2.5g的高成本探針卡。它給每個(gè)晶片增加了大約50公斤的高壓。KGD測試需要更高速的陣列和后端全速測試,這需要通過探針卡來執(zhí)行。這需要低并行度和高速探針卡。出于這個(gè)原因,KGD通常不支持最高速度的等級(jí)。”

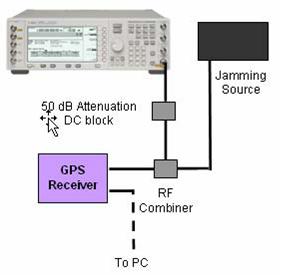

老化過程可用于加速可靠性相關(guān)的缺陷發(fā)現(xiàn),在切換電路信號(hào)的同時(shí)向DRAM施加高溫和高電壓。晶圓級(jí)老化和封裝級(jí)老化系統(tǒng)均可用。在某些情況下,可以添加系統(tǒng)級(jí)測試,在其中測試實(shí)際工作負(fù)載。

晶圓級(jí)老化有幾個(gè)原因。一是提高用于3D封裝的DRAM芯片的可靠性。賣威化是另一個(gè)原因。Advantest的Oda表示:“一些DRAM廠商將DRAM作為晶圓出售,而不是封裝。”“然后,買家包裝和測試DRAM。在這種情況下,DRAM廠商應(yīng)該保證晶圓級(jí)質(zhì)量。他們無法進(jìn)行封裝老化,因此需要在發(fā)送給客戶之前在晶圓上進(jìn)行。”

晶圓級(jí)測試和老化(WLTBI)使內(nèi)存供應(yīng)商能夠?qū)A上的所有芯片施加壓力,以識(shí)別邊緣和故障單元。這使得能夠去除嬰兒死亡率芯片,以提高多芯片/異質(zhì)模塊產(chǎn)量。模塊是通過使用幾種不同的技術(shù)構(gòu)建的,如微處理器、內(nèi)存、硅光子學(xué)等。其中每種技術(shù)都需要不同的電壓、時(shí)間和溫度應(yīng)力要求,這只能在特定技術(shù)的晶圓上完成。此外,WLTBI期間對(duì)存儲(chǔ)器的散熱要求也在不斷提高,密度和頻率的增加推動(dòng)了對(duì)晶圓散熱能力的需求,也推動(dòng)了系統(tǒng)供應(yīng)商提供更高的性能。“

圖1:兩個(gè)DRAM測試流程,可選步驟用虛線突出顯示。資料來源:a 。 Meixner/半導(dǎo)體工程

記憶有什么不同

存儲(chǔ)器ATE系統(tǒng)在幾個(gè)方面不同于邏輯ATE系統(tǒng)。首先,有模式生成和自我修復(fù)的需求。

Advantest的Oda表示:“主要區(qū)別在于,針對(duì)內(nèi)存的ATE解決方案需要配備APG(算法模式生成器)和故障捕獲內(nèi)存(或錯(cuò)誤捕獲RAM)來存儲(chǔ)故障信息和訪問。“在晶圓分類中,存儲(chǔ)器修復(fù)的失效分析是必須的,也是工藝反饋的關(guān)鍵。運(yùn)行中的內(nèi)存修復(fù)分析是非常高的計(jì)算能力,ATE硬件可訪問性是密集的。”

高速接口是第二個(gè)區(qū)別。英特爾戰(zhàn)略業(yè)務(wù)開發(fā)總監(jiān)Ken Lanier表示:“對(duì)于包括內(nèi)存控制器在內(nèi)的SoC設(shè)備,高速I/O故障可通過集成DFT功能解決太達(dá)因。“這意味著SoC測試人員不再受限于內(nèi)存I/O速率。一個(gè)10歲的SoC測試人員可能會(huì)很好地測試帶有DDR5接口的處理器。另一方面,內(nèi)存測試人員仍然必須進(jìn)行全速測試,以保證某個(gè)部件全速運(yùn)行,包括極其苛刻的計(jì)時(shí)測試。存儲(chǔ)器ATE還必須在極高的測試點(diǎn)數(shù)下進(jìn)行,以抵消較大存儲(chǔ)器的較長測試時(shí)間的影響。這給ATE設(shè)計(jì)人員帶來了巨大的挑戰(zhàn),他們需要開發(fā)專門的測試儀電子設(shè)備,以難以置信的高集成度實(shí)現(xiàn)這種高速能力。這也意味著新的內(nèi)存標(biāo)準(zhǔn)推動(dòng)了對(duì)新測試設(shè)備的需求,因此設(shè)備的使用壽命變得更短。”

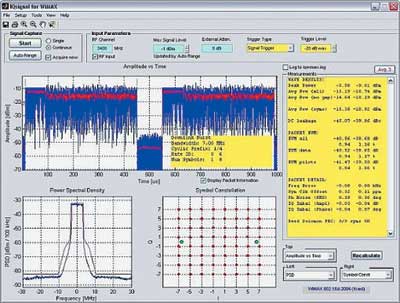

DRAM測試內(nèi)容地址范圍很廣,針對(duì)測試刷新能力、單元泄漏和解決單元故障的一長串模式,有許多特定于存儲(chǔ)器的模式。其中許多需要來自相鄰位單元的特定數(shù)據(jù)。[1]例如,臭名昭著的行錘測試強(qiáng)調(diào)位單元在連續(xù)讀取后保持其數(shù)據(jù)的能力。[2]如前所述,分別對(duì)存儲(chǔ)器性能和接口性能進(jìn)行高速測試,檢查操作時(shí)序規(guī)格(如tAC、tRCD)和I/O時(shí)序規(guī)格(如tVB、tVA)。

“DRAM需要大量使用內(nèi)部測試,我喜歡稱之為‘秘密測試模式’,”Neumonda的p CHMüller說。這些是專有的,用于在測試過程中實(shí)現(xiàn)高并行性,例如,通過將多個(gè)I/O壓縮為單個(gè)I/O。或者,可以將定時(shí)參數(shù)修改為比自然操作更關(guān)鍵的值,以找到弱內(nèi)存單元

雖然一些晶圓缺陷/故障機(jī)制與邏輯技術(shù)中的類似,但可靠位存儲(chǔ)的本質(zhì)需要一些額外的關(guān)注。由于DRAM單元的密度,對(duì)缺陷的敏感性非常高。如果每個(gè)失敗的位單元、行或列都被標(biāo)記為失敗,則產(chǎn)品產(chǎn)量將會(huì)很低。幾十年前,這些現(xiàn)實(shí)促使設(shè)計(jì)工程師增加備用行和列,以及在測試期間執(zhí)行修復(fù)的相關(guān)方法。在晶圓級(jí),可以通過激光或電熔斷(e-fuse)進(jìn)行修復(fù),但在封裝級(jí)只能進(jìn)行e-fuse。誤差校正碼(ECC)電路可以在制造測試和系統(tǒng)使用期間管理單位故障。用于修復(fù)的芯片面積可以是總面積的5%到10%。

同時(shí),為了降低成本,在晶片和封裝測試中都采用了并行測試。“因?yàn)閮?nèi)存是商品,測試成本才是王道,”小田說。“因此,DRAM使用大規(guī)模并行。對(duì)于晶圓測試,技術(shù)趨勢是一次觸地(1TD)。NAND 1TD在幾年前變得很常見,DRAM 1TD也成為一種迫在眉睫的需求。為了實(shí)現(xiàn)這一點(diǎn),ATE需要組裝許多引腳電子器件和設(shè)備電源。Advantest開發(fā)了一種新的創(chuàng)新型測試單元,通過將ATE和處理器集成在一個(gè)緊湊的單元中,提高了每給定占地面積的并行性。”

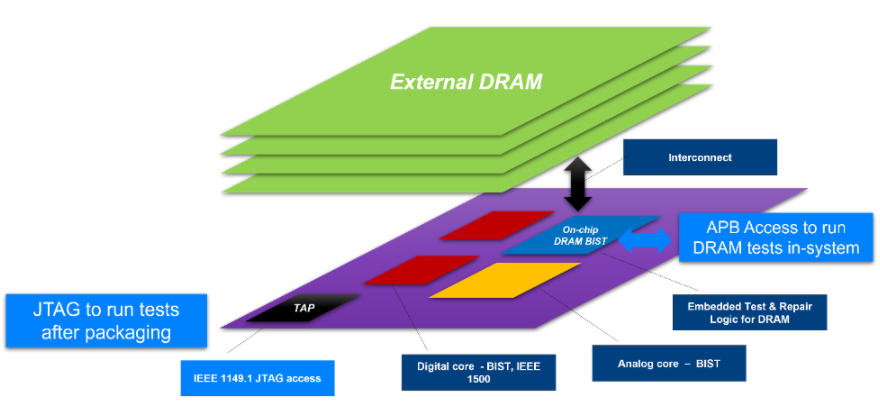

DRAM測試不可能沒有測試設(shè)計(jì)(DFT),其中可編程存儲(chǔ)器阿拉伯學(xué)者發(fā)動(dòng)機(jī)是最重要的。通過提供運(yùn)行大量內(nèi)存測試算法的能力,它使工程團(tuán)隊(duì)能夠在設(shè)備生命周期的每個(gè)階段權(quán)衡測試時(shí)間和測試覆蓋率。作為一個(gè)IP模塊,內(nèi)存BiST還需要適應(yīng)各種DRAM I/O接口,無論是LPDDR、DDR、GDDR還是HBM。其中每一種都有不同的延遲、數(shù)據(jù)速率和協(xié)議。其他DFT方案支持老化測試插入,并允許使用I/O壓縮進(jìn)行并行測試。為了找到薄弱的存儲(chǔ)單元,DFT改變內(nèi)部DRAM時(shí)序。DFT支持存儲(chǔ)器陣列自修復(fù)和HBM通道修復(fù)。

DRAM修復(fù)主要是根據(jù)制造測試標(biāo)準(zhǔn)進(jìn)行的。在過去十年中,JEDEC DRAM標(biāo)準(zhǔn)定義了封裝后修復(fù)(PPR ),它為每個(gè)存儲(chǔ)體提供一行修復(fù)。[3]標(biāo)準(zhǔn)化方法能夠在啟動(dòng)時(shí)進(jìn)行修復(fù)。

“DRAM可編程測試引擎很少提供給最終用戶,”Faisal Goriawalla說,他是新思科技。“隨著可靠性和油田內(nèi)部作業(yè)相關(guān)要求的增加,這種情況正在發(fā)生變化。隨著壽命的延長,服務(wù)器中DRAM的任何現(xiàn)場更換都將非常昂貴。DRAM廠商現(xiàn)在提供系統(tǒng)可用冗余,稱為封裝后修復(fù)(PPR)。JEDEC已經(jīng)為DRAM廠商標(biāo)準(zhǔn)化了這種封裝后修復(fù)。系統(tǒng)制造商希望在他們的SOC中部署這些解決方案,以利用DRAM中的備用容量,并提高現(xiàn)場可靠性。”

多芯片封裝中DRAM面臨的挑戰(zhàn)

無論是在2.5 D封裝中連接到計(jì)算SOC的DRAM,還是在3D封裝中使用HBM的堆疊式DRAM,產(chǎn)量和測試工程師都需要解決單芯片DRAM部件之外的其他挑戰(zhàn)。有些是DRAMs獨(dú)有的,而有些則不是。

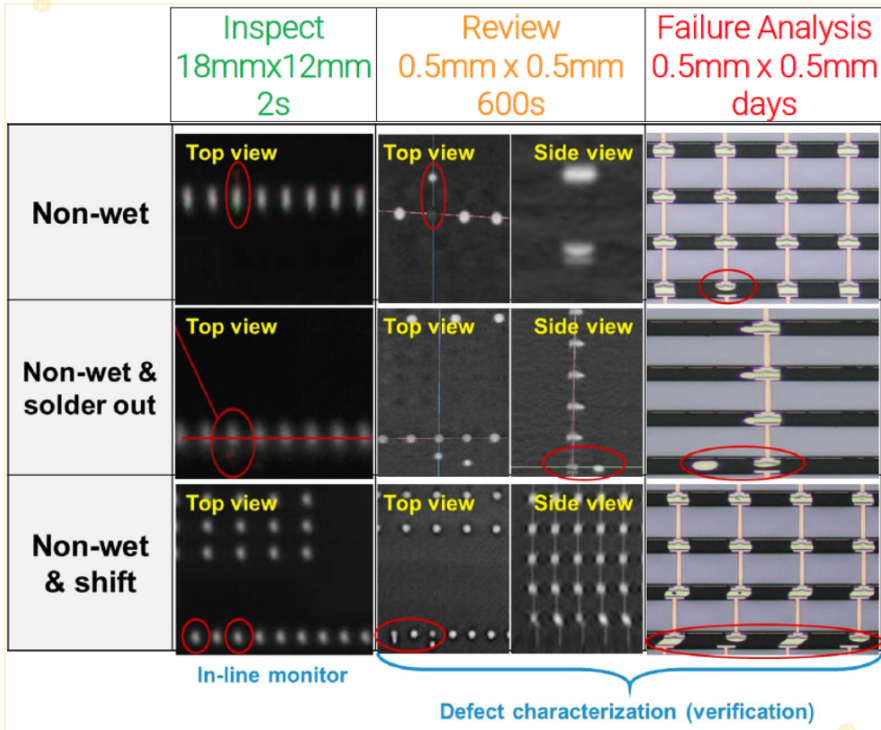

現(xiàn)代DRAM間距尺寸和高微凸塊數(shù)量給檢查和測試都帶來了挑戰(zhàn)。

“多芯片封裝產(chǎn)品需要更多的2D/3D檢測和計(jì)量解決方案。對(duì)于多芯片封裝,將有額外的互連步驟(扇出、微凸點(diǎn)、直接鍵合等)。芯片之間的額外互連需要更多的工藝步驟。扇出需要對(duì)斷裂或橋接的RDL線進(jìn)行缺陷檢查。對(duì)于微凸點(diǎn),需要CD和高度度量,以及凸點(diǎn)頂部的殘余缺陷檢測。對(duì)于直接粘接,需要進(jìn)行檢查以發(fā)現(xiàn)裂紋、空隙和分層。”

HBM接口以較低的功耗提供高得多的數(shù)據(jù)速率。它被設(shè)計(jì)為寬接口(1,024通道),用于2.5D和3D封裝解決方案。然而,堆疊裸片的凸塊間距大小和眾多連接使得通道修復(fù)選項(xiàng)成為必需,以適應(yīng)裸片之間的錯(cuò)誤接合。隨著芯片堆疊變得更深(范圍從4到16),這個(gè)倍數(shù)增加。這需要特定的測試策略來發(fā)現(xiàn)故障通道并實(shí)現(xiàn)通道修復(fù),這正是DFT所促進(jìn)的。但是眾所周知,由于不良的冶金接觸,檢查方法具有更高的篩選潛在缺陷結(jié)合的可能性。

硅通孔(tsv)和微凸塊連接實(shí)現(xiàn)了堆疊HBM DRAM管芯。作為已知良好管芯預(yù)期的一部分,測試流程通常在管芯減薄步驟之前篩選有缺陷的tsv。然后,一旦所有堆疊的管芯之間的鍵合被連接,就可以對(duì)它們進(jìn)行檢查和測試。檢查在評(píng)估焊接質(zhì)量、芯片對(duì)準(zhǔn)(重疊)和芯片翹曲方面發(fā)揮著重要作用。

“目前他們使用的是帶焊帽的銅柱,”Frank Chen說,他是布魯克。“隨著間距縮小,它將逐漸過渡到混合鍵合。對(duì)于垂直堆疊,芯片放置精度對(duì)于監(jiān)控和維護(hù)至關(guān)重要。過度移動(dòng)會(huì)導(dǎo)致凸起拉伸和斷開,從而導(dǎo)致不潤濕。同樣重要的是以粘合層厚度(BLT)測量的壓縮。大BLT會(huì)導(dǎo)致不潤濕,小BLT會(huì)導(dǎo)致焊料擠出。在某些情況下,焊料會(huì)被完全擠出,即不在焊盤區(qū)域內(nèi)。”

圖2:堆疊管芯微凸塊鍵合缺陷識(shí)別和檢查。來源:布魯克

硬短路和開路故障最容易隔離。在部分或邊緣債券的情況下,人們擔(dān)心并非所有債券都會(huì)被識(shí)別出來。然而,其中一些連接最終會(huì)在現(xiàn)場失效。在這些情況下,詳細(xì)的檢查會(huì)有所幫助,但這并不容易。

“目前,在速度足夠快、能夠靈敏地區(qū)分各層并評(píng)估影響粘合的屬性的工具方面存在一些差距,尤其是當(dāng)您使用8層、12層或16層堆疊時(shí)。對(duì)于這些多層,隨著管芯變得更薄,翹曲和對(duì)準(zhǔn)成為問題。所有這些都需要監(jiān)控,”陳指出。

將DRAM并入多芯片封裝提高了測試和DFT的標(biāo)準(zhǔn)。

“在多芯片模塊中,你會(huì)遇到與可測試性、可訪問性和多芯片診斷相關(guān)的額外挑戰(zhàn),”Synopsys的Goriawalla說。此外,HBM也帶來了挑戰(zhàn),因?yàn)槟鸁o法單獨(dú)測試邏輯芯片和內(nèi)存芯片。您必須一起測試這兩者。您需要測試它們之間的互連。對(duì)于這種芯片堆棧,您需要能夠訪問它,這是IEEE標(biāo)準(zhǔn)1500所允許的。然后,當(dāng)然,你的診斷需要區(qū)分和隔離,以進(jìn)行物理故障分析。基于DRAM的引擎需要在邏輯小芯片上。它位于控制器和DFI總線主芯片上的PHY之間。在測試模式下,它控制PHY通過PHY運(yùn)行讀/寫指令,以測試外部存儲(chǔ)器和互連。”

圖3:支持DRAM測試、診斷和修復(fù)的2.5D多管芯配置。來源:Synopsys

對(duì)于多芯片組件制造,可追溯性是實(shí)現(xiàn)操作反饋和芯片性能匹配的關(guān)鍵。

Onto的McIntyre表示:“一旦芯片被認(rèn)為“可以使用”,確保多芯片模塊(MCM)兼容性和監(jiān)控版本控制的可追溯性和分析技術(shù)在內(nèi)存和MCM中使用的任何其他組件類型之間通常是相同的。“最好的例子是使內(nèi)存性能與封裝中其他芯片的性能相匹配。這是必須的。將速度較慢的內(nèi)存芯片放在高性能封裝中的后果可能會(huì)導(dǎo)致整個(gè)封裝的降級(jí)。這通常會(huì)導(dǎo)致較低的平均銷售價(jià)格和盈利能力。另一個(gè)例子是將動(dòng)態(tài)工作范圍受到影響的內(nèi)存放入一個(gè)封裝中,該封裝將部署在一個(gè)預(yù)期高度可變的環(huán)境中。”

摘要

由于成本的原因,許多觀察家認(rèn)為DRAM是一種商品。但是把所有的DRAM都放在同一個(gè)桶里是一種誤解。內(nèi)存性能對(duì)于一些最復(fù)雜的計(jì)算系統(tǒng)的整體性能至關(guān)重要。

但是,鑒于計(jì)算對(duì)兆兆字節(jié)數(shù)據(jù)和更快執(zhí)行速度的需求不斷擴(kuò)大,DRAM向更密集的位單元和堆疊芯片實(shí)施的遷移正在使測試和檢查變得復(fù)雜,隨著更快的內(nèi)存和更復(fù)雜的封裝成為常態(tài),這一問題只會(huì)變得更加難以解決。

審核編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論