基于FPGA的設(shè)計(jì)方法助力物聯(lián)網(wǎng)解決核心問題

推薦 + 挑錯(cuò) + 收藏(0) + 用戶評(píng)論(0)

原文:FPGAs solve challenges at the core of IoT implementation

作者:Helmut Demel,德國(guó)萊迪思半導(dǎo)體公司(Lattice Semiconductor)工程師

譯者:艾美婷 校審:朱正貴

責(zé)編:周建丁([email protected])

當(dāng)前,物聯(lián)網(wǎng)(IoT)已成為一個(gè)廣受歡迎的名詞,幾乎每一個(gè)電子設(shè)備相互連接到互聯(lián)網(wǎng)上加以使用,都被大家稱為物聯(lián)網(wǎng)。它包含了一個(gè)從智能家電、汽車到可穿戴設(shè)備相關(guān)的各種應(yīng)用程序列表,并且這一列表仍在持續(xù)呈現(xiàn)爆炸式增長(zhǎng)。但這種增長(zhǎng)卻恰恰帶來了它的實(shí)戰(zhàn)挑戰(zhàn),需要找到解決方案。

智能,連接的設(shè)備,和物聯(lián)網(wǎng)的生態(tài)系統(tǒng),他們正在幫助創(chuàng)造,致力于改變?nèi)粘I睢?duì)于個(gè)別的消費(fèi)者,可能意味著使設(shè)備更有效和成本效益的日常任務(wù),讓他們更安全,甚至有助于確保他們過上更健康的生活。對(duì)于企業(yè)來說,物聯(lián)網(wǎng)的承諾技術(shù)在自動(dòng)化、能源效率、資產(chǎn)跟蹤和庫(kù)存控制、運(yùn)輸和位置、安全、個(gè)人跟蹤和節(jié)能方面具有顯著的優(yōu)勢(shì)。

但要實(shí)現(xiàn)將百億量級(jí)設(shè)備組成物聯(lián)網(wǎng),設(shè)計(jì)師必須克服重大的實(shí)戰(zhàn)挑戰(zhàn)。其中的一些關(guān)鍵,例如提高物聯(lián)網(wǎng)設(shè)備的能源效率,處理不兼容的接口,以及提供一個(gè)處理增長(zhǎng)路徑來處理不可避免的設(shè)備性能增長(zhǎng)要求。一個(gè)基于FPGA的設(shè)計(jì)方法可以幫助解決這些挑戰(zhàn)。

挑戰(zhàn)1:能源效率

物聯(lián)網(wǎng)是一個(gè)強(qiáng)大的概念,有希望如字面所述改變社會(huì)生活和工作的能力。事實(shí)上,目前很多領(lǐng)域都正在向物聯(lián)網(wǎng)發(fā)展,這將使很多物(things)看起來與今天大不相同,從消費(fèi)者的角度考慮只是其中的一部分。例如,可穿戴設(shè)備像耐克FuelBand常常需要八九個(gè)組件,包括處理器、無線模塊、存儲(chǔ)器、顯示器、八個(gè)傳感器和一個(gè)USB接口。在接下來的幾年中,組件數(shù)量可能會(huì)下降,但三或四個(gè)剩余的組件的復(fù)雜性和晶體管數(shù)量將迅速增長(zhǎng),因?yàn)楦嗟膬?nèi)存和處理能力是必需的,并相應(yīng)的讓屏幕分辨率和亮度增加。實(shí)現(xiàn)能源效率使物聯(lián)網(wǎng)設(shè)備在單電池下運(yùn)行多年,不是一件容易的事。它要求使用低功率元件和更有效的電力系統(tǒng)。而且,它將需要在架構(gòu)和芯片級(jí)的相應(yīng)改善。

如今,幾乎每一個(gè)物聯(lián)網(wǎng)設(shè)備的設(shè)計(jì)重點(diǎn)都集中在確保它是盡可能高效節(jié)能的(圖1)。例如,對(duì)于一個(gè)智能手機(jī),這可能意味著(比現(xiàn)在的)好得太多,但這不會(huì)在一夜之間發(fā)生。相反,它會(huì)分別反應(yīng)在幾代的產(chǎn)品中,一步一步地優(yōu)化。而物聯(lián)網(wǎng)設(shè)備在每個(gè)層面都應(yīng)該首先保證能源效率。

大多數(shù)物聯(lián)網(wǎng)應(yīng)用程序都需要“永遠(yuǎn)在線”。最簡(jiǎn)單的例子,物聯(lián)網(wǎng)終端處于待機(jī)模式,等待一些人的互動(dòng)來喚醒它。然而,如果一個(gè)活動(dòng)的處理器被用來監(jiān)視用戶交互設(shè)備,該設(shè)備將消耗大量的功率。主處理器,在無線模塊中的處理器核心,和顯示一樣是能耗最大的消費(fèi)者。因此在物聯(lián)網(wǎng)終端,必須采用最獨(dú)特的方案,最小化功耗的需求。

有一個(gè)可提供“永遠(yuǎn)在線”的解決方案,使用一個(gè)小的、低功耗的FPGA監(jiān)測(cè)傳感器、按鈕、甚至語(yǔ)音命令。處理器、無線模塊,顯示待機(jī)模式,直到FPGA決定用戶的需要“喚醒”終端提供服務(wù)。除了低功耗,這種架構(gòu)不同于其他模式狀態(tài)下電源管理,其他設(shè)備實(shí)際上是在線或關(guān)閉,而它則是休眠或部分喚醒,使處理器能夠動(dòng)態(tài)地從一個(gè)階段到另一個(gè)。這種方法顯著的節(jié)省了功率,從而獲得了更長(zhǎng)的電池壽命、更長(zhǎng)的顯示壽命和較低的熱輻射。

圖1 監(jiān)測(cè)傳感器工作而處理器休眠

挑戰(zhàn)2:不兼容的接口

任何物聯(lián)網(wǎng)產(chǎn)品都包含幾個(gè)具有獨(dú)特功能的子系統(tǒng)。根據(jù)需求,每個(gè)子系統(tǒng)都有許多不同的組件選項(xiàng)。然而,在許多情況下,設(shè)計(jì)師只能被迫選擇完全基于接口兼容性的組件。

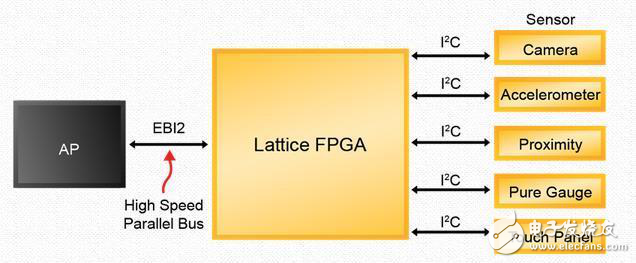

例如,物聯(lián)網(wǎng)產(chǎn)品設(shè)計(jì)的核心,可以改變處理器的分配,但在時(shí)間和人力資源上,由于需要重構(gòu)代碼,配合新的功能,需要非常昂貴的測(cè)試和認(rèn)證。然而,如果你想換一個(gè)新的無線模塊,因?yàn)樗阋嘶蛴幸恍┬碌墓δ埽枰褂靡粋€(gè)新的串行接口,您的處理器不能支持,選擇改變你的處理器,還是找一個(gè)解決方案,以低成本的維持這兩個(gè)接口,并且不增加原的容量?幸運(yùn)的是,有一個(gè)解決方案:使用一個(gè)非常小的、低成本FPGA橋接接口。

現(xiàn)階段我們擁有許多不同接口的橋接參考設(shè)計(jì)。這些基于FPGA的解決方案,如圖像傳感器接口,處理器不支持SubLVDS、CSI-2、或HiSPi,或一個(gè)處理器只有一個(gè)視頻輸出顯示的低成本實(shí)現(xiàn)SPI。

非常好我支持^.^

(1) 100%

不好我反對(duì)

(0) 0%

下載地址

基于FPGA的設(shè)計(jì)方法助力物聯(lián)網(wǎng)解決核心問題下載

相關(guān)電子資料下載

- 四維圖新成員企業(yè)四維智聯(lián)榮登中國(guó)物聯(lián)網(wǎng)新物種企業(yè)榜單 42

- 工業(yè) CPE 雙頻網(wǎng)關(guān)在工業(yè)物聯(lián)網(wǎng)中的應(yīng)用優(yōu)勢(shì) 143

- fpga的開發(fā)流程有哪些步驟?fpga和嵌入式系統(tǒng)的區(qū)別在哪里? 149

- Arm物聯(lián)網(wǎng)事業(yè)部業(yè)務(wù)拓展副總裁馬健:如何幫助AIoT企業(yè)加速創(chuàng)新? 21

- 傾角傳感器物聯(lián)網(wǎng)解決方案 190

- 如何創(chuàng)建FPGA控制的機(jī)器人手臂? 219

- 如何創(chuàng)建FPGA控制的機(jī)器人手臂 49

- 用VHDL語(yǔ)言創(chuàng)建一個(gè)8位算術(shù)邏輯單元(ALU) 50

- 工業(yè)物聯(lián)網(wǎng)解決方案:卷繞機(jī)數(shù)據(jù)采集管理系統(tǒng) 67

- 您的存儲(chǔ)器堆疊了嗎?—賽靈思推出16GB HBM FPGA 109