隨著半導(dǎo)體工藝不斷地進(jìn)步,那些原本存在芯片中的大型存儲(chǔ)器會(huì)轉(zhuǎn)變成數(shù)十或數(shù)百個(gè)小型的存儲(chǔ)器陣列,并且散布在芯片中各個(gè)角落。這些陣列有的是寄存器堆,F(xiàn)IFO,或者是在存儲(chǔ)器管理系統(tǒng)中一些對(duì)性能要求較高的存儲(chǔ)器。針對(duì)這種類型的小型陣列,如果想要偵測(cè)出與速度相關(guān)的瑕疵以及固定邏輯(stuck-at)故障,其實(shí)并不是一件容易的事。

傳統(tǒng)上,測(cè)試數(shù)字集成電路可以采用功能性向量,或是由自動(dòng)測(cè)試向量生成(ATPG)工具所產(chǎn)生的向量。此類軟件工具主要為隨機(jī)邏輯生成基于掃描的測(cè)試向量,對(duì)于待測(cè)組件(DUT)的存儲(chǔ)器部分,卻無(wú)法提供測(cè)試方案。得依賴存儲(chǔ)器內(nèi)建自測(cè)試(BIST)的方法來(lái)測(cè)試寄存器。

尤其是那些采用先進(jìn)工藝的存儲(chǔ)器陣列,存在著許多難以預(yù)測(cè)的潛在瑕疵。傳統(tǒng)的存儲(chǔ)器BIST方案會(huì)利用March或其它算法重復(fù)簡(jiǎn)單的測(cè)試序列來(lái)偵測(cè)大部分的寄存器故障。在一種存儲(chǔ)器BIST方法中,DUT中的狀態(tài)機(jī)自身能產(chǎn)生和分析那些測(cè)試存儲(chǔ)器中的每一個(gè)地址所需用到的測(cè)試向量,免去了外部ATE機(jī)的測(cè)試工作。另一種方法,則是讓片上處理器來(lái)測(cè)試存儲(chǔ)器,其缺點(diǎn)在于通常得等到DUT設(shè)計(jì)接近完成的時(shí)候,才能判斷出這種方法的有效性。

由于會(huì)影響芯片的面積與性能,小型存儲(chǔ)器陣列通常并不適合增加存儲(chǔ)器BIST邏輯。那些地址空間很少但端口很多的存儲(chǔ)器尤其不適合BIST。因?yàn)橄鄬?duì)于陣列大小,存儲(chǔ)器端口數(shù)量對(duì)BIST控制電路規(guī)模的影響更大,所以,可能導(dǎo)致實(shí)現(xiàn)BIST控制電路所需的門數(shù)甚至?xí)痛鎯?chǔ)器本身一樣大。同時(shí),BIST還要求所有存儲(chǔ)器的輸入引腳都有一個(gè)多路選擇器來(lái)選擇BIST信號(hào)與系統(tǒng)信號(hào)。對(duì)多端口存儲(chǔ)器而言,多路選擇電路會(huì)引起布線擁擠,并且導(dǎo)致性能的嚴(yán)重下降。

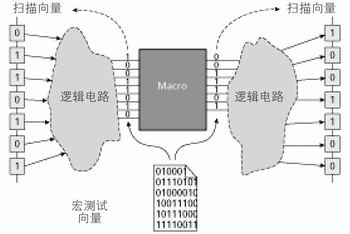

圖1 宏測(cè)試采用向量轉(zhuǎn)換的技術(shù),

在掃描單元與內(nèi)部宏單元,如嵌入式存儲(chǔ)器

陣列之間傳遞測(cè)試向量。

嵌入式存儲(chǔ)器測(cè)試方案

考慮到BIST對(duì)小型存儲(chǔ)器陣列造成的負(fù)面影響,一個(gè)簡(jiǎn)單的選擇便是不去測(cè)試 — 但用戶極有可能會(huì)收到瑕疵品。或者,在辦公室里花更多的時(shí)間,為每一個(gè)存儲(chǔ)器陣列,手工生成完成測(cè)試算法所需的向量。好在還有一種更有效的選擇 ─ 那就是利用ATPG工具和待測(cè)組件的掃描儀單元,在每一個(gè)嵌入式存儲(chǔ)器的輸入端生成測(cè)試向量,并從輸出端得到響應(yīng)。這項(xiàng)新技術(shù),有時(shí)候被稱為“向量轉(zhuǎn)換”,或者是“宏測(cè)試”(macro testing)(見圖1)。如此一來(lái),工程師便可以運(yùn)用一組宏向量序列,來(lái)測(cè)試獨(dú)立的嵌入式模塊(也可以稱之為宏)。一些EDA 公司可以提供有此功能的軟件工具。這些工具可以把那些為獨(dú)立的嵌入式存儲(chǔ)器(宏模塊) 所設(shè)計(jì)的宏向量自動(dòng)轉(zhuǎn)化成芯片級(jí)掃描向量,并把結(jié)果傳送到掃描單元,供作驗(yàn)證之用。

宏測(cè)試完成嵌入式模塊所需的測(cè)試不需要附加測(cè)試邏輯電路。其次,最終的嵌入式存儲(chǔ)器掃描向量還可以像標(biāo)準(zhǔn)的阻塞掃描向量一樣,具有簡(jiǎn)單的測(cè)試協(xié)議,因此能夠減少在產(chǎn)品測(cè)試機(jī)臺(tái)上向量的調(diào)試時(shí)間。有些公司應(yīng)用宏測(cè)試技術(shù)平行測(cè)試100多個(gè)存儲(chǔ)器。如此一來(lái),宏測(cè)試掃描向量也不過(guò)是與最長(zhǎng)的向量長(zhǎng)度相同。這項(xiàng)技術(shù)可用于測(cè)試任何嵌入式模塊,即便是所謂的“黑盒子”(black box)。只要在模塊的I/O端定義向量,那么這些向量便可以傳遞通過(guò)外圍的邏輯電路。

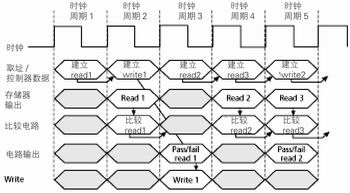

圖2 流水線處理能夠讓連續(xù)的讀/寫操作在連續(xù)的

時(shí)鐘周期內(nèi)完成,提供全速存儲(chǔ)器BIST功能。

嵌入式存儲(chǔ)器中的時(shí)序故障

如同一般的隨機(jī)邏輯,嵌入式存儲(chǔ)器也需要測(cè)試靜態(tài)故障和“實(shí)速”(at-speed)故障。由于存儲(chǔ)器BIST通常在系統(tǒng)時(shí)鐘下運(yùn)行,因此也被稱之為實(shí)速存儲(chǔ)器BIST。然而,即使BIST控制邏輯利用系統(tǒng)時(shí)鐘來(lái)設(shè)定測(cè)試序列,卻需要數(shù)個(gè)時(shí)序周期去完成單獨(dú)的讀/寫操作。因此,實(shí)速存儲(chǔ)器BIST電路雖然采用系統(tǒng)時(shí)鐘頻率,其實(shí)并無(wú)法如同芯片在正常模式運(yùn)作下那樣,執(zhí)行讀寫周期。運(yùn)用流水線(pipelining)讀寫操作,則可產(chǎn)生較為有效的測(cè)試,稱之為“全速”(full-speed) 存儲(chǔ)器BIST(見圖2)。簡(jiǎn)言之,便是在連續(xù)的時(shí)鐘周期里,執(zhí)行連續(xù)(back-to-back)的讀寫操作,如同在正常系統(tǒng)操作模式下的存儲(chǔ)器一般。

對(duì)于大型存儲(chǔ)器而言,測(cè)試那些與速度相關(guān)的故障時(shí),全速存儲(chǔ)器BIST其實(shí)是個(gè)不錯(cuò)的選擇。但是對(duì)于小型或時(shí)序要求很高的存儲(chǔ)器而言,同樣的測(cè)試方法可能會(huì)有問題。宏測(cè)試工具要把每組功能性向量轉(zhuǎn)換成掃描向量,所以每組向量的測(cè)試速度則必然變慢。不僅如此,有些嵌入式存儲(chǔ)器完全同步,并使用與掃描鏈相同的時(shí)鐘信號(hào)。當(dāng)時(shí)鐘信號(hào)觸發(fā)其模塊時(shí),掃描單元上先前的設(shè)定值便會(huì)被新值所取代。如此一來(lái),便無(wú)法傳遞模塊輸出端的期待值。因此,傳統(tǒng)的宏測(cè)試方式無(wú)法適用于不具有門控時(shí)鐘的同步存儲(chǔ)器。

不過(guò),同步宏測(cè)試可以解決這個(gè)問題。簡(jiǎn)言之,便是執(zhí)行連續(xù)的全速測(cè)試,而不需要重復(fù)載入掃描鏈。同步宏測(cè)試會(huì)決定掃描單元上用來(lái)產(chǎn)生第一個(gè)宏向量的值,并載入掃描鏈。同時(shí),也會(huì)決定用來(lái)產(chǎn)生第二個(gè)宏向量的值,并且在掃描單元的輸入端以管道方式傳輸。當(dāng)掃描鏈被載入時(shí),不同的時(shí)鐘信號(hào)即可以實(shí)速觸發(fā)。如此一來(lái),好幾組的全速向量便被傳送到模塊。全速測(cè)試可以不受干擾地應(yīng)用于設(shè)計(jì)中的幾乎任一模塊。不僅如此,全速測(cè)試只用到功能邏輯電路,而非測(cè)試邏輯電路,因此,可以執(zhí)行更接近實(shí)際狀況的全速測(cè)試。

結(jié)語(yǔ)

在實(shí)際測(cè)試中總是得面臨測(cè)試工具的成本,測(cè)試開發(fā)時(shí)間,測(cè)試機(jī)臺(tái)的時(shí)間,測(cè)試向量的調(diào)試時(shí)間,以及測(cè)試覆蓋率之間的考量與抉擇。宏測(cè)試是可以有效地對(duì)那些與日俱增的小型嵌入式模塊進(jìn)行靜態(tài)與實(shí)速故障測(cè)試的工具。它甚至可以應(yīng)用到較大的存儲(chǔ)器,透過(guò)芯片的功能邏輯,自動(dòng)執(zhí)行全速測(cè)試。

- 測(cè)試小型(5662)

相關(guān)推薦

新方法“喚醒”石墨烯超導(dǎo)性 可拓展其應(yīng)用

1495

1495存儲(chǔ)器的帶寬是多少?

存儲(chǔ)器的編碼方法

SRAM存儲(chǔ)器結(jié)構(gòu)框圖解

主板維修新方法

使用電感式傳感的篡改攻擊低功耗檢測(cè)新方法

關(guān)于如何提高SRAM存儲(chǔ)器的新方法

分享一種中斷輸入和動(dòng)態(tài)顯示的新方法

功率型LED熱阻測(cè)量的新方法

基于LabVIEW8.2提取ECG特征點(diǎn)的新方法

基于線性化技術(shù)的二次分配問題求解新方法

多功能存儲(chǔ)器芯片測(cè)試系統(tǒng)設(shè)計(jì)方案

如何停止windows的自動(dòng)更新方法

如何去測(cè)試存儲(chǔ)器和數(shù)字芯片?

嵌入式存儲(chǔ)器的設(shè)計(jì)方法是什么?

控制電源的全新方法

求一份存儲(chǔ)器測(cè)試的解決方案

求助 數(shù)據(jù)存儲(chǔ)器 FLASH程序存儲(chǔ)器 FLASH數(shù)據(jù)存儲(chǔ)器的區(qū)別

矢量混頻器表征和混頻器測(cè)試系統(tǒng)矢量誤差修正的新方法 白皮書

識(shí)別傳感器信號(hào)的新方法

請(qǐng)問怎么設(shè)計(jì)一種面向嵌入式存儲(chǔ)器測(cè)試和修復(fù)的IIP?

請(qǐng)問怎樣去測(cè)試存儲(chǔ)器芯片?

轉(zhuǎn)帖:完全用Proteus8.0編譯測(cè)試ARM Cortex的最新方法

運(yùn)用于matlab中的矩陣求逆的新方法有哪些啊(不是函數(shù)inv)

采用CCS5+controlSUIT的模式,請(qǐng)同志 們談?wù)勥@種新方法的感受。

馬上教會(huì)你如何測(cè)試主流DSP存儲(chǔ)器

一種求解非線性約束優(yōu)化全局最優(yōu)的新方法

16

16虛擬環(huán)境中軟體的包圍盒更新方法分析

8

8一種均勻直線陣列干擾抑制的新方法

4

4虛擬環(huán)境中軟體的包圍盒更新方法分析

13

13一種確定變壓器變比和聯(lián)結(jié)組別的新方法

39

39Flash存儲(chǔ)器的內(nèi)建自測(cè)試設(shè)計(jì)

35

35光伏并網(wǎng)逆變器的定頻滯環(huán)電流控制新方法

44

44功率型LED熱阻測(cè)量的新方法

23

23測(cè)試小型存儲(chǔ)器陣列的新方法

430

430

利用C語(yǔ)言和GEL語(yǔ)言的Flash編程新方法

1457

1457

MEMS振蕩器激勵(lì)新方法

776

776采用小波包分析和擬同步檢波的電壓閃變信號(hào)檢測(cè)新方法

1137

1137

采用小波包分析和擬同步檢波的電壓閃變信號(hào)檢測(cè)新方法

1133

1133

抑制變壓器勵(lì)磁涌流的新方法

3539

3539

愛國(guó)者哈筆熊:2010潮媽育兒新方法

367

367多路高壓觸發(fā)源抗干擾的新方法

695

695太陽(yáng)能系統(tǒng)效率和可靠性優(yōu)化新方法

711

711基于路徑和節(jié)點(diǎn)權(quán)重因子的黑啟動(dòng)路徑尋優(yōu)新方法(趙達(dá)維)

1

1機(jī)場(chǎng)場(chǎng)面監(jiān)視雷達(dá)目標(biāo)檢測(cè)新方法

0

0一種級(jí)數(shù)混合運(yùn)算產(chǎn)生SPWM波新方法

0

0新方法可“喚醒”石墨烯超導(dǎo)性能

1321

1321開發(fā)以3D打印隨選制藥的新方法

674

674基于平面陣列電磁傳感器的金屬缺陷檢測(cè)新方法

0

0目前微通道面臨的限制,突破硅技術(shù)的一種新方法

4064

4064三星延長(zhǎng)QLED壽命和效率的新方法

2710

2710四元數(shù)姿態(tài)更新方法公示版C語(yǔ)言版免費(fèi)下載

0

0美研發(fā)測(cè)試新冠病毒中和抗體活性新方法

293

293一種復(fù)制和粘貼URL的新方法

3600

3600存儲(chǔ)器陣列間接訪問的機(jī)制

12

12蘋果ios15怎么更新,更新方法

21398

21398基于eMMC陣列的高速固態(tài)存儲(chǔ)器的研究與設(shè)計(jì)

30

30并聯(lián)APF直流側(cè)電壓選擇新方法

5

5在洗碗機(jī)中設(shè)計(jì)和實(shí)現(xiàn)用戶界面的新方法

2

2VLSI系統(tǒng)設(shè)計(jì)的最新方法

0

0一種產(chǎn)生激光脈沖的新方法

233

233

基于PMSM 控制系統(tǒng)仿真建模的新方法

0

0軋機(jī)牌坊滑板壓虧修復(fù)的新方法

0

0 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論