信號處理器(DSP),信號處理器(DSP)是什么意思

DSP是(digital signal processor)的簡稱,是一種專門用來實現信號處理算法的微處理器芯片。根據使用方法的不同,DSP可以分為專用DSP和可編程DSP,專用DSP只能用來實現某種特定的數字信號處理功能,如數字濾波、FFT等。專用DSP不需編程,使用方便,處理速度快,但是靈活性差。可編程DSP則像GPP(General Purpose Processor,如Pentium)一樣有完整的指令系統,通過軟件實現各種功能。

DSP的發展

DSP的發展歷史大致可以分成四個階段:萌芽階段、成長階段、成熟階段、突破階段。

萌芽階段:1982年以前

在這段時期里為解決Von Neumann結構在進行數字信號處理時總線和存儲器之間的瓶頸效應,許多公司投入大量人力和物力開展了很多探索性的工作,研制出了一些DSP的雛形,如AMI的S2811、Intel的2920、AT&T的DSP-1和NEC的uPD7720。但這些產品的運算速度都太慢,而且開發工具嚴重不足,無法進行大規模的開發工作,還不能稱作真正意義上的DSP。第一片DSP是1982年TI公司出品的TMS320C10,它是—個16位的定點DSP,采用了哈佛(Harvard)結構,有一個乘加器和一個累加器。TMS320C10完成—次乘加操作需要390ns,即在一秒鐘的時間內可以完成250萬次左右的乘加運算。或許正是因為生產出了第一個DSP,TI公司在此后的三十幾年中一直是DSP界的領軍人物。

成長階段:1982-1987年

這段時間內各公司相繼研制出了自己的DDSP并不斷地改進。如1985年,TI推出了TMS320C20,它具備單指令循環的硬件支持,尋址空間達到64K字,有專門的地址寄存器,一次乘加運算只需耗時200ns。1987年,Motorola公司推山了DSP56001,采用24位的數據和指令,有專門的地址寄存器,可以循環尋址,累加器有保護位,一坎乘加運算只需耗時75ns。此外,在這段時期中還有一些代表產品,如AT&T的DSPl6A、AD的ADSP-2100,TI的TMS320C50。

成熟階段:1987-1997年

在這個階段里各公司不斷借鑒相互的優點,并完善自身的設計,推出了特點分明的產品,如TI的TMS320C54系列、AD的ADSP2100系列、Lucent(前身為AT&T)的DSPl600系列和Motorola的DSP56000系列。它們在供電上都支持3.3v,片上的存儲器也較大,都有JTAG模塊支持用戶在線調試。另外,TI等公司還專門提供DSP的內核,為一些專用集成電路(ASIC)的開發提供了空間。此外,在成熟階段還首次出現了多處理核的DSP,如TI的TMS320C80和Motorola的MC68356等,雖然它們的推出在商業上并不算成功,但卻指明了一個有潛力的發展方向。

突破階段:1997年直至現在

這段時間里DSP的發展非常迅速,各公司相繼建立了自己從定點到浮點,從低端到高端,從通用到專用完整的產品系列,并且在DSP設計上有了大的飛躍,推出了一些性能突出的產品。很多公司相繼采用先進技術研制了計算性能很高的DSP,如AD的SHARC系列、TI的TMS320C6000系列、Motorola和Agere(前身為Lucent微電子)的StarPro等,每秒鐘可以完成1G條以上的指令,計算速度驚人。TI公司還研制出功耗最小的DSP TMS320C55系列,為便攜式設備提供了一個明智的選擇。

回顧DSP發展的二十幾年,也正是電子、信息和微電于技術快速發展的二十年,正是后者為DSP提供了必要的技術支持和應用的廣闊空間,使得DSP及其相關的技術日益受到人們的重視。

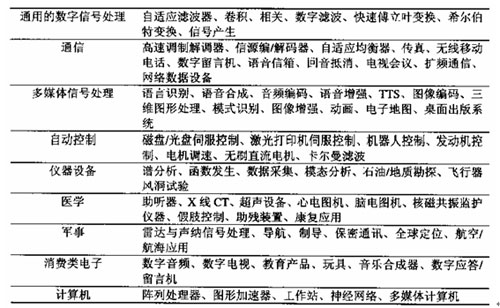

DSP的應用

DSP的產生主要是為了滿足通信、雷達、數字電視等領域對實時數字信號處理的需要。典型的數字信號處理算法包括數字濾波、FFT等。這些算法的共同特點是要進行密集的數學計算,因此DSP在體系結構上采取了一系列措施,使之在數學計算方面具有特別突出的性能;而在其它方面,例如文字處理、數據庫管理等則不如GPP。除了密集的數學計算之外,DSP應用的另一個突出特點是實時性。在許多應用領域,如通信中的調制、解調、雷達中信號檢測等等,數據是以幀為單位更新的,每她的長度一般為微秒到毫秒量級,DSP必須在這段時間之內完成處理并輸出結果,這就是所謂實時處理。顯然,實時處理要求處理器具有極高的處理速度,能夠對外部事件迅速做出反應(能夠及時迅速地響應中斷),并且具有強大的IO吞吐能力。 DSP的應用范圍非常廣泛,在下表中大致歸納出一些。

面對DSP巨大的市場和廣闊的發展前景,世界上最大的幾個半導體公司都對此投入巨資、開展競爭。如TI、AD、Agere、Motorola、Siemens、Semiconductor等公司都在全力開發和生產DSP器件,不同公司DSP的側重點都有所不同。

DSP的結構特點

1.MAC指令,硬件乘法器和累加器。

2.存儲器結構

GPP一般采用Von Neumann結構,如圖所示,系統只有一套總線(包括數據總線和地址總線)和單一存儲器,無論是數據還是指令都要經過同樣的數據通道進入處理器內核。

哈佛結構將指令存儲空間和數據存儲空間分離開,各自擁有獨立的總線,這就使取指令和訪問數據可以同時進行,從而緩解了存儲器的瓶頸效應。

3.尋址方式。在進行數字信號處理時,處理器往往要同時維護多個數據緩沖區,而且每個緩沖區的指針都要頻繁移動。 GPP雖然有基址和變址寄存器,但是這些寄存器不能自動更新;而且數量也有限,每個寄存器往往要管理多個緩沖區。DSP用特殊的硬件來尋址數據存儲器,有大量寄存器可以用作數據指針(如ADSP21060有16個),指針的更新可以和其他操作并行執行,所以不占用處理時間。DSP還支持一些特殊的尋址方式,如用來實現環形緩沖區的環形尋址,實現FFT變換所必需的逆序尋址等。

4.零耗循環(zero overhead loop)

GPP每執行一次循環都要用軟件判斷循環結束條件是否滿足,更新循環計數器,還要進行條件轉移。這些例行操作要消耗幾個周期的時間,這種消耗對于短循環是相當可觀的。與GPP不同,DSP可以用硬件實現更新計數器等例行操作,不用額外消耗任何時間,所以是一種零耗循環。由于數字信號處理程序百分之九十的執行時間是在循環中度過,所以零耗循環對提高程序效率是非常重要的。

5. 程序執行時間可預測

實時處理不僅要求處理器必須具有極高的計算速度,而且還要求程序的執行時間要容易預測,否則開發人員無法判斷自己的系統是否滿足實時要求。高性能GPP普遍采用了CACHE和動態分支預測技術,這些動態特性雖然能夠從統計角度提高處理速度,但也使處時間很難精確預測,因為當前指令的執行時間要受到程序運行的歷史過程的影響。盡管從理論上說,程序員可以推測出最壞情況下的執行時間,但是由于各種動態特性的相互影響,最壞執行時間可能遠遠超過程序的典型執行時間,這將導致系統設計過于保守,嚴重浪費資源。與GPP不同,DSP的動態特性較少,而且還通過設置MAX(求最大值)、MIN(求最小值)、CLIP時,DSP生產商還提供了能夠精確模擬每—條指令執行狀態的軟件仿真器Simulator。使設計人員在硬件系統完成之前就能夠調試程序并驗證處理時間。值得注意的是,TI的最新產品TMS320C6011設置了可選擇的兩級CACHE,而AD將要推出的TigerrSHARC采用了動態分支預測技術。這是否意味著DSP正在喪失程序執行時間可預測的特點,或者正在猴備采取其他措施(如提供工具軟件)來彌補因芯片結構日趨復雜對預測時間造成的不利影響,我們將拭目以待。

6.外圍設備

GPP硬件系統(如PC機)的開發一般由專業公司承擔,用戶只從事軟件開發。而DSP工程師往往要自己設計硬件平臺,而且許多DSP應用系統特別是嵌入式系統對體積、功耗有嚴格的限制,所以DSP必須具備開發簡便的特點。多數DSP支持IEEE1149.1標準,用戶可以通過JTAG端口對DSP進行在線實時仿真。另外DSP體現了片上系統(System on chip)的設計思想,在片上集成了DMA、中斷控制、串行通信口、上位機接口、定時器等外圍設備,有的DSP還包含AD和DA轉換器。所以用戶通常只需要外加很少的器件就可以構成自己的DSP系統。

DSP的組成(以ADSP-21xx為例)

DSP芯片能夠以很高的速度實現各種DSP算法,在其內部包括以下功能單元。

計算單元——每個處理器包括3個獨立的、功能完備的計算單元:算術/邏輯單元(ALU)、乘法/累加器(MAC)和桶狀移位器。

計算單元直接處理16位數據并對多精度計算提供硬件支持。

數據地址產生器和程序控制器——兩個專用的地址產生器和—個程序控制器提供對片內、片外存儲器的尋址。程序掉制器支持單周期的條件分支和無開銷循環。雙數據地址生器使處理器能同時產生兩個操作數的地址。數據地址產生器和程序控制器使計算單元保持連續工作狀態,使流量達到最大化。

存儲器——采用修改的哈佛結構,其中數據存儲器存放數據,程序存儲器既可存放指令又可存放數據。所有的處理器都有片內RAM,該片內RAM構成程序存儲空間和數據存儲空間的一部分。片內存儲器的速度很高,處理器可以在一個周期讀取兩個操作數(一個來自數據存儲器,另一個來自程序存儲器)和一條指令(來自程序存儲器)。

串口——串口(SPORT)提供帶有硬件數據壓擴部件的完整的串行接口。支持按μ律和A律壓縮的擴展。SPORT可以容易地和多種流行的串行設備直接接口。每個SPORT能產生一個可編程的內部時鐘或接收—個外部時鐘。SPORT有多通道選項。

定時器一一一個帶有8位預分頻器的定時器/計數器可產生周期性的中斷。

主機接口——主機接口(HIP)有16根數據引腳和11根控制引腳,可以和主機處理器直接連接,無須連接邏輯。HIP非常靈活,易于和各種主機處理器接口。如:Motorola 6800、Intel8051或其他ADSP-21xx系列處理器可以容易地接到HIP上。

DMA接口——內部DMA接口(IDMA)和字節DMA接口(BDMA)可對內部存儲器進行有效的數據傳送。IDMA接口具有16位多路復用的地址和數據總線,支持24位寬的程序存儲器。IDMA接口是完全異步的,在DSP全速運行時,可以寫入數據。字節DMA接口允許引導裝載并且存儲程序指令和數據。

模擬接口——DSP片內集成了模擬和數字信號混合處理電路。該電路由模數轉換器、數模轉換器、模擬和數字濾波器、處理器核的并行接口等組成。轉換器采用Σ-Δ技術獲取樣本。

非常好我支持^.^

(169) 66%

不好我反對

(87) 34%

相關閱讀:

- [電子說] 模型的帶寬對信號眼圖有什么影響? 2023-10-24

- [處理器/DSP] 高通Hexagon NPU架構技術詳解 2023-10-23

- [電子說] 技術壁壘高的DAC核心參數 2023-10-23

- [電子說] 車載DSP:新應用孕育國產“芯”機遇 2023-10-22

- [電子說] LightCounting復盤ECOC 2023:LPO熱潮延續 2023-10-22

- [電子說] ADI ADAU1701DSP數字音頻處理方案 2023-10-20

- [電子說] 車載DSP:新應用孕育國產“芯”機遇 2023-10-19

- [電子說] 國產DSP操作教程:LCD圖片顯示實驗(程序讀取圖片) 2023-10-19

( 發表人:admin )