在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。##在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵

2016-04-26 14:00:01 5104

5104

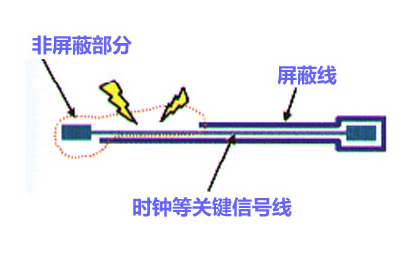

信號走線屏蔽規(guī)則 在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2018-04-13 08:20:00 1567

1567

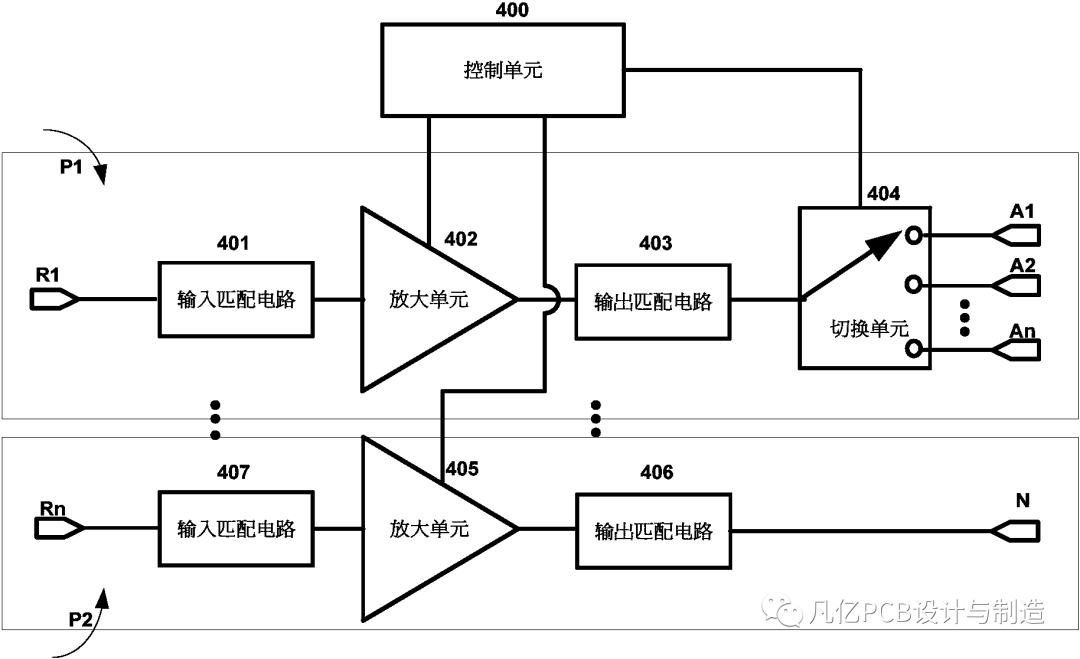

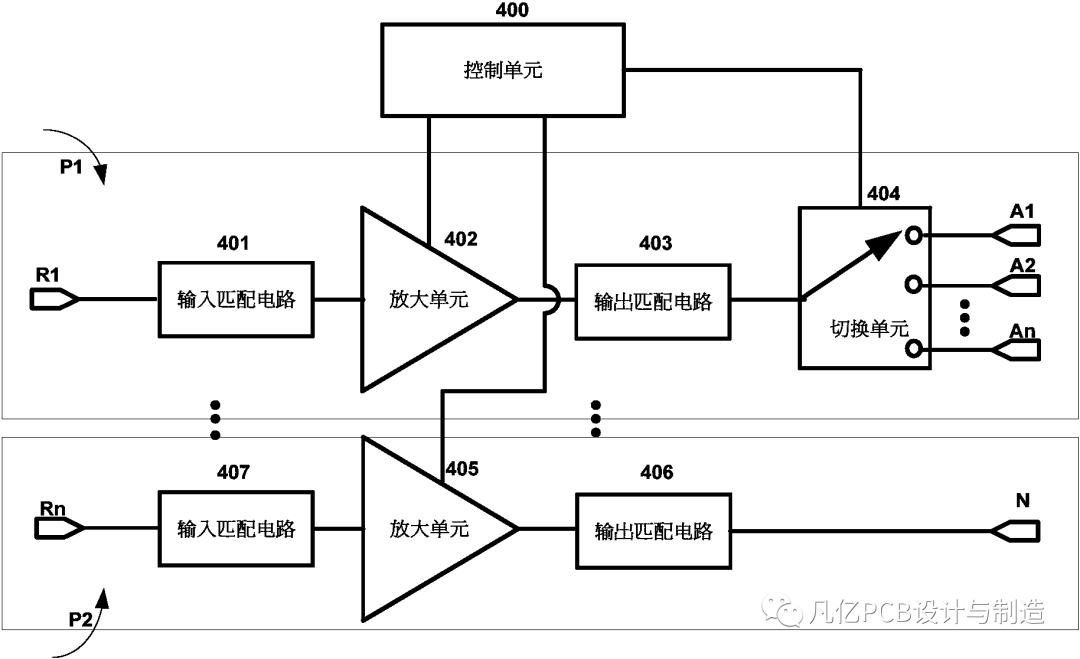

本文主要詳解PCB設(shè)計(jì)高速模擬輸入信號走線,首先介紹了PCB設(shè)計(jì)高速模擬輸入信號走線方法,其次闡述了九大關(guān)于PCB設(shè)計(jì)高速模擬輸入信號走線規(guī)則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 8394

8394

一站式PCBA智造廠家今天為大家講講高速PCB設(shè)計(jì)中的屏蔽方法有哪些?高速PCB設(shè)計(jì)中的屏蔽方法高速PCB設(shè)計(jì)布線系統(tǒng)的傳輸速率隨著時代的更迭也在不斷加快,但這也給其帶來了一個新的挑戰(zhàn)——抗干擾能力

2023-08-08 10:19:06 790

790

產(chǎn)品的PCB設(shè)計(jì)中,我們常常對某些模塊進(jìn)行屏蔽1、電源模塊(PMU+DCDC+LDO)如圖1-3所示,通常電源模塊做為一個發(fā)熱源及干擾源存在于PCB上,對其加上一個屏蔽罩而已有效的降低其對外的輻射

2019-02-26 11:35:44

缐,一來可以稍微提昇屏蔽罩的電磁隔絕能力,另一方面也可以為屏蔽夾無效時,馬上可以更改為屏蔽框,而無需要重新設(shè)計(jì)電路板。 02 屏蔽罩的使用模塊 在MID或VR產(chǎn)品的PCB設(shè)計(jì)中,我們常常對某些模塊

2023-04-18 14:07:13

PCB設(shè)計(jì)中跨分割的處理高速信號布線技巧

2021-02-19 06:27:15

高速PCB設(shè)計(jì)系列課:入門篇:林超文PCB設(shè)計(jì)PADS和OrCAD實(shí)操指南http://t.elecfans.com/topic/22.html?elecfans_trackid=bbspost

2015-05-05 09:30:27

高速PCB設(shè)計(jì)布線系統(tǒng)的傳輸速率在穩(wěn)步加快的同時也帶來了某種防干擾的脆弱性,這是因?yàn)閭鬏斝畔⒌念l率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統(tǒng)就越容易受干擾。 干擾無處不在,電纜

2018-11-28 17:00:27

高速PCB設(shè)計(jì)布線系統(tǒng)的傳輸速率在穩(wěn)步加快的同時也帶來了某種防干擾的脆弱性,這是因?yàn)閭鬏斝畔⒌念l率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統(tǒng)就越容易受干擾。干擾無處不在,電纜

2019-07-17 18:55:38

高速PCB設(shè)計(jì)布線系統(tǒng)的傳輸速率在穩(wěn)步加快的同時也帶來了某種防干擾的脆弱性,這是因?yàn)閭鬏斝畔⒌念l率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統(tǒng)就越容易受干擾。干擾無處不在,電纜

2016-09-14 11:03:51

高速PCB設(shè)計(jì)布線系統(tǒng)的傳輸速率在穩(wěn)步加快的同時也帶來了某種防干擾的脆弱性,這是因?yàn)閭鬏斝畔⒌念l率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統(tǒng)就越容易受干擾。干擾無處不在,電纜

2016-09-21 10:25:21

高速PCB設(shè)計(jì)中的電磁輻射檢測技術(shù),總結(jié)的太棒了

2021-04-25 07:38:23

高速PCB設(shè)計(jì)中的若干誤區(qū)與對策

2012-08-20 14:38:56

黑魔書,高速PCB設(shè)計(jì)經(jīng)典,推薦給需要的你!

2016-01-15 14:15:35

阻抗匹配阻抗匹配是指在能量傳輸時,要求負(fù)載阻抗要和傳輸線的特征阻抗相等,此時的傳輸不會產(chǎn)生反射,這表明所有能量都被負(fù)載吸收了。反之則在傳輸中有能量損失。在高速PCB設(shè)計(jì)中,阻抗的匹配與否關(guān)系到信號的質(zhì)量優(yōu)劣。

2019-05-31 08:12:33

高速PCB設(shè)計(jì)之一 何為高速PCB設(shè)計(jì)電子產(chǎn)品的高速化、高密化,給PCB設(shè)計(jì)工程師帶來新的挑戰(zhàn)。PCB設(shè)計(jì)不再是產(chǎn)品硬件開發(fā)的附屬,而成為產(chǎn)品硬件開發(fā)中“前端IC,后端PCB,SE集成”3個環(huán)節(jié)中

2014-10-21 09:41:25

`請問高速PCB設(shè)計(jì)前期的準(zhǔn)備工作有哪些?`

2020-04-08 16:32:20

電路應(yīng)具備信號分析、傳輸線、模擬電路的知識。錯誤的概念:8kHz幀信號為低速信號。 問:在高速PCB設(shè)計(jì)中,經(jīng)常需要用到自動布線功能,請問如何能卓有成效地實(shí)現(xiàn)自動布線? 答:在高速電路板中,不能只是看

2019-01-11 10:55:05

本帖最后由 eehome 于 2013-1-5 09:46 編輯

高速PCB設(shè)計(jì)指南。

2012-08-04 10:35:49

高速PCB設(shè)計(jì)指南

2012-04-02 22:47:12

高速PCB設(shè)計(jì)指南

2012-08-12 13:09:35

高速PCB設(shè)計(jì)指南

2013-12-07 11:48:35

高速PCB設(shè)計(jì)電容的應(yīng)用采集

2014-10-24 11:19:05

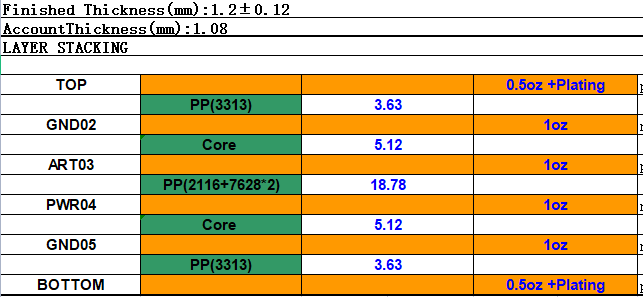

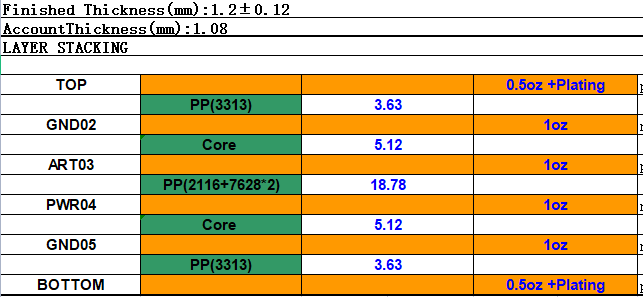

的設(shè)計(jì)要求,結(jié)合筆者設(shè)計(jì)經(jīng)驗(yàn),按照PCB設(shè)計(jì)流程,對PCB設(shè)計(jì)中需要重點(diǎn)關(guān)注的設(shè)計(jì)原則進(jìn)行了歸類。詳細(xì)闡述了PCB的疊層設(shè)計(jì)、元器件布局、接地、PCB布線等高速PCB設(shè)計(jì)中需要遵循的設(shè)計(jì)原則和設(shè)計(jì)方法以及需要注意的問題等。按照筆者所述方法設(shè)計(jì)的高速復(fù)雜數(shù)模混合電路,其地噪很低,電磁兼容性很好。

2012-03-31 14:29:39

`請問高速PCB設(shè)計(jì)規(guī)則有哪些?`

2020-02-25 16:07:38

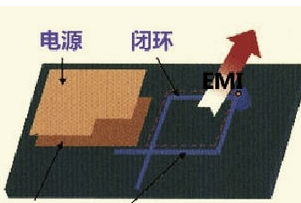

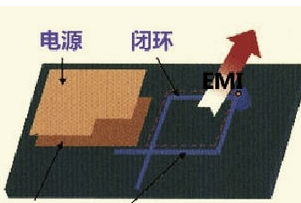

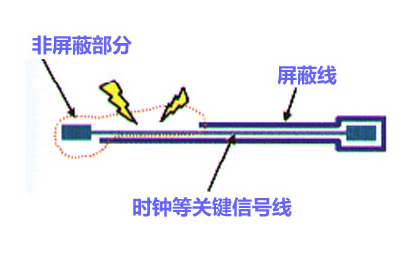

規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地

2016-01-19 22:50:31

對于高速信號的PCB我們經(jīng)常采用gnd shape對串?dāng)_進(jìn)行屏蔽,還要沿著被保護(hù)的對象做地孔,請問地孔的間距如何確定,怎么計(jì)算?謝謝各位幫忙!!!

2012-09-11 15:45:26

資料主要講述射頻與數(shù)模混合高速pcb設(shè)計(jì)

2020-10-23 23:35:56

在高速pcb設(shè)計(jì)中,經(jīng)常聽到要求阻抗匹配。而設(shè)計(jì)中導(dǎo)致阻抗不匹配的原因有哪些呢?一般又對應(yīng)著怎么的解決方案?歡迎大家來討論

2014-10-24 13:50:36

高速pcb設(shè)計(jì)技術(shù)

2009-07-17 21:56:11

、DSP系統(tǒng)的降噪技術(shù)2、POWERPCB在PCB設(shè)計(jì)中的應(yīng)用技術(shù)3、PCB互連設(shè)計(jì)過程中最大程度降低RF效應(yīng)的基本方法六、1、混合信號電路板的設(shè)計(jì)準(zhǔn)則2、分區(qū)設(shè)計(jì)3、RF產(chǎn)品設(shè)計(jì)過程中降低信號耦合

2012-07-13 16:18:40

7月15日晚上8點(diǎn),小哥在QQ語音平臺,進(jìn)行了90分鐘的高速PCB設(shè)計(jì)在線語音交流;在線交流近百人參加,討論熱烈;其中演示和答疑了群里朋友提出的Allegro軟件操作中的問題和高級技巧使用;并以高速

2015-12-22 17:17:28

、高速信號走線屏蔽規(guī)則如上圖所示:在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,則需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。2...

2021-12-31 06:22:08

和Allegro為基礎(chǔ),詳細(xì)介紹了使用SPB 16.6實(shí)現(xiàn)原理圖與高速PCB設(shè)計(jì)的方法和技巧。本書結(jié)合設(shè)計(jì)實(shí)例,配合大量圖片,以通俗易懂的方式介紹PCB設(shè)計(jì)流程和常用電路模塊的PCB設(shè)計(jì)方法。 本書注重實(shí)踐

2017-08-11 17:11:31

掌握高速多層PCB設(shè)計(jì)的基本原則套路及關(guān)鍵點(diǎn)?傳輸線理論基礎(chǔ)知識以及其在PCB設(shè)計(jì)中對EMC的考量?PCB設(shè)計(jì)中EMC的基礎(chǔ)理論及設(shè)計(jì)關(guān)鍵點(diǎn)?屏蔽罩的設(shè)計(jì)?BGA的出線技巧?開關(guān)電源(對傳導(dǎo)影響特別

2019-11-28 17:01:13

經(jīng)過多次的檢測,尤其是對有問題的很難量化的原理圖設(shè)計(jì)和版圖設(shè)計(jì)中的參數(shù)需要反復(fù)多次。在系統(tǒng)復(fù)雜程度越來越高、設(shè)計(jì)周期要求越來越短的情況下,需要改進(jìn)PCB的設(shè)計(jì)方法和流程,以適應(yīng)現(xiàn)代高速系統(tǒng)設(shè)計(jì)的需要。 圖傳統(tǒng)的PCB設(shè)計(jì)流程 歡迎轉(zhuǎn)載,信息維庫電子市場網(wǎng)(www.dzsc.com):

2018-11-27 15:23:52

在pcb設(shè)計(jì)中FPGA與高速并行DAC的布線應(yīng)該注意什么?

2023-04-11 17:30:54

在高速PCB設(shè)計(jì)中,過孔有哪些注意事項(xiàng)?

2021-04-25 09:55:24

圖解在高速的PCB設(shè)計(jì)中的走線規(guī)則

2021-03-17 07:53:30

高速PCB設(shè)計(jì)的基本內(nèi)容是什么高速PCB的設(shè)計(jì)方法是什么

2021-04-27 06:33:07

在高速PCB設(shè)計(jì)過程中,由于存在傳輸線效應(yīng),會導(dǎo)致一些一些信號完整性的問題,如何應(yīng)對呢?

2021-03-02 06:08:38

解決高速PCB設(shè)計(jì)信號問題的全新方法

2021-04-25 07:56:35

高速數(shù)字PCB設(shè)計(jì)信號完整性解決方法

2021-03-29 08:12:25

在一般的非高速PCB設(shè)計(jì)中,我們都是認(rèn)為電信號在導(dǎo)線上的傳播是不需要時間的,就是一根理想的導(dǎo)線,這種情況在低速的情況下是成立的,但是在高速的情況下,我們就不能簡單的認(rèn)為其是一根理想的導(dǎo)線了,電信號

2019-05-30 06:59:24

解決方案詳解基于電磁兼容技術(shù)PCB板的設(shè)計(jì)解密PROTEL DXP軟件的PCB設(shè)計(jì)技巧簡述高速PCB設(shè)計(jì)中的常見問題及解決方法簡單介紹基于射頻開關(guān)模塊功能電路PCB板的設(shè)計(jì)PCB地線的干擾與抑制設(shè)計(jì)方法

2014-12-16 13:55:37

高速PCB設(shè)計(jì)布線系統(tǒng)的傳輸速率在穩(wěn)步加快的同時也帶來了某種防干擾的脆弱性,這是因?yàn)閭鬏斝畔⒌念l率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統(tǒng)就越容易受干擾。干擾無處不在,電纜

2016-01-06 16:43:09

的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。規(guī)則二:高速信號的走線閉環(huán)規(guī)則由于PCB板的密度越來越高

2017-11-02 12:11:12

什么是高速pcb設(shè)計(jì)高速線總體規(guī)則是什么?

2019-06-13 02:32:06

直播觀眾將獲得哪些知識點(diǎn):?快速掌握高速多層PCB設(shè)計(jì)的基本原則套路及關(guān)鍵點(diǎn)?傳輸線理論基礎(chǔ)知識以及其在PCB設(shè)計(jì)中對EMC的考量?PCB設(shè)計(jì)中EMC的基礎(chǔ)理論及設(shè)計(jì)關(guān)鍵點(diǎn)?屏蔽罩的設(shè)計(jì)?BGA的出線

2019-10-22 15:00:18

高速PCB設(shè)計(jì)指南之(一~八 )目錄 2001/11/21 一、1、PCB布線2、PCB布局3、高速PCB設(shè)計(jì)

二、1、高密度(HD)電路設(shè)計(jì)2、抗干擾技術(shù)

2008-08-04 14:14:42 0

0 高速PCB設(shè)計(jì)方法:在電信領(lǐng)域和其他電子行業(yè)領(lǐng)域的數(shù)據(jù),語音和圖像的傳輸應(yīng)用中傳輸速度已經(jīng)遠(yuǎn)遠(yuǎn)高于500MB/S,在通信領(lǐng)域人們追求的是更快的推出更高性能的產(chǎn)品,而成本并不

2009-03-25 15:31:47 0

0 高速PCB設(shè)計(jì)的疊層問題

2009-05-16 20:06:45 0

0 電容在高速PCB設(shè)計(jì)中的應(yīng)用:探討高速PCB設(shè)計(jì)電容的應(yīng)用。電容是電路板上不可缺少的一個部分,并且起到了至關(guān)重要的作用,探討他具備至關(guān)重要的價值。您在設(shè)計(jì)中是否有這樣

2009-08-16 13:11:56 0

0 高速PCB設(shè)計(jì)指南之一

第一篇 PCB布線在PCB設(shè)計(jì)中,布線是完成產(chǎn)品設(shè)計(jì)的重要步驟,可以說前面的準(zhǔn)備工作都是為它而做

2009-11-11 14:57:48 600

600 高速PCB設(shè)計(jì)指南之七

第一篇 PCB基本概念

1、“層(Layer) ”的概念 與字處理或其它許多

2009-11-11 15:07:15 433

433 高速PCB抄板與PCB設(shè)計(jì)方案

目前高速PCB的設(shè)計(jì)在通信、計(jì)算機(jī)、圖形圖像處理等領(lǐng)域應(yīng)用廣泛。而在這些領(lǐng)域工程師們用的高速PCB

2009-11-18 14:11:47 824

824 基于Cadence的高速PCB設(shè)計(jì)

隨著人們對通信需求的不斷提高,要求信號的傳輸和處理的速度越來越快.相應(yīng)的高速PCB的應(yīng)用也越來越廣,設(shè)計(jì)也越來越

2009-12-12 17:50:27 954

954 高速PCB 設(shè)計(jì)已成為數(shù)字系統(tǒng)設(shè)計(jì)中的主流技術(shù),PCB的設(shè)計(jì)質(zhì)量直接關(guān)系到系統(tǒng)性能的好壞乃至系統(tǒng)功能的實(shí)現(xiàn)。針對高速PCB的設(shè)計(jì)要求,結(jié)合筆者設(shè)計(jì)經(jīng)驗(yàn),按照PCB設(shè)計(jì)流程,對PCB設(shè)計(jì)

2011-08-30 15:44:23 0

0 簡要闡述了高速PCB設(shè)計(jì)的主要內(nèi)容, 并結(jié)合Cadence軟件介紹其解決方案比較了傳統(tǒng)高速設(shè)計(jì)方法與以Cadence為代表的現(xiàn)代高速PCB設(shè)計(jì)方法的主要差異指出在進(jìn)行高速設(shè)計(jì)過程中必須借助于

2011-11-21 16:53:58 0

0 理論研究和實(shí)踐都表明,對高速電子系統(tǒng)而言,成功的PCB設(shè)計(jì)是解決系統(tǒng)EMC問題的重要措施之一.為了滿足EMC標(biāo)準(zhǔn)的要求,高速PCB設(shè)計(jì)正面臨新的挑戰(zhàn),在高速PCB設(shè)計(jì)中,設(shè)計(jì)者需要糾正或放棄

2011-11-23 10:25:41 0

0 高速PCB設(shè)計(jì)技術(shù)(中文)

2011-12-02 14:16:44 161

161 高速PCB設(shè)計(jì)指南,大家自己有需要的趕緊下載吧,機(jī)不可失

2015-10-27 14:09:28 0

0 高速PCB設(shè)計(jì)指南.........................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計(jì)指南............................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計(jì)指南.......................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計(jì)指南,好資料,又需要的下來看看

2017-01-12 12:18:20 0

0 高速PCB設(shè)計(jì)電容的應(yīng)用

2017-01-28 21:32:49 0

0 規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有

2017-11-25 07:43:00 7511

7511

在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-03-15 14:05:42 4494

4494

在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-05-06 18:08:15 3981

3981 尤其在使用高速數(shù)據(jù)網(wǎng)絡(luò)時,攔截大量信息所需要的時間顯著低于攔截低速數(shù)據(jù)傳輸所需要的時間。數(shù)據(jù)雙絞線中的絞合線對在低頻下可以靠自身的絞合來抵抗外來干擾及線對之間的串音,但在高頻情況下,僅靠線對絞合已無法達(dá)到抗干擾的目的,只有屏蔽才能夠抵抗外界干擾。

2019-08-12 11:56:00 1855

1855 高速PCB設(shè)計(jì)布線系統(tǒng)的傳輸速率在穩(wěn)步加快的同時也帶來了某種防干擾的脆弱性,這是因?yàn)閭鬏斝畔⒌念l率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統(tǒng)就越容易受干擾。

2020-02-27 17:19:32 718

718 高速PCB設(shè)計(jì)布線系統(tǒng)的傳輸速率在穩(wěn)步加快的同時也帶來了某種防干擾的脆弱性,這是因?yàn)閭鬏斝畔⒌念l率越高,信號的敏感性增加,同時它們的能量越來越弱,此時的布線系統(tǒng)就越容易受干擾。

2019-10-28 17:01:39 1922

1922 高速PCB設(shè)計(jì)EMI有什么規(guī)則

2019-08-21 14:38:03 807

807

本文主要分析一下在高速PCB設(shè)計(jì)中,高速信號與高速PCB設(shè)計(jì)存在一些理解誤區(qū)。 誤區(qū)一:GHz速率以上的信號才算高速信號? 提到高速信號,就需要先明確什么是高速,MHz速率級別的信號算高速、還是

2019-11-05 11:27:17 10310

10310

在高速的PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。

2019-12-16 14:52:30 2976

2976

如上圖所示:在PCB設(shè)計(jì)中,時鐘等關(guān)鍵的高速信號線,走需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2

2020-06-05 10:54:04 2839

2839 高速PCB設(shè)計(jì)是指信號的完整性開始受到PCB物理特性(例如布局,封裝,互連以及層堆疊等)影響的任何設(shè)計(jì)。而且,當(dāng)您開始設(shè)計(jì)電路板并遇到諸如延遲,串?dāng)_,反射或發(fā)射之類的麻煩時,您將進(jìn)入高速PCB設(shè)計(jì)領(lǐng)域。

2020-06-19 09:17:09 1537

1537 PCB設(shè)計(jì),對后期自己的擇業(yè)或者兼職創(chuàng)業(yè)來說可選擇性廣,競爭力大! 本次《凡億90天高速PCB設(shè)計(jì)線上特訓(xùn)班》由凡億教育的名師帶隊(duì),依托于凡億教育10多年PCB設(shè)計(jì)辦學(xué)經(jīng)驗(yàn),以獨(dú)特的教學(xué)方式,幫助大家梳理PCB設(shè)計(jì)的學(xué)習(xí)方法、學(xué)習(xí)要

2022-01-27 13:59:58 3097

3097 電子發(fā)燒友網(wǎng)站提供《對物聯(lián)網(wǎng)應(yīng)用有用的繼電器屏蔽PCB設(shè)計(jì).zip》資料免費(fèi)下載

2022-07-05 14:31:07 6

6 高速PCB設(shè)計(jì)指南之七

2022-12-30 09:22:13 4

4 高速PCB設(shè)計(jì)指南之五

2022-12-30 09:22:14 3

3 高速PCB設(shè)計(jì)指南之八

2022-12-30 09:22:14 5

5 高速PCB設(shè)計(jì)指南之六

2022-12-30 09:22:15 3

3 高速PCB設(shè)計(jì)指南之四

2022-12-30 09:22:15 4

4 高速PCB設(shè)計(jì)指南二

2022-12-30 09:22:16 5

5 高速PCB設(shè)計(jì)電容的應(yīng)用

2022-12-30 09:22:16 29

29 高速PCB設(shè)計(jì)的疊層問題

2022-12-30 09:22:17 37

37 高速PCB設(shè)計(jì)電容的應(yīng)用

2023-03-01 15:37:57 2

2 尤其在使用高速數(shù)據(jù)網(wǎng)絡(luò)時,攔截大量信息所需要的時間顯著低于攔截低速數(shù)據(jù)傳輸所需要的時間。數(shù)據(jù)雙絞線中的絞合線對在低頻下可以靠自身的絞合來抵抗外來干擾及線對之間的串音,但在高頻情況下(尤其在頻率超過250MHz以上時)

2023-11-21 11:51:50 175

175 高速PCB設(shè)計(jì)當(dāng)中鋪銅處理方法

2023-11-24 18:03:58 263

263

PCB設(shè)計(jì)之高速電路

2023-12-05 14:26:22 290

290

挑戰(zhàn)性的任務(wù)。本文將介紹高速PCB設(shè)計(jì)中常見的射頻電路類型,以及每一種的處理方法和注意事項(xiàng)。 1. 高速PCB設(shè)計(jì)中的射頻類型 高速PCB設(shè)計(jì)中的射頻電路通常包括以下幾種類型: 1.1 射頻前端電路 射頻前端電路是接收和處理射頻信號的入口,它通常包括天線、低噪聲放

2023-11-30 07:45:01 317

317

電子發(fā)燒友App

電子發(fā)燒友App

評論