電路功能與優勢

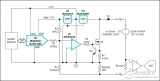

圖1所示電路使用業界功耗最低且尺寸的HART?1兼容型IC調制解調器AD5700和16位電流輸出和電壓輸出DACAD5422,構成完整的HART兼容型4 mA至20 mA解決方案。該電路中采用 OP184,使得IOUT和VOUT引腳能夠短接在一起,從而減少可編程邏輯控制(PLC)模塊應用中所需的螺絲連接數量。為了進一步節省空間,AD5700-1 提供了精度為0.5%的內部振蕩器。

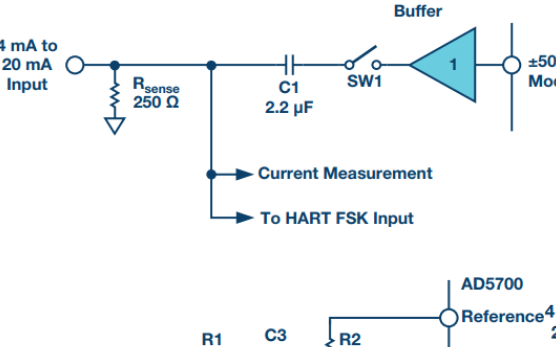

圖1. AD5422 HART使能電路原理示意圖

應用筆記 AN-1065 描述了為符合HART通信標準而對AD5420 IOUT DAC進行配置的方式。AN-1065概述了AD5700HART調制解調器輸出如何進行衰減并通過CAP2引腳交流耦合至AD5420。AD5422也是如此。然而,如果應用中涉及特別惡劣的環境,則可采用一種電源抑制特性更加的替代電路配置。這種替代電路要求使用外部RSET電阻,并涉及到將HART信號耦合至AD5420或AD5422的RSET引腳。CN-0270描述了AD5420的這種解決方案,通常是在線路供電的發射器應用中。目前的電路筆記與AD5422相關;與AD5420不同,該器件提供電壓和電流輸出引腳,因此特別適合PLC/分布式控制系統(DCS)應用。AD5422提供40引腳LFCS和24引腳TSSOP封裝,這點與電路特性的相關性將在“電路描述”部分加以介紹。

該電路符合由HART通信基金會定義的HART物理層規范,例如靜默期間輸出噪聲和模擬變化率規格。

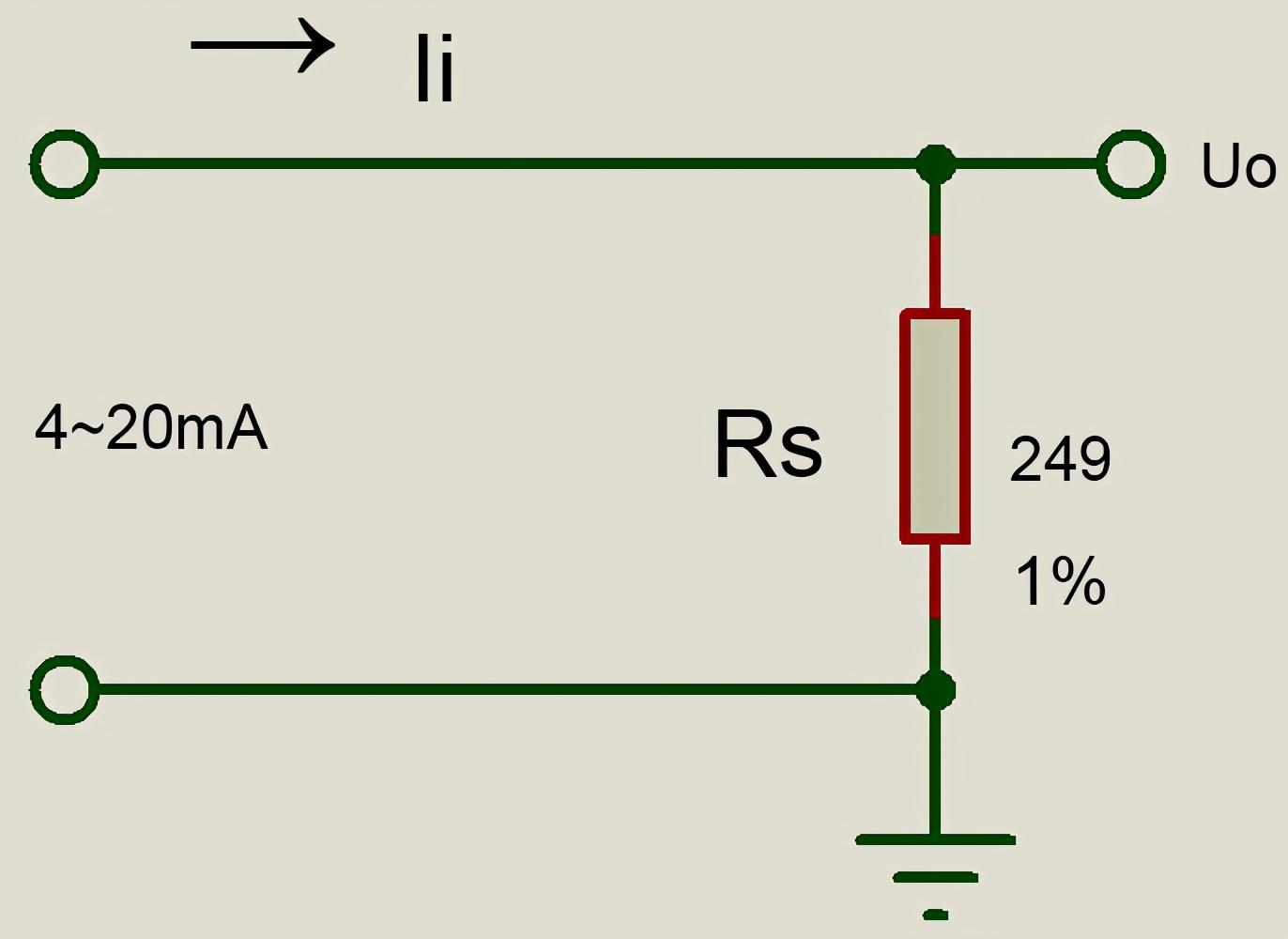

多年來,過程控制儀器儀表中一直使用4 mA至20 mA通信。此通信方式穩定可靠,對長距離通信中的環境干擾具有高抗擾度。不過,其限制是每次只能進行一個過程變量的單向通信。

可尋址遠程傳感器高速通道(HART)標準的開發實現了高性能的雙向數字通信,同時支持傳統儀器儀表設備所使用的4 mA至20 mA模擬信號。它衍生出各種特性,例如遠程校準、故障查詢和額外過程變量的傳輸。簡言之,HART是一種數字雙向通信,可在4 mA至20 mA模擬電流信號之上調制一個1 mA峰峰值頻移鍵控(FSK)信號。

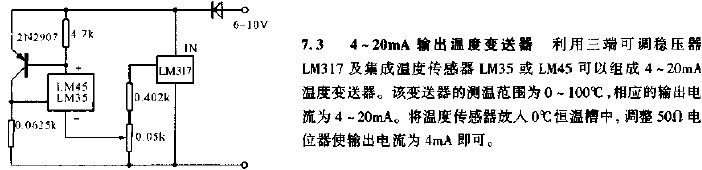

電路描述

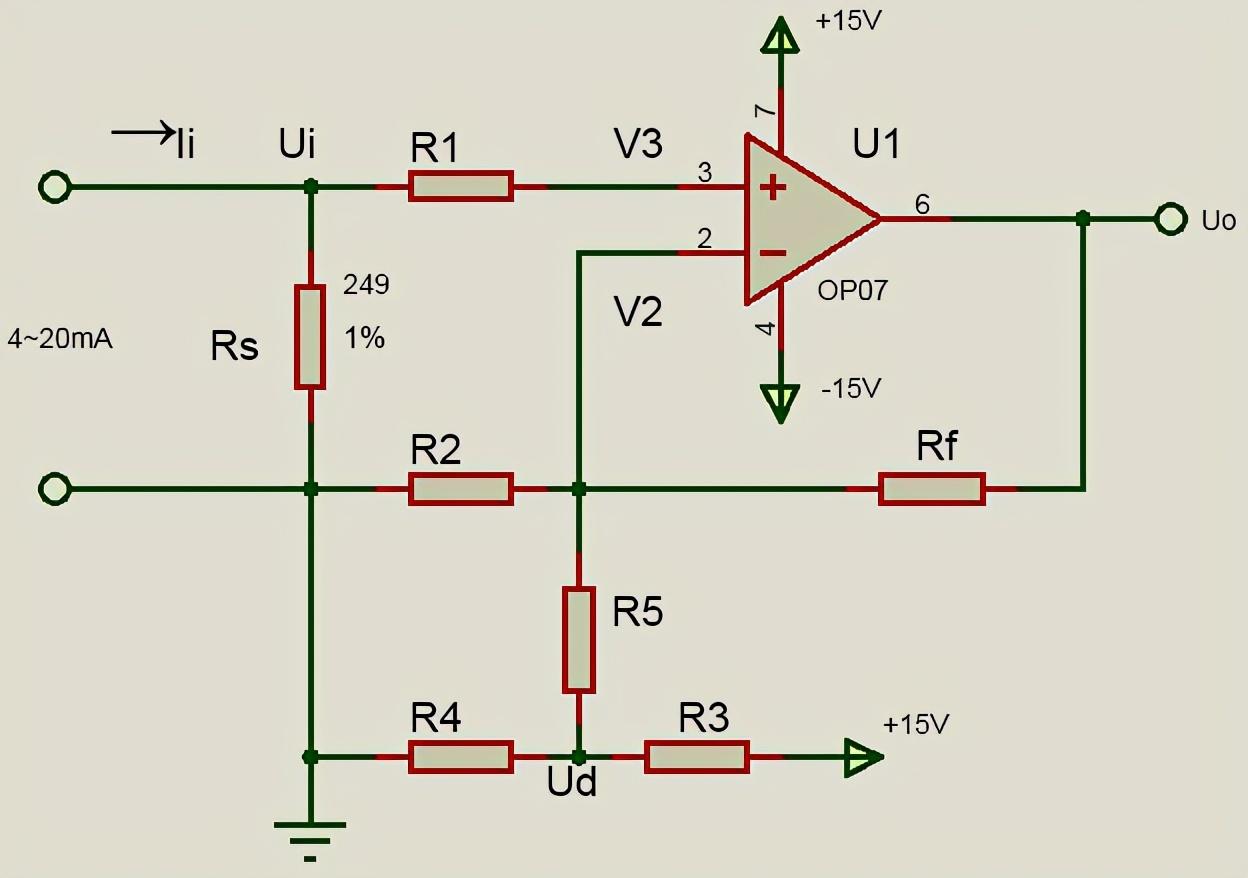

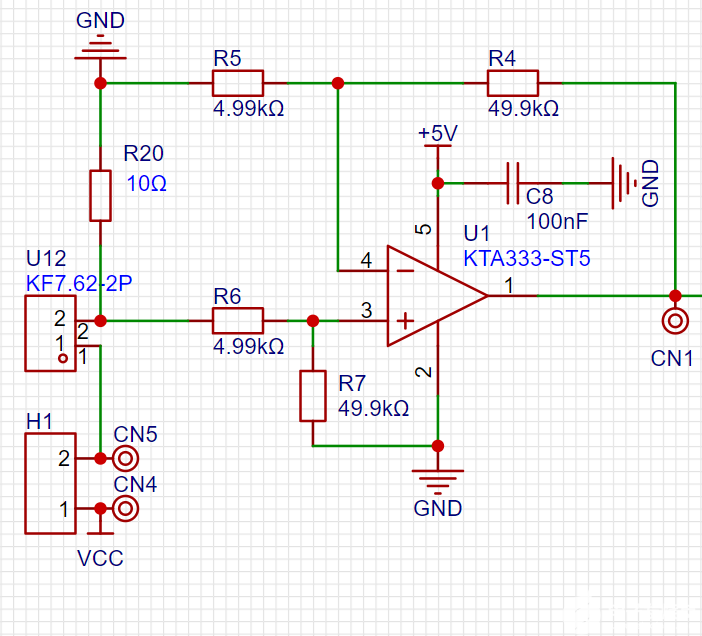

圖1顯示AD5422如何與AD5700 HART調制解調器和UART接口配合使用,以使PLC和DCS系統常用的4 mA至20 mA電流輸出支持HART。如果應用無需短接IOUT和VOUT引腳,則不一定需要連接至+VSENSE引腳的緩沖器。來自AD5700的HART_OUT信號經衰減后,交流耦合至AD5422的RSET引腳。如果未使用外部RSET電阻,通過CAP2引腳連接AD5422和AD5700的替代方法請參見應用筆記AN-1065,如前文所述。此方法只適用于AD5422的40引腳LFCSP封裝選項,因為引腳數量較少的24引腳TSSOP封裝沒有CAP2引腳。

雖然本電流電路筆記中描述的方法需要使用外部RSET電阻,但其電源抑制性能卻高于替代應用筆記解決方案。無論使用哪一種解決方案,AD5700 HART調制解調器輸出均可在不影響電流直流電平的前提下調制4 mA至20 mA模擬電流(如圖2所示)。二極管保護電路(D1至D4)將在“瞬態電壓保護”部分詳細論述。

圖2. AD5700/AD5700-1樣片調制器波形

確定外部元件值

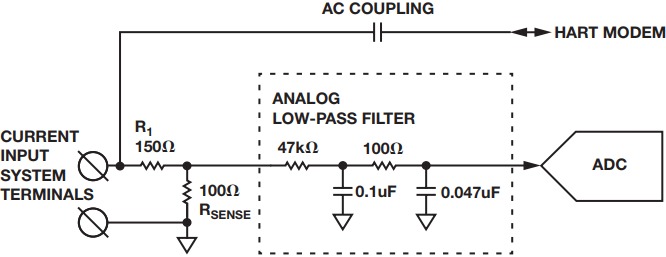

C1和C2電容可配合器件的數字壓擺率控制功能使用,以控制AD5422的IOUT信號壓擺率。確定電容的絕對值時,要確保調制解調器的FSK輸出無失真通過。因此,調制解調器輸出信號的帶寬必須通過1200 Hz和2200 Hz頻率。圖3顯示了實現此要求的電路。在此情況下,C2(如圖1所示)保持開路。

圖3. AD5422和AD5700 HART調制解調器連接

低通和高通濾波器電路通過RH、CL、CH和C1的相互作用并配合AD5422的一些內部電路來形成。在計算這些元件的值時,低通和高通頻率截止點目標分別為》10 kHz和《500 Hz。圖4顯示了仿真頻率響應的曲線圖,表1顯示了增加各元件而剩余元件值保持恒定對頻率響應的影響。

圖4. 仿真頻率響應

表1. 個別元件值增加對頻率響應的影響

調制解調器的輸出是一個FSK信號,包括1200 Hz和2200Hz移頻。這個信號必須轉換為1 mA峰峰值電流信號。為此,RSET引腳上的信號幅度必須衰減。這是因為AD5422采用內部電流增益配置設計。假定調制解調器的輸出幅度為500 mVp-p,則其輸出必須經過500/150 = 3.33倍衰減。此衰減通過RH和CL來實現。

本電路筆記中的測量使用以下元件值完成:

C1 = 4.7 nF

RH = 27 kΩ

CL = 4.7 nF

CH = 8.2 nF

圖5表明在500Ω負載電阻上分別測得了1200 Hz和2200 Hz移頻。通道1顯示耦合至AD5422輸出中的調制HART信號(設置為輸出4 mA),通道2則顯示AD5700 TXD信號。

圖5. 在500Ω負載上測得的FSK波形

HART兼容性

圖1中的電路要與HART兼容,必須符合HART物范。HART規范文檔中包含了眾多物理層規范。其要的兩個是靜默期間輸出噪聲和模擬變化率。

靜默期間輸出噪聲

當HART設備沒有進行傳輸(靜默)時,不應在HART擴展頻帶中將噪聲耦合到網絡上。噪聲過高可能會干擾設備本身或網絡上其它設備對HART信號的接收。

對于在500Ω負載上測得的電壓噪聲,其包含的擴展頻帶中的寬帶噪聲和相關噪聲總和不能超過2.2 mV rms。此噪聲通過在500Ω負載上連接HCF_TOOL-31濾波器(可從HART通信基金會獲得)并將濾波器輸出連接到真均方根測量儀(參見圖6)來測量。也可使用示波器來檢查輸出波形峰峰值電壓。

AD5422 輸出電流設置為4 mA、12 mA和20mA。對于所有這三個輸出電流值,有帶通濾波器時的結果十分相似,不過電流輸出值增加時,寬帶寬噪聲也略有增加。在輸出電流為4 mA的情況下,使用和不使用HCF_TOOL-31帶通濾波器時,測得的均方根值分別為143μV rms和1.4μV rms。這兩個值均在要求的2.2 mV rms(使用HART濾波器)和138 mVrms(不使用HART濾波器的寬帶噪聲)規范內。在輸出電流為12 mA的情況下,使用和不使用HCF_TOOL-31帶通濾波器時,測得的均方根值分別為158μV rms和2.1μV rms,這兩個值同樣都在HART協議規范要求的范圍內。

圖6. HART規范測試電路

圖7和圖8分別顯示4 mA和12 mA輸出電流的示波器曲線圖。注意,濾波器的通帶增益為10。每個曲線圖上的通道1和通道2分別顯示濾波器的輸入和輸出。

圖7. 輸出電流為4 mA時HART濾波器輸入(通道1)和輸出(通道2)端的噪聲

圖8. 輸出電流為12 mA時HART濾波器輸入(通道1)和輸出(通道2)端的噪聲

模擬變化率

此規范可確保當設備調節電流時,模擬電流的最大變化率不會干擾HART通信。電流的階躍變化會擾亂HART信號。仍然使用如圖6所示的相同測試電路。為進行這個測試,AD5422被編程為輸出一個4 mA至20 mA切換的周期波形,該波形在兩個值上都沒有延遲,以獲得最大變化率。為了符合HART規范,濾波器輸出端波形的峰值電壓不能大于150 mV。符合這一要求可確保模擬信號的最大帶寬處于規定的直流至25 Hz頻帶中。

AD5422輸出從4 mA變為20 mA的正常時間約為10μs。這個速度顯然太快,而且會對HART網絡造成重大破壞。為了降低變化率,AD5422提供了兩種特性:一是在CAP1和CAP2引腳處連接電容,二是提供內部線性數字壓擺率控制功能(詳情請參考AD5422數據手冊)。對于較快的壓擺率,可在與AD5422通信的控制器/FPGA上實施一個非線性數字斜坡發生器。

要使帶寬降低到25 Hz以下,需要在CAP1和CAP2引腳處連接非常大的電容值。最佳解決方案是結合使用外部電容和AD5422的數字壓擺率控制功能。兩個電容C1和C2的作用是降低模擬信號的變化率;不過還不足以滿足規范。使能壓擺率控制功能可以為變化率的設置提供靈活性。

圖9. AD5422輸出(通道1)和HART濾波器輸出(通道2),SR時鐘= 3,SR階躍= 2,C1 = 4.7 nF,C2 = NC

圖9顯示了AD5422的輸出和HART濾波器的輸出。濾波器輸出端的峰值電壓為82 mV,處于規定范圍以內。壓擺率設置為SR時鐘= 3和SR階躍= 2,從4 mA至20 mA的轉換時間設為約120 ms,C1 = 4.7 nF,C2未連接。如果這個變化率太低,可以縮短壓擺時間。采用C1 = 4.7 nF且C2未連接的電路配置時,可以發現壓擺時間設為80 ms(SR時鐘= 1,SR階躍= 2)時,所得到的模擬變化率符合HART規范。然而,如果將壓擺時間進一步縮短至60 ms(SR時鐘= 0,SR階躍=2),則會導致結果超出150 mV規格范圍。從CAP1連接至AVDD的電容可用于抵消濾波器輸出端因壓擺時間過快而導致的峰值電壓增加。然而,選擇此值時必須小心,因為它會影響“確定外部元件值”部分討論的低通濾波器截止頻率。

圖10顯示了壓擺率控制設置改為SR時鐘= 5、SR階躍= 2且C1電容值保持4.7 nF不變的結果。這樣,轉換時間就會在240 ms左右。濾波器輸出端的峰值幅度可通過增加C1值、配置更慢的壓擺率或通過兩者的組合來進一步降低。

圖10. AD5422輸出(通道1)和HART濾波器輸出(通道2),SR時鐘= 5,SR階躍= 2,C1 = 4.7 nF,C2 = NC

瞬態電壓保護

AD5422 內置ESD保護二極管,可防止正常操作造成的損害。但是,工業控制環境會使I/O電路遭受高得多的瞬變。為了防止過高瞬態電壓影響AD5422,可能需要外部功率二極管和浪涌電流限制電阻,如圖1所示。對電阻值的約束條件(圖1中顯示為18Ω)是,在正常工作期間,IOUT的輸出電平必須保持在其順從電壓限值(AVDD ? 2.5 V)以內,并且這兩個保護二極管和電阻必須具有適當的額定功率。在18Ω的條件下,對于4 mA至20 mA輸出,引腳處的順從限值降低V = IMAX × R = 0.36 V。 OP184 緩沖器的正輸入端還連接了一個10 kΩ電阻,用以限制瞬態期間的電流來保護放大器。通過瞬態電壓抑制器(TVS)或瞬態吸收器可實現進一步的保護。這些元件包括單向和雙向抑制器,可提供各種各樣的隔離和擊穿電壓額定值。TVS應盡量采用最低擊穿電壓定標,同時在電流輸出的功能范圍內不導通。建議保護所有遠程連接節點。

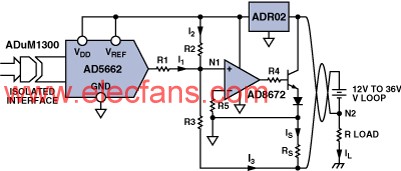

在許多過程控制應用中,需要在控制器與受控單元之間提供一個隔離柵,以保護和隔離控制電路,防止危險的共模電壓破壞電路。

ADI公司的iCoupler系列產品可隔離高于2.5 kV的電壓。為了減少所需隔離器的數量,CLEAR等非關鍵信號可以連到GND;FAULT和SDO可以不連接,從而只需要隔離三個信號。不過請注意,FAULT或SDO引腳是訪問AD5422的故障檢測功能所必需的。

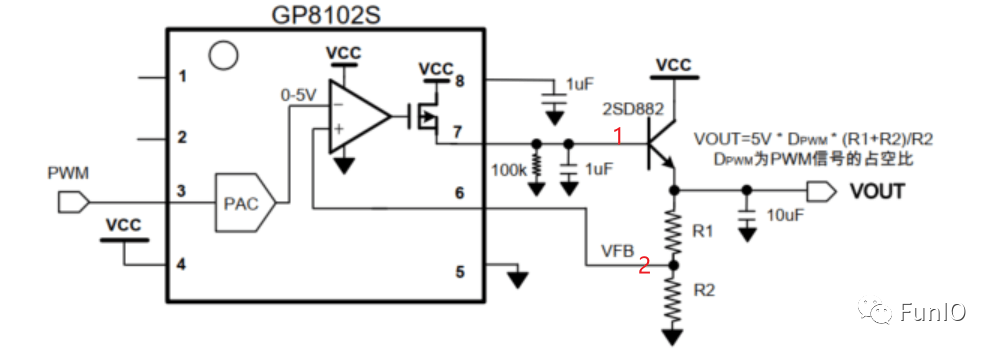

常見變化

圖1所示電路的一個常見變化是使用 AD5422AD5420,它類似于AD5422,但只有一個電流輸出。因此,其輸出端沒有OP184緩沖器配置。這種AD5420和AD5700 HART調制解調器電路詳見CN-0270。電路筆記CN-0065提供有關IEC61000兼容解決方案的額外信息,該解決方案適合使用AD5422和ADuM1401數字隔離器的全隔離式輸出模塊。電路筆記CN-0233包含有關提供電源和數據隔離的信息,所使用的是ADuM3471 PWM控制器和具有四通道隔離器的變壓器驅動器。

如果需要多個通道,可使用AD5755-1四通道電壓和電流輸出DAC。該產品具有創新型片內動態電源控制功能,在電流模式下,可以最大限度地降低封裝功耗。各通道均有一個相應的CHARTx引腳, 因此HART信號可以耦合至AD5755-1的電流輸出端。

電路評估與測試

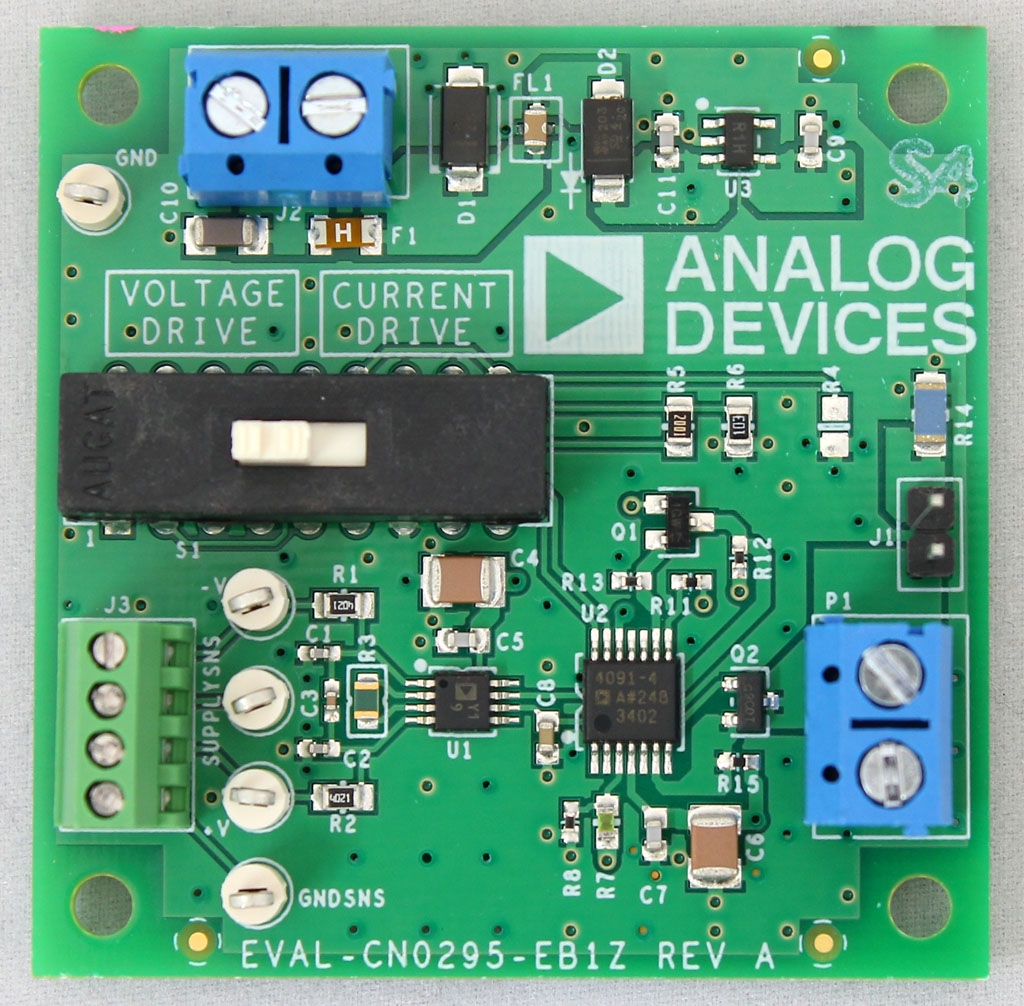

要構建此電路, 需要使用 AD5422評估板 ( EVAL-AD5422EBZLFCSP P版本)和 AD5700-1評估板 (EVAL-AD5700-1EBZ)1EBZ),參見圖11。除了這兩個評估板之外,該電路還需要三個外部電容(C1、CH和CL)、一個電阻(RH)、一個負載電阻(RL)、一個緩沖放大器以及一個UART接口。

設備要求 需要以下設備:

AD5422 評估板( EVAL-AD5422EBZ LFCSP版本)

AD5700 評估板( EVAL-AD5700-1EBZ)

主機控制器和UART接口(標準微控制器, 例如 ADuC7060)

10.8 V至60 V的電源

數字測試濾波器(HCF_TOOL-31,可從HART通信基金會獲得)

500Ω負載電阻

OP184 放大器(位于單獨的試驗板上且帶有連接線)

外部電容C1 (4.7 nF)、CH (8.2 nF)和CL (4.7 nF);電阻RH (27 kΩ)

Tektronix DS1012B示波器或等同產品

圖11. 測試設置框圖

靜默期間噪聲測量 AD5422 LFCSP

如前文所述,對于靜默測試期間的輸出噪聲,AD5700調制解調器并未在發射數據(靜默)。AD5422設置為輸出所需的電流并通過HART通信基金會帶通濾波器。接著使用Tektronix TDS1012B示波器測量輸出噪聲;結果顯示輸出噪聲在HART通信基金會協議規范要求的范圍內。

模擬變化率測量 — AD5422 LFCSP

模擬變化率規范可確保當AD5422調節電流時,模擬電流的最大變化率不會干擾HART通信。電流的階躍變化會擾亂HART信號。為進行這個測試,AD5422被編程為輸出一個4 mA至20 mA切換的周期波形,該波形在兩個值上都沒有延遲,以獲得最大變化率。所用的壓擺率設置為SR時鐘= 3和SR階躍= 2,C1設置為4.7 nF,C2保持開路。

此外,再將SR時鐘設置改變為5而不是3,并保持其它所有設置和元件值不變,從而進一步降低壓擺率,由此另外進行測量;至于相關影響,可比較圖9和圖10來得出。

靜默期間噪聲測量 —AD5422 TSSOP

另外還執行了額外測量,以模擬AD5422 TSSOP封裝選項在這種配置下的表現;不過,沒有連接在CAP1引腳的電容(C1)(因為此器件的TSSOP版本沒有CAP1引腳)。

雖然與有C1的LFCSP器件相比,沒有C1時測得的靜默期間輸出噪聲值更大,但還是在HART通信基金會協議規范要求的范圍內。圖12和圖13中的通道2顯示了有HCF_TOOL-31濾波器時的寬帶噪聲,IOUT為4 mA時結果為530μV rms,IOUT為12 mA時結果為690μV rms。可將這些曲線圖與圖7及圖8進行比較,以體現有無C1的影響如何。

圖12. 無C1且輸出電流為4 mA時HART濾波器輸入(通道1)和輸出(通道2)端的噪聲

圖13. 無C1且輸出電流為12 mA時HART濾波器輸入(通道1)和輸出(通道2)端的噪聲

模擬變化率測量 — AD5422 TSSOP

從模擬變化率測試的角度來看,無論有無C1,最大峰值結果都相似。主要區別在于,沒有C1時,峰峰值本底噪聲要大得多。圖14和圖15分別是壓擺率為120 ms(SR時鐘= 3和SR階躍= 2)和240 ms(SR時鐘= 5和SR階躍= 2)時的模擬變化率曲線圖。

圖14. AD5422輸出(通道1)和HART濾波器輸出(通道2),SR時鐘= 3,SR階躍= 2,C1 = NC,C2 = NC

圖15. AD5422輸出(通道1)和HART濾波器輸出(通道2),SR時鐘= 5,SR階躍= 2,C1 = NC,C2 = NC

同樣,可將這些曲線圖與圖9及圖10進行比較,以體現有無C1的影響如何。雖然這種電路配置中所用的HART耦合技術要求采用外部RSET電阻,但請注意,即使該電路的HART部分未實施,添加緩沖器也會在使用內部RSET電阻時造成IOUT精度略微降低。因此,在使用這種緩沖器配置將電壓和電流輸出引腳連接在一起時,建議使用外部RSET電阻。

電子發燒友App

電子發燒友App

評論