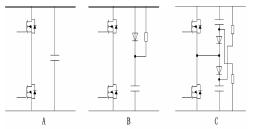

MAX101A芯片內部是由采樣率為250兆/秒的完全獨立的兩個ADC拼在一起而得到的,從模擬信號輸入、參考電壓到數字信號輸出都是完全分開的兩部分。這樣做給與用戶很大的自由度,但同時也帶來一個問題,那就是很難確定在每一次上電后究竟是哪一個ADC先輸出,從而無法正確地進行數據鎖存。MAX101A要求用戶提供一個外加的控制信號TRK1和TRK1來確定兩個ADC的先后順序。它規定在系統采樣時鐘的下降沿到來時,如果TRK1為“1”,/TRK1為“0”則第一個ADC輸出有效,反之則第二個ADC輸出有效(圖4)。這樣的控制信號實現起來并不難,但MAX101A對TRK1和/TRK1的邏輯電平范圍的規定是一個非常規的值,它規定輸入電平在±50mV之間為邏輯“1”,在-350mV到-500mV之間為邏輯“0”。對于這樣一種非標準的時鐘電路,不可能用現成的芯片直接產生,為此在模擬偽真結果的基礎上,采用了圖5所示的電路來產生這樣的時鐘信號。D觸發器將時鐘信號二分頻后經隔直電容送到電阻分壓網絡進行衰減,同時提供新的基準電平,這樣原來的ECL信號(-900mV~-1800mV)就被轉換成在0~-450mV之間的時鐘信號,滿足了MAX101A的要求。電容隔直方法在高速數字電路中應用十分廣泛,應用這種方法可以很方便地將不同電平范圍的信號(如ECL和PECL)進行相互轉換而不需要額外的電路,使用起來相當方便。

?

2.4 高速數據的鎖存

高速ADC的數據鎖存在A/D系統里的設計一直都是一個難點,ADC的速度越高數據鎖存的難度就越大。盡管MAX101A的數字輸出已經分成了A、B兩個端口,使每個數據通道的速率降為250Mbyte/s,但要將如此速度的數據準確無誤的鎖存下來還是相當困難的,必須進一步降低數據端口的輸出速率。降低端口速率唯一的辦法就是將輸出端口的數據分成多路交替輸出,使每一路的數據產生率降到可以接受的速度。但是分的路數越多,電路就越龐大,各種時鐘與數據之間的關系也就越復雜。綜合兩者考慮,采取了將ADC的輸出分成八路的方案,這樣每一路的數據產生率為62.5Mbyte/s,完全可以用普通的鎖存器來完成。數據鎖存部分的結構如圖6所示。MAX101A輸出的鎖存時鐘(250MHz)經四分頻后送入一個六位的移位寄存器產生6個相差4ns的時鐘,其中的ABCD用于鎖存各個端口的數據,CDEF經電平轉換后作為EPLD鎖存數據的時鐘,之所以推遲兩個時鐘是為了補償數據的傳輸延時和EPLD內部FIFO的建立時間。數據進入到EPLF后,后端的處理就方便得多了,可以用EPLD作DRAM控制接口將FIFO的數據存儲到大容量的DRAM中去,也可將數據分組打包通過傳輸介質傳遞給計算機進行處理。在本系統中,采取第二種方法將數據通過電纜傳遞給位于計算機內的一塊PCI卡上,計算機再通過它把數據存放到硬盤上。

3 高速電路的設計

在高速電路中如何避免各個信號之間的串擾(crosstalk),以及如何保證信號的完整性(integrality)是整個系統正常工作的保障。首先,對于高速電路電路板(PCB)應至少采用四層以上的多層板技術,本系統采用了六層板(表1).采有多層板的目的并不僅僅是為了走線的方便,更重要的是使用了大面積的電源或地層之后可以使各信號線與地或電源平面之間形成一個緊耦合從減少信號線之間的串擾。通常所用的在走線層大面積網格鋪地的方法,雖然也可起到一定的屏蔽作用,但其面積和與信號線距離的關系遠不如地平面產生的效果好。其次,系統的整體布局要合理,應該綜合考慮地平面和電源層的分割。使用相同電源和地的芯片,布局盡量放在一起以避免地平面被瑣碎的分割。當同一塊電路板上既有模擬電路也有數字電路時,更應該仔細地考慮這兩部分的布局。模擬部分和數字部分應該隔離,不僅是空間的隔離,而且電源也應該隔離,兩部分最好單獨供電。最后,模擬地和數字地通過磁珠(ferrite bead)在一點相連。地平面上的電流一般比較大,大電流流過時會對表面上的器件產生一公平的影響,尤其是對模擬器件產生的影響將直接反映在輸出信號質量的好壞。為了減少地電流的影響,在設計地平面時應該在比較敏感的模擬器件下方加一道隔離溝阻斷大電流的通路(如圖7所示),以減小地電流對它的影響。

表1

名 稱 用途說明

頂層 布線、元件

中間層1 模擬地、VTT

中間層2 數字地、ECL的VCC

中間層3 模擬+5V、數字+5V、數字+3.3V

中間層4 模擬-5V、數字-5V、數字+2.5V

底層 布線

高速電路的PCB設計是整個系統成敗的關鍵,PCB的設計在很大程序上與所選用的EDA工具有關。在本系統的PCB設計上選用的是PADS公司出品的PowerPCB,它和傳統的設計工具Protel相比有如下優點:

(1)支持圓弧拐角布線,減少信號線的輻射,降低串優;

(2)支持淚滴焊盤,使走線阻抗變化均勻,減少反射;

(3)可以方便地在PCB的內部層進行分割和走線;

(4)支持多種布線規則,如布線長度、走線阻抗等規則;

(5)與自動布線器Specctra接口方便;

(6)直接支持信號完整性分析軟件HyperLynx。

?

鑒于以上種種優越性能,它非常適合于高速電路板的PCB設計。

電子發燒友App

電子發燒友App

評論