近年來對芯片的高速數據處理的要求,使得許多芯片內部都已經搭載了高速IF的功能。但是,也正是由于它的高速性能造成芯片的測試變得非常的困難。對這類高速IF芯片的初期評價階段,一般采用的是多種計測器的綜合評價。但是針對多管腳的高速IF芯片,單純利用計測器的測定,會面對許多問題。

T6683+5G Option

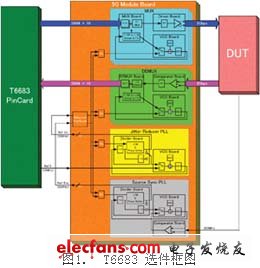

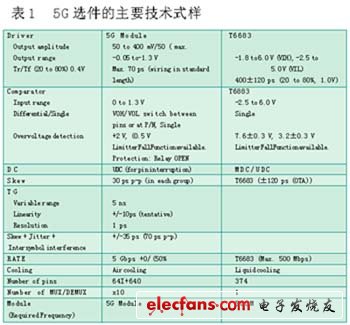

為了實現精確的高速差分串行信號測試,我們開發了可以對應最大5Gbps差分信號的ATE用高速測試選件。這次開發的可以提供最大5Gbps的高速專用PE(圖1),內藏于ATE系統中,其包括:64個高速輸入專用通道+ 64個高速輸出專用通道的Dr·Cp(驅動·比較)以及10:1的MUX/DEMUX。采用的ATE系統為愛德萬測試的高速SoC測試系統T6683。T6683擁有1024個IO通道以外,還有1024個輸出專用通道。與前面介紹的由計測器組成的測試系統比較起來,可以容易地控制系統時序的同步。另外,也可以容易地對通道間的個別相位進行調整。 表1列出了5G選件的主要技術式樣。

個別特殊測試要求對應XDR

5G選件采用的是10:1MUX,也可以設定為8:1。由于XDR的Idling狀態時的差分輸出的Pos/Neg兩方電壓需要固定為同一值上,5G選件的Pos/Neg的兩輸出電壓可以根據需要嚴格地固定在同一電壓值。這個電壓控制是由8:1模式時沒有用到的另外2個Bit來進行。

高速測試系統的基本技術

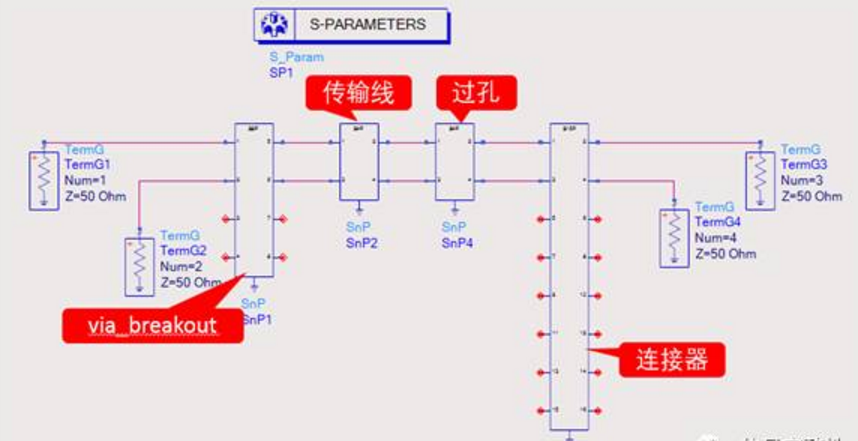

對于超過數Gbps的信號處理,高速信號專用芯片技術、高速信號傳送技術等非常重要。近年來芯片的設計/制造技術的發展使得芯片本身對高速信號的處理性能有了很大的提高,因此從芯片將高速信號輸出后的傳送問題成為了高速信號處理的重點。如何能夠把GHz的高速信號,以最小Jitter及最小衰減的性能在與芯片之間傳送/接收是要面對的最重要的課題。在下面我們要針對高速測試系統必要的基礎要素技術進行探討。

(1)時鐘(Timing)發生

(2)測試系統PE到被測芯片之間的高速信號傳送

用戶評論

共 0 條評論