信號(hào)完整性測(cè)量已成為開(kāi)發(fā)數(shù)字系統(tǒng)過(guò)程中的關(guān)鍵步驟。信號(hào)完整性問(wèn)題,如串?dāng)_、信號(hào)衰減、接地反彈等,在傳輸線效應(yīng)也很關(guān)鍵的較高頻率下會(huì)增加。

?

當(dāng)今的高級(jí)功能電子產(chǎn)品規(guī)定使用在1 至 10 GHz 的高頻范圍(RF/微波)下工作的HDI PCB 。這種增加的頻率會(huì)導(dǎo)致信號(hào)響應(yīng)的邊緣更陡峭。電路板變得越來(lái)越緊湊,布線密度逐漸變緊,導(dǎo)致串?dāng)_基本分析的重要性。

隨著更快的邊緣速度產(chǎn)生相對(duì)于總線長(zhǎng)度更短的波長(zhǎng),EMI 會(huì)上升,從而產(chǎn)生意外的輻射發(fā)射。這些輻射會(huì)增加串?dāng)_,并可能導(dǎo)致高速 PCB 設(shè)計(jì)在 EMI/EMC 測(cè)試期間失敗。

PCB中的串?dāng)_是什么?

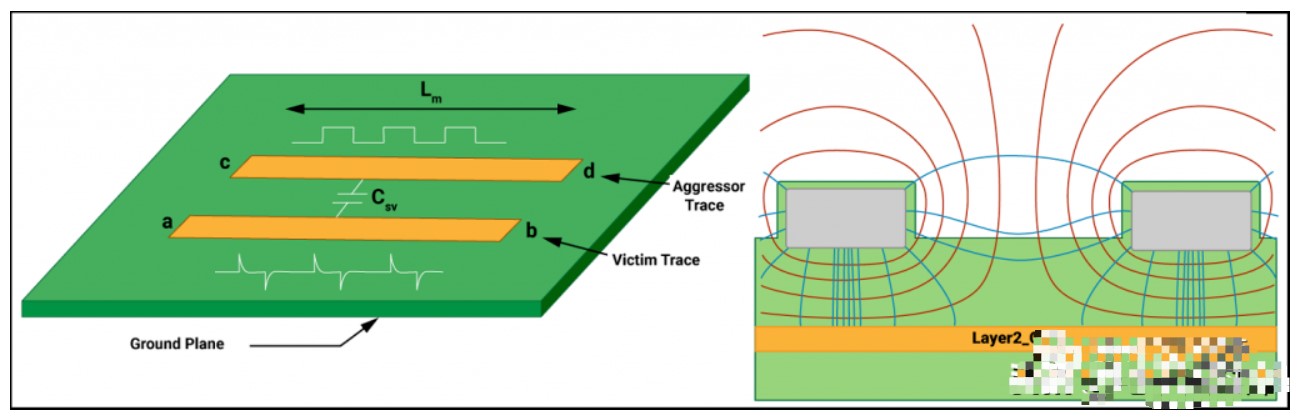

串?dāng)_是由一個(gè) PCB 跡線到另一個(gè) PCB 跡線的能量耦合引起的干擾,即使它們沒(méi)有接觸。換言之,高速 PCB中緊密間隔走線之間不需要的電磁耦合稱(chēng)為串?dāng)_。它是由于電場(chǎng)(電容耦合)和磁場(chǎng)(電感耦合)的干擾而發(fā)生的。磁場(chǎng)產(chǎn)生互感,電場(chǎng)在附近的走線之間產(chǎn)生互電容。互感負(fù)責(zé)在相鄰(受害者)線路上感應(yīng)電流,這與入侵線路中的電流相反。并且由于互電容形成的電容器將在受害線路上雙向通過(guò)電流。它阻礙了電路板的信號(hào)完整性。

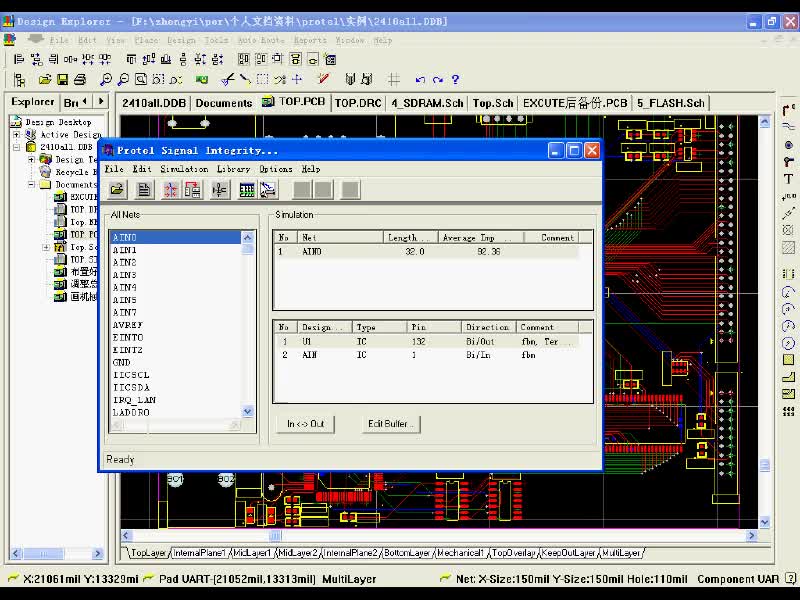

使用 SI 工具的仿真可以確定初始布局布線后的串?dāng)_。雖然,它有時(shí)仍然未被發(fā)現(xiàn)。如果在初始階段不加以控制,串?dāng)_可能會(huì)降低電路板的功能。基本上,這都是關(guān)于邊緣電場(chǎng)和磁場(chǎng),它們不受限制,而是散布在附近區(qū)域。

?

受害跡線 (ab) 中引起的串?dāng)_

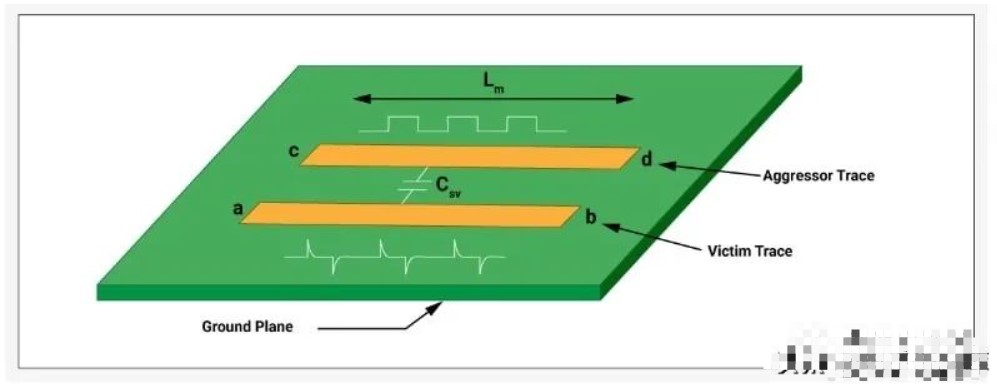

當(dāng)兩條跡線在同一層中彼此相鄰運(yùn)行或在相鄰層中一條在另一條的頂部上方運(yùn)行時(shí),就會(huì)出現(xiàn)串?dāng)_。考慮在同一方向運(yùn)行的兩條跡線。如果流經(jīng)一條跡線的信號(hào)幅度高于另一條跡線,則可能會(huì)影響流經(jīng)另一條跡線的信號(hào)。在這里,具有較高幅度的跡線將被稱(chēng)為“攻擊者”,而另一條跡線被稱(chēng)為“受害者”。

在這種情況下,受害跡線中的信號(hào)將開(kāi)始模仿入侵跡線的特征阻抗,而不是傳導(dǎo)自己的信號(hào)。當(dāng)這種情況發(fā)生時(shí),這意味著串?dāng)_已經(jīng)侵入了系統(tǒng)。

串?dāng)_對(duì) PCB 的影響

-

降低電路板的信號(hào)完整性

-

時(shí)間延遲

-

電壓過(guò)沖

-

誤觸發(fā)導(dǎo)致邏輯功能混亂

串?dāng)_如何在系統(tǒng)中引起噪聲?

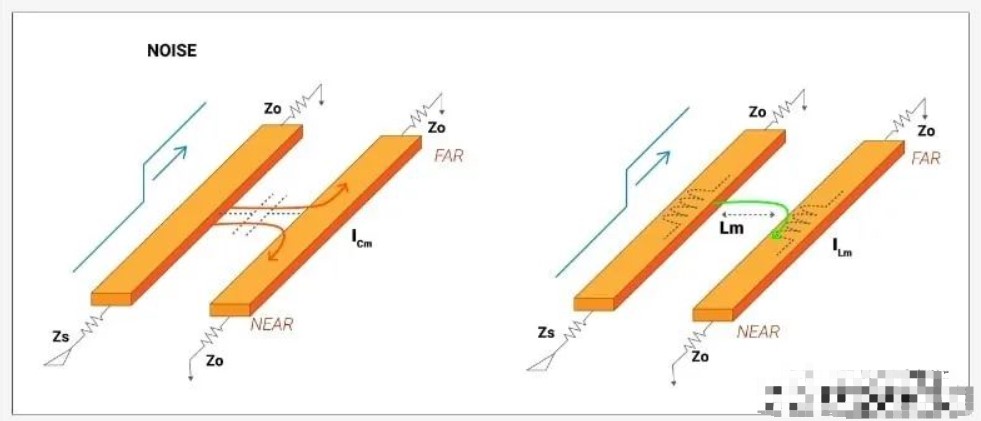

每個(gè)電信號(hào)都有不同的電磁場(chǎng)。每當(dāng)這些場(chǎng)重疊時(shí),它們就會(huì)產(chǎn)生電感、電容或傳導(dǎo)耦合,從而導(dǎo)致 EMI。串?dāng)_使干擾信號(hào)超過(guò)了受干擾信號(hào),即使它們沒(méi)有物理連接但非常接近。串?dāng)_分為普通阻抗耦合和電磁場(chǎng)耦合。當(dāng)多個(gè)信號(hào)共享一個(gè)公共返回路徑時(shí),會(huì)發(fā)生易于分析的公共阻抗耦合。電磁場(chǎng)耦合進(jìn)一步分為電容耦合和電感耦合,這是最受關(guān)注的因素。

由互電容和電感引起的串?dāng)_

傳統(tǒng)的用筆和紙分析串?dāng)_不僅麻煩而且耗時(shí)。我們可以做的是考慮電路元件來(lái)估計(jì)耦合。由邊緣電場(chǎng)引起的耦合由電容器(互電容)近似,由電感器(互感)評(píng)估由邊緣磁場(chǎng)引起的耦合。

電場(chǎng)變化引起的電容耦合

在平面上平行工作的兩條跡線充當(dāng)由電介質(zhì)隔開(kāi)的電容器的平行板。侵略者和受害者之間的電場(chǎng)變化被建模為一個(gè)電容器。我們知道如果電容器中電壓發(fā)生變化,電場(chǎng)發(fā)生變化,就會(huì)感應(yīng)出位移電流。這里,電容耦合電流就是我們所說(shuō)的串?dāng)_。這種效應(yīng)稱(chēng)為寄生電容。要了解更多信息,請(qǐng)閱讀如何減少 PCB 布局中的寄生電容。

互容性和感性耦合

通過(guò)磁場(chǎng)環(huán)進(jìn)行電感耦合

磁耦合或電感耦合近似于圍繞受害者旋轉(zhuǎn)多少磁場(chǎng)環(huán)。受害者周?chē)那致哉弋a(chǎn)生的磁場(chǎng)變化導(dǎo)致傳導(dǎo)電流發(fā)生變化。因此,根據(jù)法拉第感應(yīng)定律,在受害線上感應(yīng)出電壓。該感應(yīng)電壓以串?dāng)_的形式驅(qū)動(dòng)電流。

寬邊耦合

通常,串?dāng)_發(fā)生在同一層上的兩條相鄰走線之間。除此之外,周?chē)尚‰娊橘|(zhì)隔開(kāi)的平行跡線會(huì)導(dǎo)致串?dāng)_。該電介質(zhì)厚度可以是4 密耳 (0.1mm) 或小于兩條跡線之間的間距。這被稱(chēng)為寬邊耦合。

有哪些不同類(lèi)型的串?dāng)_?

以下是不同類(lèi)型的串?dāng)_:

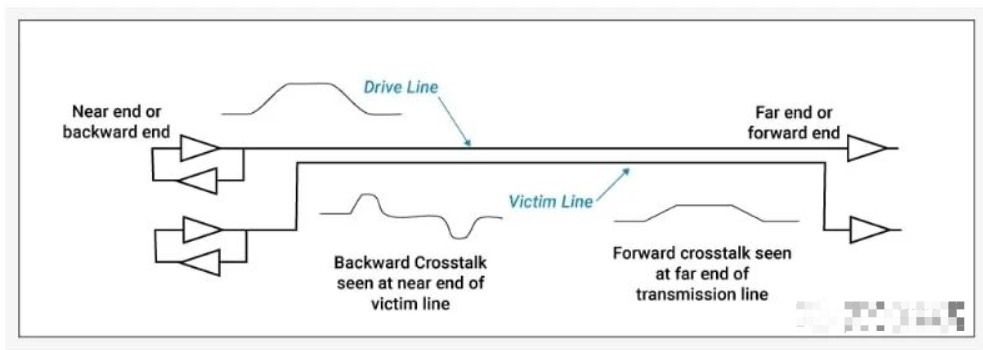

基于傳播方向

-

前向串?dāng)_:它沿著干擾信號(hào)的方向傳播。

前向串?dāng)_ = 電容耦合 - 電感耦合

-

反向串?dāng)_:它以與干擾信號(hào)相反的方向傳播。

反向串?dāng)_ = 電容耦合 + 電感耦合

前向和后向串?dāng)_

基于測(cè)量區(qū)域近端串?dāng)_(NEXT):它是指受害線路驅(qū)動(dòng)器側(cè)的噪聲。遠(yuǎn)端串?dāng)_(FEXT):?它是受害線路接收端的干擾。

近端和遠(yuǎn)端串?dāng)_

NEXT 和 FEXT 是相對(duì)于施加刺激的端口進(jìn)行測(cè)量的。它可以發(fā)生在線路的任何地方,無(wú)論是雙導(dǎo)體還是單端。

差分 NEXT 和 FEXT 測(cè)量

注意:NEXT 值以分貝 (dB) 表示,并隨傳輸頻率而變化。NEXT 的更高 dB 意味著更少的干擾。

基于量化

-

Power-sum-NEXT(PS-NEXT):近端串?dāng)_的絕對(duì)或相對(duì)功率。PSNEXT 給出了所有相鄰線對(duì)的總串?dāng)_,并涉及測(cè)量與功率相關(guān)的所有線對(duì)到線對(duì)分組。

-

Power-sum-FEXT (PS-FEXT):遠(yuǎn)端串?dāng)_的絕對(duì)或相對(duì)功率。

-

Power-sum-equal-level-crosstalk (PS-ELFEXT):?PS-NEXT 和 PS-FEXT 之和。

外星串?dāng)_

外來(lái)串?dāng)_非常復(fù)雜,不能通過(guò)相位抵消輕易消除。在這里,不同頻率的多個(gè)信號(hào)與受害信號(hào)混合在一起,當(dāng)必須增加帶寬以獲得更快的響應(yīng)時(shí),情況會(huì)變得更糟。屏蔽不足以防止這種情況發(fā)生。 串?dāng)_也可以使用 TDR 來(lái)測(cè)量。有關(guān)更多詳細(xì)信息,請(qǐng)閱讀我們關(guān)于TDR 阻抗測(cè)量如何工作的文章。

S 參數(shù)

S 參數(shù)描述了 PCB 中互連的微波特性。每個(gè) S 參數(shù)元素基本上是從互連的終端出來(lái)的正弦波與進(jìn)入另一個(gè)互連的起始端的正弦波的比率。由于它們是正弦波的比率,因此每個(gè)元素(S31 和 S41)都是復(fù)雜的。標(biāo)準(zhǔn)阻抗始終為 50Ω。

S 參數(shù)用于串?dāng)_的基本分析。它們會(huì)自動(dòng)檢測(cè)信號(hào)進(jìn)入的端口和信號(hào)輸出的端口。確定線路中發(fā)生多少串?dāng)_以及受擾線路上的噪聲方向至關(guān)重要。由于這個(gè)事實(shí),受害者線的兩端被單獨(dú)標(biāo)記。S31 是離干擾源最近的受害線路端的噪聲,稱(chēng)為近端串?dāng)_。S31反向傳播。遠(yuǎn)端串?dāng)_是從受害者相對(duì)于干擾信號(hào)的最遠(yuǎn)端口測(cè)量的。它向前傳播。

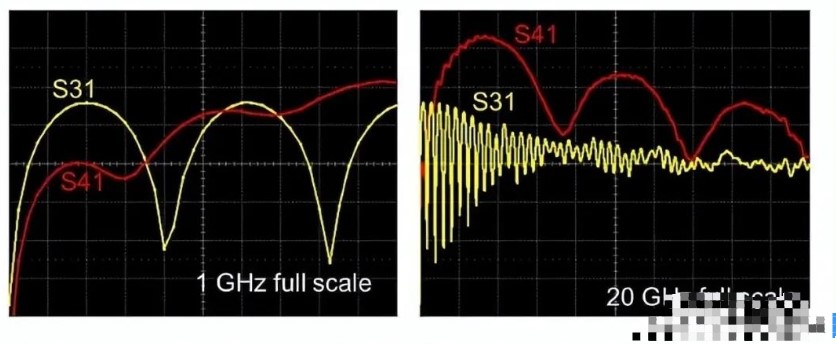

力克羅 VNA 結(jié)果。圖片來(lái)源:EDN

即使 S31 和 S41 測(cè)量由同一攻擊者引起的同一受害者的噪聲,它們的值也不同。此處可以通過(guò) Le croy 信號(hào)完整性網(wǎng)絡(luò)分析儀顯示。

在這兩種情況下,垂直刻度均為 40db 滿量程,而左側(cè)的水平刻度為 1 GHz 滿量程,右側(cè)為 20 GHz。S31和S41的區(qū)別在這里可以很明顯的看出。我們還可以使用矢量網(wǎng)絡(luò)分析儀 (VNA) 探測(cè) s 參數(shù)。要了解有關(guān)此的更多信息,請(qǐng)參閱使用矢量網(wǎng)絡(luò)分析儀進(jìn)行 s 參數(shù)測(cè)量。

如何測(cè)量串?dāng)_?

串?dāng)_通常指定為出現(xiàn)在受擾線上的信號(hào)相對(duì)于干擾線的百分比。它也可以用低于驅(qū)動(dòng)線路電平的 dB 表示。NEXT 隨傳輸頻率而變化,因?yàn)楦叩念l率會(huì)產(chǎn)生更多的干擾。dB 值越高,受干擾的鏈路/通道接收到的串?dāng)_就越少。FEXT 是根據(jù)系統(tǒng)S 參數(shù)的串?dāng)_元素計(jì)算得出的。

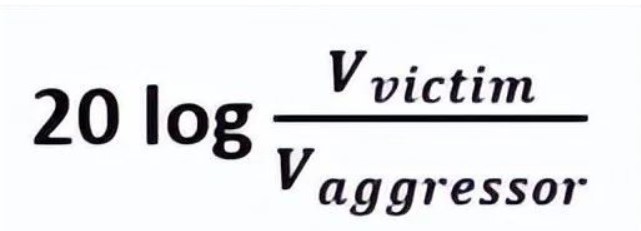

串?dāng)_的公式由下式給出:

在哪里:

K 是一個(gè)常數(shù),其值始終小于 1,取決于電路的上升時(shí)間和經(jīng)歷串?dāng)_的走線長(zhǎng)度。

H2 是平行走線高度的乘積。

D2 是跡線中心線之間的直接距離的乘積。

上式清楚地表明,可以通過(guò)減小 H 和最大化 D 來(lái)最小化串?dāng)_。

以 dB 為單位的串?dāng)_由下式給出:

?

其中,Vvictim是受害線上的電壓, Vaggressor是干擾線上的電壓。

影響串?dāng)_大小的因素

-

攻擊者線和受害者線之間的耦合程度

-

發(fā)生耦合的距離

-

使用的終止類(lèi)型的有效性

差分對(duì)中如何引起串?dāng)_?

差分對(duì)中的串?dāng)_

每當(dāng)微分系統(tǒng)中出現(xiàn)不平衡時(shí),場(chǎng)就不再完全抵消,這導(dǎo)致它們與不平衡成比例地輻射。類(lèi)似地,外部場(chǎng)可以在差分對(duì)中感應(yīng)出幅度不相等且相位相反的電流,因此它們不再相互抵消。產(chǎn)生的電流稱(chēng)為共模電流。與差模相比,共模串?dāng)_對(duì)系統(tǒng)性能的不利影響更大。

在頻率方面比較共模和差模串?dāng)_效應(yīng)。圖片來(lái)源:英特爾

串?dāng)_的原因是什么?

電容和電感耦合:電容耦合是由于寄生電容,而電感耦合是由于互感。

-

傳播速度差異:可以通過(guò)走線長(zhǎng)度匹配和傳播延遲匹配來(lái)避免。

-

PCB 通孔:帶有短截線的 PCB 通孔會(huì)產(chǎn)生反射,從而產(chǎn)生振鈴,從而產(chǎn)生串?dāng)_。避免這種情況的一種方法是回鉆過(guò)孔。

-

增加的數(shù)據(jù)速率:隨著數(shù)據(jù)速率的增加,上升時(shí)間也會(huì)增加。根據(jù)法拉第定律,隨著上升時(shí)間的增加,串?dāng)_也會(huì)增加。減少此類(lèi)信號(hào)之間的串?dāng)_的一種方法是增加跡線之間的間距。

-

電路板尺寸:隨著電路板尺寸的增加,走線長(zhǎng)度也會(huì)增加,這些走線就像天線一樣。因此,盡可能縮短走線長(zhǎng)度非常重要。

減少串?dāng)_的設(shè)計(jì)指南

在高頻板中串?dāng)_是不可避免的。我們能做的就是減輕它,讓它變得微不足道。以下是一些避免串?dāng)_的快速流行技術(shù):

在走線之間保持足夠的間隔

在走線之間提供足夠的間隔(采用 3W 規(guī)則)。如果沒(méi)有保持足夠的分離,則會(huì)增加互電容 (Cm)。3W 規(guī)則將串?dāng)_降低了 70%。要實(shí)現(xiàn) 98% 的串?dāng)_減少,請(qǐng)選擇 10W。

使用實(shí)體參考平面

使用固體參考平面或返回路徑是為了吸收邊緣電場(chǎng)和磁場(chǎng)。因此,它們不能擴(kuò)散開(kāi)來(lái)并對(duì)其他信號(hào)產(chǎn)生噪聲。

利用隔離的傳輸線

串?dāng)_是由干擾跡線到受干擾跡線上引起的,因此很明顯,較高的干擾電壓會(huì)引起更多的串?dāng)_。因此,最好根據(jù)信號(hào)幅度對(duì)網(wǎng)絡(luò)組進(jìn)行隔離。此策略可防止較大的電壓網(wǎng)絡(luò) (3.3V) 影響較小的電壓網(wǎng)絡(luò) (1.5V)。

實(shí)施背鉆過(guò)孔

通孔短截線會(huì)降低信號(hào)完整性,因此會(huì)增加串?dāng)_。這可以通過(guò)實(shí)施背鉆來(lái)減少。

減少并行跟蹤運(yùn)行

較長(zhǎng)的走線(超過(guò) 500 密耳)會(huì)增加互感,從而增加串?dāng)_。

采用正交路由

正交布線相鄰信號(hào)層,以盡量減少它們之間的電容耦合。

不要減少信號(hào)上升時(shí)間

減少的信號(hào)上升時(shí)間會(huì)增加串?dāng)_。

選擇差分對(duì)路由

緊密耦合的差分路由消除了串?dāng)_,因?yàn)閬?lái)自干擾源的噪聲平等地耦合到差分對(duì)的兩個(gè)分支中,從而產(chǎn)生共模噪聲。差分對(duì)抑制有助于減少串?dāng)_的共模噪聲。

使用長(zhǎng)度較短的跡線

在實(shí)際設(shè)計(jì)中,并不總是可以使用相互垂直的信號(hào)。那么盡可能短的走線長(zhǎng)度是減少耦合機(jī)會(huì)的可行技術(shù)。

隔離高頻信號(hào)

像時(shí)鐘信號(hào)這樣的高頻信號(hào)應(yīng)該與其他信號(hào)隔離,以減少串?dāng)_的可能性。

隔離異步信號(hào)

異步信號(hào)必須遠(yuǎn)離高速信號(hào)。由于它們?cè)谡k娐凡僮髦泻苌偈褂茫覀兛梢詫⑺鼈兎胖迷?a target="_blank">電源線附近。

使用保護(hù)痕跡

保護(hù)走線用于控制傳輸線之間的電容串?dāng)_。應(yīng)明智地使用此類(lèi)走線,因?yàn)樗鼈儠?huì)使布線變得困難。

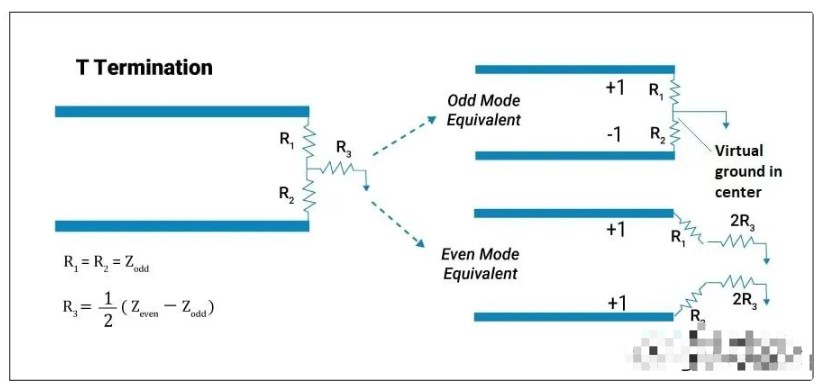

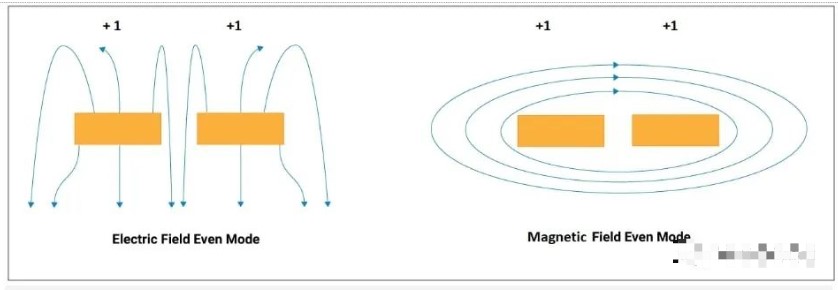

正確終止偶模和奇模傳輸

三電阻網(wǎng)絡(luò)(T 端接)可用于端接奇偶模式。

?

用于偶模和奇模傳輸?shù)?T 端接

串?dāng)_極限

確保整個(gè)系統(tǒng)串?dāng)_不超過(guò) 150mV。

串?dāng)_如何影響傳輸線參數(shù)?

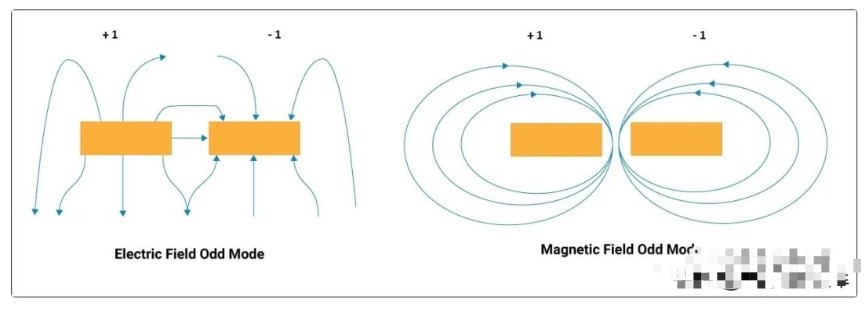

傳輸線可以稱(chēng)為雙導(dǎo)體系統(tǒng),其中兩條獨(dú)立的走線影響信號(hào)通過(guò)它們的傳播。可以考慮兩種傳播模式:偶模式(線同相)和奇模式(線 180 度異相)。

在奇模傳輸中,兩條線路之間將存在相當(dāng)大的電位差。這個(gè)電位差將增加等于互電容值的有效電容。

?

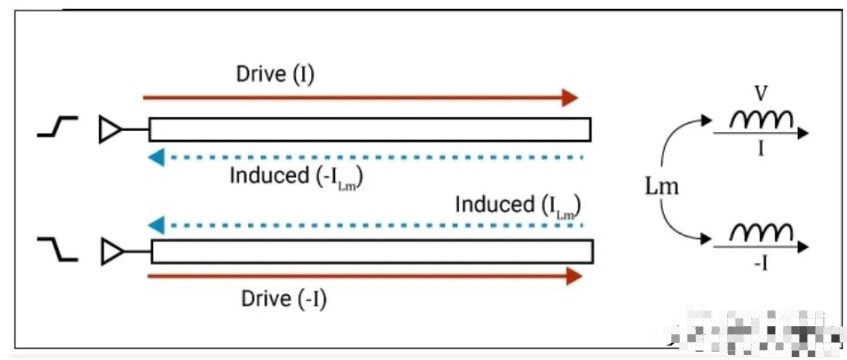

奇模傳輸期間的場(chǎng)線

由于兩條線路中的電流以相反的方向流動(dòng),因此總電感會(huì)減少互感 (Lm) 值。

?

奇模傳輸期間的電流

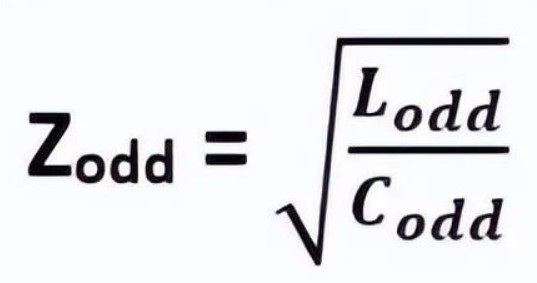

奇模的傳輸線阻抗由下式給出:

?

注意 Z 微分 = 2Zodd

奇模的傳輸線傳播延遲由下式給出:

?

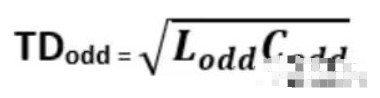

在偶數(shù)模式傳輸中,兩條線路(受害者和攻擊者)將始終具有相等的潛力。這將通過(guò)互電容值降低有效電容。

?

偶模傳輸期間的場(chǎng)線

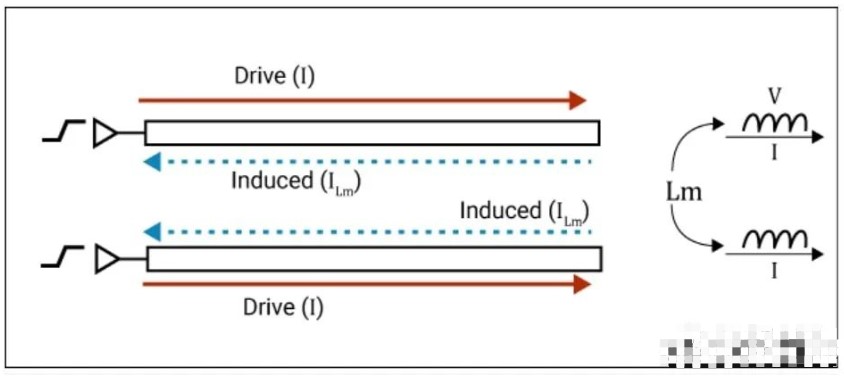

由于兩條線路中的電流沿相同方向流動(dòng),因此總電感會(huì)增加互感 (Lm) 值。

?

偶模傳輸期間的電流

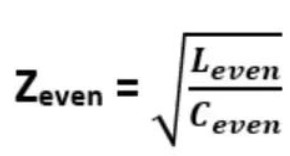

偶模的傳輸線阻抗由下式給出:

?

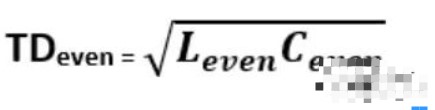

偶模的傳輸線傳播延遲由下式給出:

?

不同傳輸線中的串?dāng)_

電容耦合電流沿順時(shí)針和逆時(shí)針?lè)较騻鞑ァU螂娏魍话l(fā)偶然與入侵信號(hào)同時(shí)發(fā)生。因此,由于電容耦合導(dǎo)致的遠(yuǎn)端串?dāng)_增加。反向電流反復(fù)回傳,使近端串?dāng)_的幅度相同,但持續(xù)時(shí)間較長(zhǎng)。在這兩個(gè)方向上,電壓脈沖都是正的。

電感耦合電流順時(shí)針循環(huán)。正向和反向的現(xiàn)象與電容耦合相同,只是這里的電壓脈沖導(dǎo)致正向的遠(yuǎn)端串?dāng)_是負(fù)的。

電容和電感耦合電流

在帶狀線中,信號(hào)線上方和下方的環(huán)境是均勻的。因此,來(lái)自?xún)蓚€(gè)耦合的遠(yuǎn)端串?dāng)_將相互抵消。但是,如果我們將微帶線作為傳輸線引入,情況就不匹配了。微帶上方有空氣,下方是電介質(zhì)。介質(zhì)的差異導(dǎo)致遠(yuǎn)端串?dāng)_升高。基本上電介質(zhì)是電耦合的原因。因此,我們可以得出結(jié)論,在微帶傳輸線的情況下,我們可以減少電容耦合,但會(huì)增加遠(yuǎn)端串?dāng)_。有關(guān)詳細(xì)信息,請(qǐng)閱讀微帶線和帶狀線有什么區(qū)別?

串?dāng)_不能在系統(tǒng)級(jí)減少。集成的建模和表征周期可用于減輕器件或封裝級(jí)別的串?dāng)_。如果控制不當(dāng),它可能會(huì)使您的電路板無(wú)法正常工作。即使 PCB 設(shè)計(jì)人員確保跡線之間的最小間隔,它可能還不足以解決相關(guān)問(wèn)題。

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論