文章作者:陜西省西安交通大學 陳文潔 楊 旭 楊拴科 王兆安

摘要:分析了傳統(tǒng)大功率電力電子器件普遍采用的封裝結構和互連方式存在的問題,對目前電力電子集成模塊集成與封裝技術進行了分類和比較,介紹各種新型封裝結構與互連方式原理、結構設計方法。

關鍵詞:電力電子集成 封裝 互連

如何使電力電子裝置的效率更高、體積更小、重量更輕、成本更低、更加可靠耐用,長期以來一直是各設計、生產者不斷努力和追求的方向。解決這一問題最為有效的途徑,是采用系統(tǒng)集成的方法使多種電力電子器件組合成為標準化模塊,并封裝為一體,構成集成電力電子模塊。

集成電力電子模塊既不是某種特殊的半導體器件,也不是一種無源元件。它是按照最優(yōu)化電路拓撲和系統(tǒng)結構的原則而設計出的包含多種器件的集成組件或模塊。除了具備有功率半導體器件外,還包含驅動電路、控制電路、傳感器、保護電路、輔助電源及無源元件。

集成與封裝技術作為電力電子集成模塊的一個重點研究方向,主要研究模塊的集成和封裝工藝。目前已有越來越多的學者認識到,能否真正將集成模塊的概念付諸實現(xiàn),在很大程度上取決于集成和封裝的工藝技術。

1、傳統(tǒng)封裝結構與互連方式存在的主要問題

1.1 封裝技術是研究電力電子集成模塊的核心問題

電力電子集成的基本思路可以分成單片集成和多芯片混合集成兩種。由于高壓、大電流的主電路和其它低壓、小電流電路的集成工藝完全不同,還有高壓隔離和傳熱的問題,因此,目前僅在數(shù)十瓦的功率范圍內實現(xiàn)了單片集成。電力電子集成封裝技術的主要發(fā)展方向為混合集成,即將不同工藝的硅片封裝在一個模塊中。

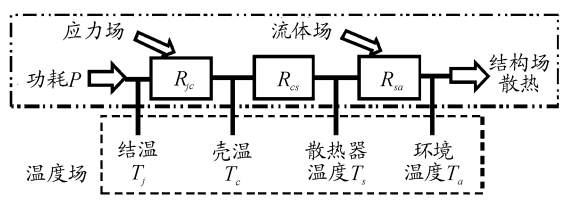

混合集成中,首先面臨的是集成模塊的封裝問題。與普通IC不同,集成模塊的封裝更主要是使模塊具備更大的電流承載能力,更高的功率密度和更高效的散熱能力。另一方面,對集成模塊封裝技術的研究是研究與之相關的各類問題的基礎和平臺。主電路、控制電路等的優(yōu)化設計與實現(xiàn),模塊內的電磁兼容問題、寄生參數(shù)等的分析,控制、傳感技術以及高效的散熱方式等等,幾乎所有相關研究都必須在此基礎上展開。

具體到封裝技術,又涉及模塊的封裝結構、模塊內芯片與基板的互連方式、各類封裝材料(導熱、填充、絕緣)的選取、制備的工藝流程等許多問題。由于集成模塊無論在功能和結構上都與傳統(tǒng)IC或功率器件存在巨大差異,因此新型的模塊封裝結構和與之相適應的引線工藝又是封裝技術中重點并且首先需要研究的問題。

1.2 傳統(tǒng)封裝結構與互連方式存在的主要問題

傳統(tǒng)的電力電子器件或模塊,雖然外形封裝樣式多種多樣,但其采用的封裝結構形式以平面型為主。然而對于電力電子集成模塊,由于隔離和散熱等問題,難以將功率芯片、控制芯片等多個不同工藝的硅片采用平面型結構安裝在同一塊底板上。

引線工藝主要解決裸芯片的各電極如何與基板互連的問題。傳統(tǒng)電力電子器件采用的互連工藝主要有鍵合與壓接兩種方式。前者適用于電流容量為50~600A的器件,由于工藝成熟、成本低,應用較為廣泛;后者適用于電流超過500~3000A的器件。然而,這兩種互連方式由于其固有的缺陷,均不能簡單照搬到電力電子集成模塊上。其中壓接方式的缺陷主要體現(xiàn)在對管芯、壓塊、底板等零件平整度要求很高,否則不僅使模塊的接觸熱阻增大,而且會損傷芯片,嚴重時使芯片碎裂;要保證施加合適的壓力,壓力過大,會損傷芯片;壓力過小,不僅使正向峰值壓降、熱阻增大,而且會使這兩個參數(shù)不穩(wěn)定;由于熱應力會使彈簧片等緊固件發(fā)生較大的塑性形變,使加在芯片上的壓力發(fā)生變化,造成正向峰值壓降和熱阻不穩(wěn)定;工藝設備復雜,成本,高,殼內零件較多易引起芯片沾污。

引線鍵合技術本身存在諸多技術缺陷表現(xiàn)在:多根引線并聯(lián)會產生鄰近效應,導致同一硅片的鍵合線之間或同一模塊內的不同硅片的鍵合線之間電流分布不均;由于高頻大電流通過互相平行的引線產生電磁場,由此形成的電磁力容易造成引線老化;引線鍵合工藝的寄生電感很大,會給器件帶來較高的開關過電壓,形成開關應力;引線本身很細,又普遍采用平面封裝結構,傳熱性能不夠好;引線和硅片作為不同的材料,二者熱膨脹系數(shù)的差異會產生熱應力等等。

因此,低寄生參數(shù)、高性能、能有效傳熱、高可靠性的新型電力電子集成模塊的封裝結構和互連方式成為電力電子模塊集成工藝中研究的主要問題。

2、新型封裝結構與互連方式的研究現(xiàn)狀

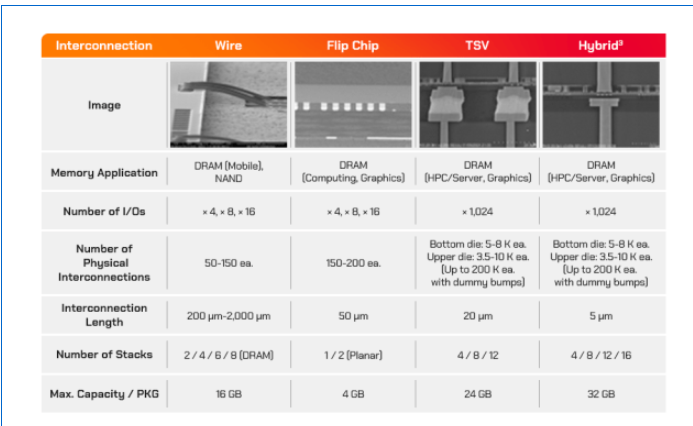

為了獲得高性能的電力電子集成模塊,以混合封裝技術為基礎的多芯片模塊 (Multi-Chip Module--MCM)封裝是目前國際上該領域研究的主流方向。隨著三維混合封裝技術的發(fā)展,目前的MCM已不只局限于將幾塊芯片平面安裝在一塊襯底上,而是采用埋置、有源基板或疊層技術,在三維空間內將多個不同工藝的芯片互連形成完整功能的模塊。 將MCM技術用于電力電子集成封裝的研究,核心內容是研究具有高載流能力、低漏感、高可靠性、三維傳熱能力和低成本、便于制造的互連和封裝工藝,從而解決寄生參數(shù)、散熱和可靠性問題。目前,國際上已提出多種技術方案,根據(jù)其互連方式大體可以劃分為兩類:以焊接技術為基礎的互連工藝和以沉積金屬膜(薄膜或厚膜)為基礎的互連工藝。

2.1 焊接技術為基礎的互連工藝

以焊接技術為基礎的互連工藝普遍采用疊層型三維封裝結構, 即把多個裸芯片或多芯片模塊(MCM)沿Z軸層層疊裝、互連,組成三維封裝結構。疊層型三維封裝的優(yōu)點是工藝相對簡單,成本相對較低,關鍵是解決各層間的垂直互連問題。根據(jù)集成功率模塊的特殊性,主要利用焊接工藝將焊料凸點、金屬柱等焊接在芯片的電極引出端,并與任一基板或芯片互連。目前的技術方案包括焊料凸點互連(Solder Ball Interconnect)和金屬柱互連平行板結構(Metal Posts Interconnected Parallel Plate Structures--MPIPPS)等。

即把多個裸芯片或多芯片模塊(MCM)沿Z軸層層疊裝、互連,組成三維封裝結構。疊層型三維封裝的優(yōu)點是工藝相對簡單,成本相對較低,關鍵是解決各層間的垂直互連問題。根據(jù)集成功率模塊的特殊性,主要利用焊接工藝將焊料凸點、金屬柱等焊接在芯片的電極引出端,并與任一基板或芯片互連。目前的技術方案包括焊料凸點互連(Solder Ball Interconnect)和金屬柱互連平行板結構(Metal Posts Interconnected Parallel Plate Structures--MPIPPS)等。

(1)焊料凸點互連(Solder Ball Interconnect)

該技術利用焊料凸點代替引線構成芯片電極的引出端,并常與倒裝芯片技術(Flip-Chip Technology)結合,以進一步縮短引線間距。倒裝芯片技術是在芯片的輸入/輸出端利用平面工藝制成焊料凸點焊球,將芯片面朝下,直接貼裝在基片上,利用回流焊工藝使芯片焊球和基板焊盤之間形成焊點,實現(xiàn)芯片與基板的電、熱、機械連接。焊料凸點互連的優(yōu)點在于省略了芯片和基板之間的引線,起電連接作用的焊點路徑短、接觸面積大、寄生電感/電容小,封裝密度高。

圖1所示為采用焊料凸點互連的集成電力電子模塊的結構示意圖。在模塊的結構設計中采用了柔性電路板,并與倒裝芯片技術相結合,使功率芯片借助焊料凸點倒扣在柔性電路板上,而芯片的另一面經(jīng)DBC板與散熱器固定。應用焊料凸點互連方式的集成功率模塊的缺點在于:由于芯片的熱膨脹系數(shù)和底板的熱膨脹系數(shù)存在熱膨脹失配,因此在芯片服役(工作時發(fā)熱,不工作時冷卻)中,熱膨脹失配嚴重。在熱循環(huán)加載下,焊點內產生很大的周期性塑性形變,萌生裂縫并擴展,使焊點很快疲勞失效。

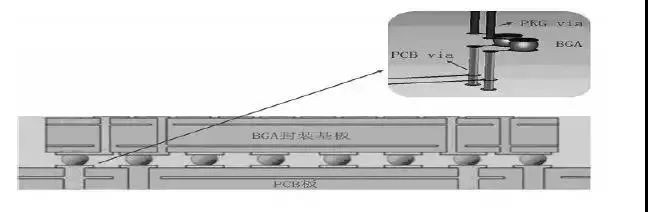

文獻對焊料凸點互連技術進行了改進。一方面通過應用底充膠(underfill)技術,即在芯片和基板間隙填充聚合物,機械耦合了芯片與基板的熱膨脹失配,提高焊點壽命;另一方面將焊料凸點互連技術與球柵陣列封裝(Ball Grid Array--BGA)相結合,進一步減小了集成模塊的電氣寄生參數(shù),提高了散熱性能。圖2為采用球柵陣列工藝技術構成的集成電力電子模塊。除采用類似的三維疊層封裝結構外,由于是在硅片表面以陣列方式制出球形觸點作為引腳,不僅使封裝尺寸更為縮小,達到與芯片尺寸封裝(Chip Scale Package --CSP)接近的封裝密度,而且解決了確保獲得好的芯片(know goodie--KGD)的問題,使功率芯片可以象普通芯片一樣進行測試老化篩選,成品率更有保證。

(2)金屬柱互連平行板結構(Metal Posts Interconnected Parallel Plate Structures--MPIPP)

圖3所示為金屬柱互連平行板結構的封裝示意圖。在硅片的正反兩面上下各有一層互相平行的陶瓷覆銅板(Direct Bond Copper--DBC)。DBC板上都預先刻蝕有相應的電路。硅片的底面直接焊接在DBC板上,而硅片正面的電極是通過直接鍵合的金屬柱引出,與上DBC板構成電氣連接,即借助金屬柱完成了硅片之間及上下DBC板之間的互連。上DBC板作為一雙面基板,安裝驅動、保護等元件構成控制電路,與下DBC板的功率電路共同組成具備獨立完整功能的集成電力電子模塊。

(3)其他互連方式

類似的以焊接技術為基礎的互連方式還包括仙童公司的球柵陣列MOSFET,摩托羅拉公司的多芯片機械電子功率封裝(Multichip Mechatronics Power Package),CPES的凹陷陣列互連(Dimple Array Interconnect-DAI)等。其中DAI技術是在銅帶上制作類似球柵陣列的凹陷陣列,將凹陷的凸起作為芯片的互連引線。與凸焊點相比,凹陷陣列的凸起高度可以做的更高,使互連更加可靠,在銅帶上制作凹陷的工藝相對也較為簡單。

2.2 沉積金屬膜為基礎的互連工藝

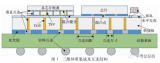

以沉積金屬膜為基礎的互連工藝多采用埋置型三維封裝結構,即在各類基板或介質中埋置裸芯片,頂層再貼裝表貼元件及芯片來實現(xiàn)三維封裝結構。典型結構如圖4所示。其特點是蒸鍍或濺射的金屬膜不僅與芯片的電極相連,而且可以構成電路圖形,并連至其他電路。

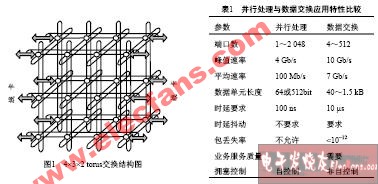

其最大優(yōu)點是能大大減少焊點,縮短引線間距,進而減小寄生參數(shù)。表1所示為幾種互連工藝的寄生參數(shù)比較。可以看出,不論寄生電感還是等效電阻,沉積金屬膜為基礎的互連工藝都是最低的。另外,這種互連工藝采用的埋置型三維封裝結構能夠增大芯片的有效散熱面積,熱量耗散可以沿模塊的各個方向流動,有利于進一步提高集成模塊的功率密度。

表1不同互連工藝下的寄生參數(shù)比較

| 電氣參數(shù) | 引線鍵合 (wire bond) | 帶自動鍵合 (TAB) | 焊料凸點 (solder bump) | 沉積金屬膜 (metallization) |

| 寄生電感(nH) | 13 | 0.52.0 | <0.1 | <0.01 |

| 等效電阻(m) | 30100 | 1350 | 26 | <1 |

以沉積金屬膜為基礎的互連工藝有:薄膜覆蓋技術和嵌入式封裝等。

(1)薄膜覆蓋技術(Thin Film Power Overlay Technology)

圖5為采用薄膜覆蓋技術構成的功率模塊的結構示意。首先在功率芯片上涂覆聚酰亞胺介質薄膜。之后利用激光在薄膜上燒灼過孔,與下面芯片的電極相通。再用濺射法使過孔金屬化,然后涂覆金屬層,并圖形化。最上層表貼驅動、控制、保護元件。薄膜覆蓋技術的優(yōu)點是能夠制作耐壓等級高、電流大、高效散熱的集成功率模塊。

(2)嵌入式封裝(Embedded Power Technology)

圖6為嵌入式封裝的結構示意圖。首先在陶瓷框架上刻蝕出空洞,功率芯片被埋設在陶瓷框架的空洞內,之后,在其上部利用絲網(wǎng)漏印、光刻等技術分別涂覆介質薄膜以及金屬膜并使之圖形化,最后,集成模塊的驅動、控制、保護元件以表貼或膜式元件的形式粘附在最上層。嵌入式封裝結構的最大優(yōu)點是可以大為縮小模塊的體積,繼而提高模塊的功率密度。和焊接技術為基礎的互連工藝相比,芯片電極引出線的距離更短,相應的寄生參數(shù)也更小。

針對電力電子集成模塊的新型集成與封裝技術的研究是電力電子集成領域的研究重點。傳統(tǒng)的平板型、螺栓型等封裝結構以及引線鍵合、壓接等互連方式由于存在各種缺陷,不適用于電力電子集成模塊。以MCM為基礎的三維封裝技術具有組裝密度高、寄生參數(shù)小、功耗低等優(yōu)點,成為集成模塊的發(fā)展方向。其中,以焊接技術為基礎的互連方法工藝相對簡單,成本相對較低;以沉積金屬膜為基礎的互連方法結構更緊湊,寄生參數(shù)更小,更利于三維散熱,但工藝較為復雜。

- 電力電子(48394)

- 研究現(xiàn)狀(5440)

相關推薦

功率電子封裝結構詳解

2295

2295BGA封裝與PCB差分互連結構的設計與優(yōu)化

1127

1127

LTCC封裝技術研究現(xiàn)狀與發(fā)展趨勢

1043

1043

大功率電力電子器件散熱研究綜述

773

773

通過Level和Step兩方面剖析現(xiàn)代電子集成技術

158

158

電力電子變壓器對交直流混合微網(wǎng)功率控制的研究

電力電子器件的歸納

電力電子裝置中模擬信號的精確隔離傳輸

電力電子設備的現(xiàn)狀與展望

電力電子集成模塊封裝構成與研究重點

電子封裝技術最新進展

集成電路封裝技術專題 通知

CAD技術在電子封裝中的應用及其發(fā)展

C語言和MATLAB程序設計在電力諧波電流檢測方法仿真中的應用是什么

PCB線路板的互連方式

SiC器件在新能源電力系統(tǒng)中的發(fā)展分析和展望

【精品】集成電路應用識圖方法電子書

【設計技巧】PCB板的互連方式

一文解讀集成電路的組成及封裝形式

中科院海西研究院泉州裝備制造研究所現(xiàn)代電機控制與電力電子實驗室招聘公告

光互連技術

光互連技術發(fā)展面臨的難點

光互連技術的研究進展

光互連技術的展望

光電子集成芯片

單片光電子集成技術

平面全屬化封裝技術

歸納碳化硅功率器件封裝的關鍵技術

報名 | 寬禁帶半導體(SiC、GaN)電力電子技術應用交流會

新人學習電力電子,求電力電子仿真模型

汽車用基礎電子元器件發(fā)展現(xiàn)狀與趨勢是什么?

現(xiàn)代電力電子器件的發(fā)展現(xiàn)狀與發(fā)展趨勢

現(xiàn)代電力電子器件的發(fā)展現(xiàn)狀與發(fā)展趨勢

納電子封裝的基本概念和發(fā)展現(xiàn)狀

芯片封裝鍵合技術各種微互連方式簡介教程

請問PCB板互連的方式有哪些?

電力電子集成模塊用冷板傳熱性能的仿真與實驗研究

19

19電力電子集成模塊用平板型熱管基板的傳熱特性

28

28混合封裝電力電子集成模塊內的傳熱研究

20

20超大規(guī)模集成電路銅互連電鍍工藝

15

15基于網(wǎng)絡的電力電子學虛擬實驗室的研究

32

32集成電路片內銅互連技術的發(fā)展

14

14混合封裝電力電子集成模塊內的傳熱研究

28

28集成電路互連延遲問題的研究及對策

21

21混合集成技術在電源中的應用

2085

2085

什么是直接互連結構(direct interconnecti

1588

1588

中國電子集團:調結構譜新篇

630

630集成電源是電源技術發(fā)展的必由之路

51

51電子封裝微互連中的電遷移

33

33電子集成塊封裝工藝及傳遞模設計

48

48集成電力電子模塊封裝的關鍵技術

41

41芯片封裝用電子結構材料的現(xiàn)狀

52

52微電子所在智能電表多芯片封裝研究上取得突破

905

905開關電源用電力電子集成模塊的研究

6

6帶光儲系統(tǒng)的模塊化電力電子變壓器在配電網(wǎng)中的仿真研究_袁威

1

1IMT公司與陜西光電子集成電路先導技術研究院建立戰(zhàn)略合作關系,合力推動光電子集成電路與MEMS工藝技術的融

1586

1586光互連的背景和數(shù)據(jù)中心的發(fā)展概述及光互連與光集成

16

16電力電子集成傳動系統(tǒng)與傳感器的集成

4

4可延展電子金屬導線通用互連結構研究

0

0淺析光子集成技術的優(yōu)勢和發(fā)展現(xiàn)狀

12262

12262PCB | 高速BGA 封裝與PCB 差分互連結構的設計與優(yōu)化

3836

3836陜西光電子集成電路先導技術研究院南區(qū)項目已正式啟動開工

2686

2686高速BGA封裝與PCB差分互連結構進行設計與優(yōu)化

2401

2401高速BGA封裝與PCB差分互連結構進行設計與優(yōu)化

2296

2296

南京城網(wǎng)10kvxlpe絕緣電力電纜現(xiàn)狀試驗研究

1

1IGBT功率模塊封裝中先進互連技術研究進展

6

6高速BGA封裝與PCB差分互連結構設計

534

534硅光電子集成電路與CMOS器件的集成有較大的市場需求

1325

1325淺談電子集成技術先進封裝的從2D,3D,4D封裝

1207

1207其它新型電力電子器件與功率集成電路

0

0電子集成全面解析:7種(5+2)集成技術

604

604芯片三維互連技術及異質集成研究進展

519

519

【半導光電】先進封裝-從2D,3D到4D封裝

787

787

面向集成電路產業(yè)的電子電鍍研究方法

231

231詳細介紹BGA封裝與PCB差分互連結構的設計與優(yōu)化

367

367

車規(guī)級功率模塊封裝的現(xiàn)狀,SiC MOSFET對器件封裝的技術需求

419

419

互連在先進封裝中的重要性

181

181

光子集成電路的特性

214

214

光電子集成芯片是什么

507

507光子集成芯片基礎知識

95

95微波光子集成芯片和硅基光子集成芯片的區(qū)別

104

104光子集成芯片是什么

68

68光子集成芯片的工作原理和應用

73

73 電子發(fā)燒友App

電子發(fā)燒友App

評論