新聞摘要:問運行PROTEL時老是被提醒系統(tǒng)錯誤WINDOWS無法從A:讀取數(shù)據(jù),非法操作&hellip。PROTEL有對打開文件的記憶功能,每次開機時它會自動找尋上次退出前所打開的那個文件,若A:有此文件,則自動予以調(diào)入,否則就出現(xiàn)上述現(xiàn)象。以原理圖編輯為例,這種記憶被保存在WINDOWS子目錄中一個名為SCH。為避免此麻煩,每次打開過軟驅(qū)中的文

問 運行PROTEL時老被提醒“系統(tǒng)錯誤WINDOWS無法從A:讀取數(shù)據(jù),非法操作……”。如此反復,直至重新啟動系統(tǒng)甚至死機,是為什么?

答 這說明您最近一次操作時曾打開過A:的文件且退出時未關閉。PROTEL有對打開文件的記憶功能,每次開機時它會自動找尋上次退出前所打開的那個文件,若A:有此文件,則自動予以調(diào)入,否則就出現(xiàn)上述現(xiàn)象。以原理圖編輯為例,這種記憶被保存在WINDOWS子目錄中一個名為SCH.INI的文件內(nèi),打開它即可得以驗證。為避免此麻煩,每次打開過軟驅(qū)中的文件后,記住關閉此文件(菜單是:File-Close)再退出PROTEL系統(tǒng)(File-Exit);也可以關閉Options-Preferences…中的“Save Defaults”。當然,后一種方法會對其它方面的使用帶來少許影響。

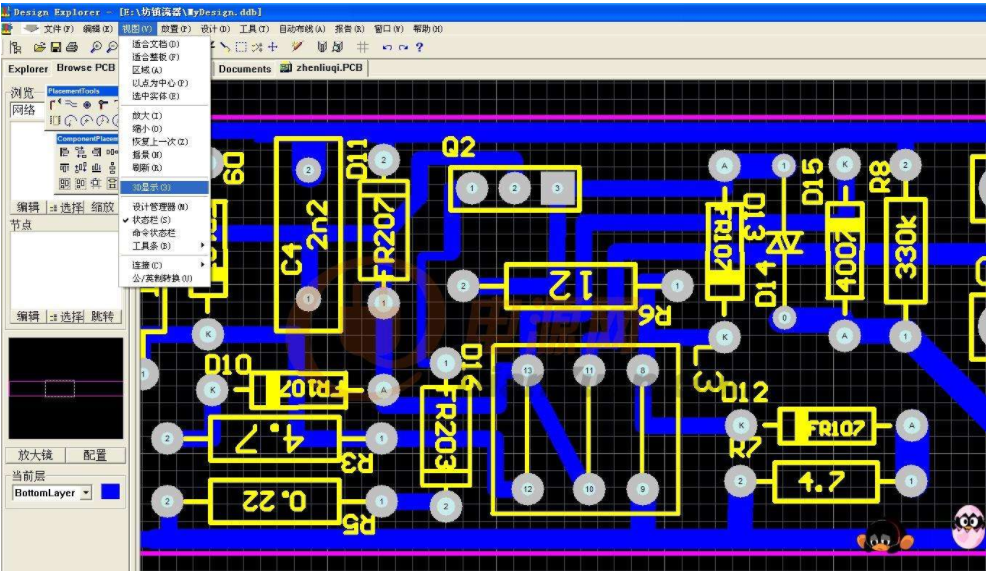

問 為什么有時會找不到繪圖和布線工具條?

答 這往往是由于調(diào)整顯示器分辨率造成的。假如您現(xiàn)在的顯示分辨率為1024×768,則兩個快捷工具條就已被您拖到了畫面的邊緣。若此時把分辨率調(diào)整為800×600,則由于這時實際所能顯示的畫面變小,原來已在邊緣的工具條勢必被“擠”到畫面以外,導致工具條“失蹤”。因此,在把分辨率由高調(diào)低之前把工具條拉到畫面中部即可解決這一問題。另外,顯示器分辨率的調(diào)整以及在WINDOWS系統(tǒng)中改變字體的大小均會造成這一現(xiàn)象,還會影響某些對話框內(nèi)字符的完整性。

問 數(shù)字系統(tǒng)的原理圖上,經(jīng)常要在集成塊引腳名或網(wǎng)絡標號的字母上方畫橫線,如WR、RESET等,PROTELFORWINDOWS能否做到?如何實現(xiàn)?

答 PROTELFORWINDOWS中有此功能。在原理圖或其元件庫的編輯中,遇到需要在網(wǎng)絡標號或引腳名等字符上方劃橫線時,只要在輸入這些名字的每個字母后面再補充輸入一個“\”號,PROTEL軟件即可自動為您把“\”號轉(zhuǎn)為前一字母的上劃線。這種方法絲毫不影響將來網(wǎng)絡表和印板設計系統(tǒng)對其原意的識別。

問 原理圖上各連線畫得清清楚楚,但在作“ERC”檢查時總被提示出錯,或建立網(wǎng)絡表后發(fā)現(xiàn)某些引腳沒連上,或是據(jù)此設計出的PCB上對應焊盤之間沒連上。總之,原理圖有連接,可印板圖自動布線時卻沒有對應走線。這是什么原因?

答 這是設計者最常遇見的也是最難自我察覺的問題,原因有以下幾種:(1)原理圖繪制時沒能嚴格區(qū)分繪圖工具條(Drawing Tools)和布線工具條(Wiring Tools)這兩者所畫出的直線的區(qū)別。前者所繪的直線是“圖畫”意義上的直線(Line);后者所繪制的直線才是具有“電特性”意義上的連接導線(Wire)。遺憾的是,軟件所給的兩者的缺省顏色太接近,以至于設計時很容易混淆。如果僅僅是繪制原理圖,即使混淆兩者也無妨,但要用這種原理圖來提取網(wǎng)絡表,則混入“Line”的對應兩點間必定連接不上。PROTEL給出前者的目的是供用戶在圖面上繪制一些與布線無關的圖案等,換言之,如果與布線無關的線條用了“Wire”繪制,同樣也會在布線時被提示出錯。解決的方法很簡單,就是在放置這兩種線中的任一種時把缺省色改為其它色。

(2)繪制“Wire”時,線畫了,以至于越過元件引腳端點與引腳線重疊。避免這種現(xiàn)象可在為每個元件連線時點選該元件,使之顯示出外廓虛線。PROTEL的“ERC”功能可以查出此類毛病(菜單是:File-Reports-Electrical Rules Check……)。

(3)柵格(Grids)選項設置不當,其中柵格捕捉精度(Snap)取得太高,可視柵格(Visible)取得較大,導致繪制“Wire”時稍不留神就在導線端點與引腳端點之間留下難以察覺的間隙,PCB設計時必然缺線。例如,當Snap取為1,Visible取為10時,就很容易產(chǎn)生這種問題。這種設置可在菜單Options-Sheet…所打開的Grids對話框中查找。另外,自己編輯庫元件的過程中,在放置元件引腳時如果把柵格捕捉精度取得太高(具體在菜單“Options-Workspace…”調(diào)出的對話框中)同樣也會使得該元件在使用中出現(xiàn)此類問題,所以,進行庫編輯時最好取與原理圖編輯相同的柵格精度。

(4)在編輯原理圖庫中的元件時沒有注意引腳的首尾之分(首端是指應當靠近元件圖案的一端;尾端指遠離元件供導線連接的那一端),導致凡使用了這種元件的地方在原理圖上看似被導線連上了,實質(zhì)上卻是連在了引腳的首端,實際布線時當然無法連接上。這種問題可這樣考慮:由于每個引腳的引腳名(例如VCC)必定是引腳的首端,故把帶引腳名的端子落在元件圖案內(nèi)即可。為此,在編輯元件庫時應把各引腳(Pin)的“Show Name”項打開,顯示出各管腳名,以此作為標識。

問 運行PROTEL時老被提醒“系統(tǒng)錯誤WINDOWS無法從A:讀取數(shù)據(jù),非法操作……”。如此反復,直至重新啟動系統(tǒng)甚至死機,是為什么?

答 這說明您最近一次操作時曾打開過A:的文件且退出時未關閉。PROTEL有對打開文件的記憶功能,每次開機時它會自動找尋上次退出前所打開的那個文件,若A:有此文件,則自動予以調(diào)入,否則就出現(xiàn)上述現(xiàn)象。以原理圖編輯為例,這種記憶被保存在WINDOWS子目錄中一個名為SCH.INI的文件內(nèi),打開它即可得以驗證。為避免此麻煩,每次打開過軟驅(qū)中的文件后,記住關閉此文件(菜單是:File-Close)再退出PROTEL系統(tǒng)(File-Exit);也可以關閉Options-Preferences…中的“Save Defaults”。當然,后一種方法會對其它方面的使用帶來少許影響。

問 為什么有時會找不到繪圖和布線工具條?

答 這往往是由于調(diào)整顯示器分辨率造成的。假如您現(xiàn)在的顯示分辨率為1024×768,則兩個快捷工具條就已被您拖到了畫面的邊緣。若此時把分辨率調(diào)整為800×600,則由于這時實際所能顯示的畫面變小,原來已在邊緣的工具條勢必被“擠”到畫面以外,導致工具條“失蹤”。因此,在把分辨率由高調(diào)低之前把工具條拉到畫面中部即可解決這一問題。另外,顯示器分辨率的調(diào)整以及在WINDOWS系統(tǒng)中改變字體的大小均會造成這一現(xiàn)象,還會影響某些對話框內(nèi)字符的完整性。

問 數(shù)字系統(tǒng)的原理圖上,經(jīng)常要在集成塊引腳名或網(wǎng)絡標號的字母上方畫橫線,如WR、RESET等,PROTELFORWINDOWS能否做到?如何實現(xiàn)?

答 PROTELFORWINDOWS中有此功能。在原理圖或其元件庫的編輯中,遇到需要在網(wǎng)絡標號或引腳名等字符上方劃橫線時,只要在輸入這些名字的每個字母后面再補充輸入一個“\”號,PROTEL軟件即可自動為您把“\”號轉(zhuǎn)為前一字母的上劃線。這種方法絲毫不影響將來網(wǎng)絡表和印板設計系統(tǒng)對其原意的識別。

問 原理圖上各連線畫得清清楚楚,但在作“ERC”檢查時總被提示出錯,或建立網(wǎng)絡表后發(fā)現(xiàn)某些引腳沒連上,或是據(jù)此設計出的PCB上對應焊盤之間沒連上。總之,原理圖有連接,可印板圖自動布線時卻沒有對應走線。這是什么原因?

答 這是設計者最常遇見的也是最難自我察覺的問題,原因有以下幾種:(1)原理圖繪制時沒能嚴格區(qū)分繪圖工具條(Drawing Tools)和布線工具條(Wiring Tools)這兩者所畫出的直線的區(qū)別。前者所繪的直線是“圖畫”意義上的直線(Line);后者所繪制的直線才是具有“電特性”意義上的連接導線(Wire)。遺憾的是,軟件所給的兩者的缺省顏色太接近,以至于設計時很容易混淆。如果僅僅是繪制原理圖,即使混淆兩者也無妨,但要用這種原理圖來提取網(wǎng)絡表,則混入“Line”的對應兩點間必定連接不上。PROTEL給出前者的目的是供用戶在圖面上繪制一些與布線無關的圖案等,換言之,如果與布線無關的線條用了“Wire”繪制,同樣也會在布線時被提示出錯。解決的方法很簡單,就是在放置這兩種線中的任一種時把缺省色改為其它色。

(2)繪制“Wire”時,線畫了,以至于越過元件引腳端點與引腳線重疊。避免這種現(xiàn)象可在為每個元件連線時點選該元件,使之顯示出外廓虛線。PROTEL的“ERC”功能可以查出此類毛病(菜單是:File-Reports-Electrical Rules Check……)。

(3)柵格(Grids)選項設置不當,其中柵格捕捉精度(Snap)取得太高,可視柵格(Visible)取得較大,導致繪制“Wire”時稍不留神就在導線端點與引腳端點之間留下難以察覺的間隙,PCB設計時必然缺線。例如,當Snap取為1,Visible取為10時,就很容易產(chǎn)生這種問題。這種設置可在菜單Options-Sheet…所打開的Grids對話框中查找。另外,自己編輯庫元件的過程中,在放置元件引腳時如果把柵格捕捉精度取得太高(具體在菜單“Options-Workspace…”調(diào)出的對話框中)同樣也會使得該元件在使用中出現(xiàn)此類問題,所以,進行庫編輯時最好取與原理圖編輯相同的柵格精度。

(4)在編輯原理圖庫中的元件時沒有注意引腳的首尾之分(首端是指應當靠近元件圖案的一端;尾端指遠離元件供導線連接的那一端),導致凡使用了這種元件的地方在原理圖上看似被導線連上了,實質(zhì)上卻是連在了引腳的首端,實際布線時當然無法連接上。這種問題可這樣考慮:由于每個引腳的引腳名(例如VCC)必定是引腳的首端,故把帶引腳名的端子落在元件圖案內(nèi)即可。為此,在編輯元件庫時應把各引腳(Pin)的“Show Name”項打開,顯示出各管腳名,以此作為標識。

電子發(fā)燒友App

電子發(fā)燒友App

評論