前言

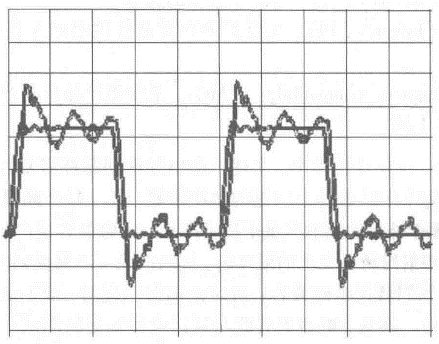

100 MHz 時(shí)鐘產(chǎn)生后,從信號(hào)驅(qū)動(dòng)器芯片輸出的兩種波形:沒有外加引出連線(平滑曲線)的情況和輸出端連接一段2 in長的PCB線條(振鈴曲線)的情況。

縱軸每格表示1 V,橫軸每格表示2 ns

對(duì)于大多數(shù)電子產(chǎn)品而言,當(dāng)時(shí)鐘頻率超過100 MHz或者上升邊小于1 ns時(shí),信號(hào)完整性效應(yīng)就變得重要了,通常將這種情況稱為高頻領(lǐng)域或高速領(lǐng)域(區(qū)別與高速信號(hào)的定義)。

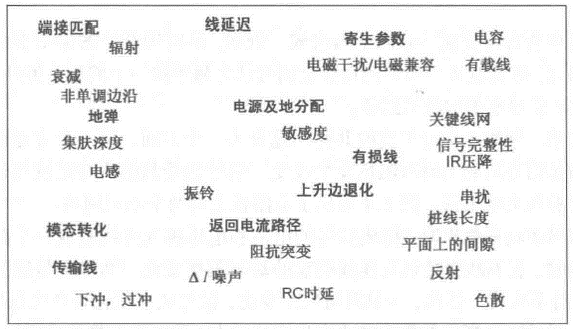

從廣義上講,信號(hào)完整性指的是在高速產(chǎn)品中互連線引起的所有問題。主要研究當(dāng)互連線與數(shù)字信號(hào)的電壓電流波形相互作用時(shí),其電氣特性如何影響產(chǎn)品的性能。?

可以將所有這些問題歸結(jié)為以下三類。在這三類問題之間也存在著相當(dāng)大的重疊:

1.信號(hào)完整性(Signal Integrity,SI),主要指信號(hào)波形的失真;

2.電源完整性(Power Integrity,PI),主要指為有源器件供電的互連線及各相關(guān)元器件的噪聲;

3.電磁兼容(Electro Magnetic Compatibility,EMC),主要指產(chǎn)品自身產(chǎn)生的電磁輻射和由外場導(dǎo)入產(chǎn)品的電磁干擾。

在信號(hào)完整性領(lǐng)域中,通常信號(hào)完整性問題與噪聲問題或者時(shí)序問題有關(guān)。這兩類問題都可能引起接收端的誤觸發(fā)或者誤碼。?例如,分配一些時(shí)間給門翻轉(zhuǎn)、將信號(hào)傳送至輸出門、等待時(shí)鐘進(jìn)入下一級(jí)門、等待門讀出輸入端的數(shù)據(jù)等。互連線嚴(yán)重影響時(shí)序預(yù)算,這里主要討論由互連線產(chǎn)生的上升邊失真對(duì)抖動(dòng)的影響。

許多信號(hào)完整性噪聲問題,如振鈴、發(fā)射、近端串?dāng)_、開關(guān)噪聲、非單調(diào)性、地彈、電源彈、衰減和容性負(fù)載等。這些都是互連線的電氣特性對(duì)數(shù)字信號(hào)波形造成的不同影響。?

以上列出的問題都和如下的6種類型的問題之一有關(guān):

1.單一網(wǎng)絡(luò)的信號(hào)失真;

2.互連線中頻率相關(guān)損耗引起的上升邊退化;

3.兩個(gè)或多個(gè)網(wǎng)絡(luò)之間的串?dāng)_;

4.作為串?dāng)_特殊形式的地彈和電源彈;

5.電源和地分配中的軌道坍陷;

6.來自整個(gè)系統(tǒng)的電磁干擾和輻射。

二、單一網(wǎng)絡(luò)的信號(hào)完整性

互連線引起單一網(wǎng)絡(luò)上信號(hào)失真的共性問題分為三個(gè)方面:?

第一個(gè)方面是反射 ;

第二個(gè)方面是信號(hào)質(zhì)量問題;?

第三個(gè)方面是時(shí)序;

反射:

引起反射的唯一原因是信號(hào)遇到的瞬時(shí)阻抗發(fā)生改變。?

任何改變橫截面或者網(wǎng)絡(luò)幾何結(jié)構(gòu)的特征都會(huì)改變信號(hào)所感受到的阻抗。引起阻抗變化的所有特征稱為突變。?

所感受到的阻抗發(fā)生改變的情況來自以下幾點(diǎn):

1.互連線末端;2.線寬變化;

3.層轉(zhuǎn)換;4.返回路徑平面上的間隙;

5.接插件;

6.路由拓?fù)涞母淖儯热绶种Ь€、T行線或樁線。

信號(hào)質(zhì)量問題:

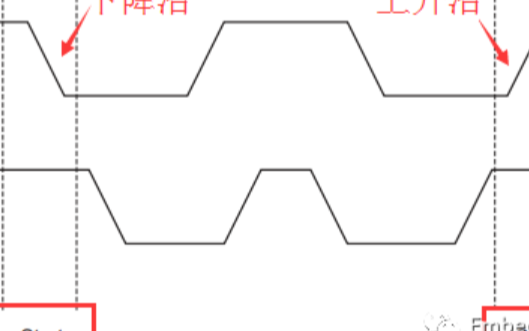

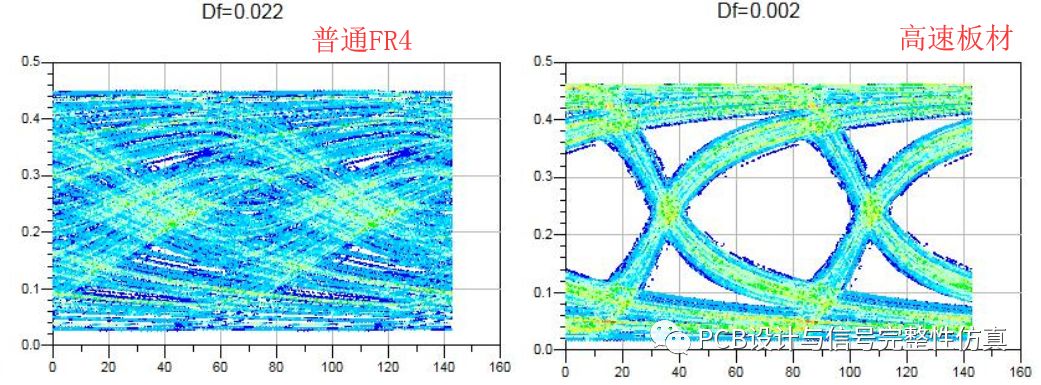

導(dǎo)線和介質(zhì)中與頻率相關(guān)的損耗,所造成信號(hào)的高頻損耗要比低頻損耗更大,其結(jié)果是在傳播中信號(hào)上升邊將會(huì)被拉長。?

這個(gè)上升邊退化到接近信號(hào)的單位間隔(Unit ?interval,UI)時(shí),1比特的信息將會(huì)泄漏到下一個(gè)甚至下下個(gè)比特,這種效應(yīng)稱為符號(hào)間干擾(Inter-Symbol Interference,ISI)。在數(shù)據(jù)率或更高的高速串行鏈路中,它將是引起問題的主要原因。

時(shí)序:

兩個(gè)或者多個(gè)信號(hào)路徑之間的時(shí)延差稱為錯(cuò)位(skew)。錯(cuò)位是兩條或者多條網(wǎng)絡(luò)之間時(shí)延的差異。為了控制錯(cuò)位,主要依靠匹配網(wǎng)絡(luò)之間的長度。另外,網(wǎng)絡(luò)之間的介電常數(shù)發(fā)生局部變化(如疊層中的玻璃纖維分布)也會(huì)影響時(shí)延,這個(gè)問題比較難以控制。?

當(dāng)信號(hào)線和時(shí)鐘線之間存在超出預(yù)期的錯(cuò)位時(shí),就可能產(chǎn)生誤觸發(fā)和邏輯錯(cuò)誤。?

當(dāng)差分對(duì)的兩條線之間存在錯(cuò)位時(shí),部分差分信號(hào)會(huì)轉(zhuǎn)變?yōu)楣材P盘?hào),并造成差分信號(hào)失真。

三、串?dāng)_

網(wǎng)絡(luò)之間的容性耦合和感性耦合,為有害噪聲從一個(gè)網(wǎng)絡(luò)到達(dá)另外一個(gè)網(wǎng)絡(luò)提供了路徑。

同時(shí),也可以將其描述為從攻擊網(wǎng)絡(luò)到受害網(wǎng)絡(luò)邊緣電磁場的作用。?

兩種不同情況下會(huì)發(fā)生串?dāng)_:

1.互連線為均勻傳輸線,電路板上大多數(shù)線條屬于這種情況;

2.互連線為非均勻傳輸線,如接插件和封裝的場合。

這兩種效應(yīng)在靜態(tài)線的近端和遠(yuǎn)端的疊加方式是不一樣的。

當(dāng)信號(hào)經(jīng)過接插件且多個(gè)信號(hào)共用的返回路徑是一個(gè)引腳而不是一個(gè)平面時(shí),感性耦合噪聲比容性耦合噪聲增加得更多。當(dāng)感性耦合噪聲處于主導(dǎo)地位時(shí),通常把這種串?dāng)_歸為同時(shí)開關(guān)噪聲(Simultaneous Switching Noise,SSN)。這類噪聲是由耦合電感(即所謂的互感)產(chǎn)生的。?

開關(guān)噪聲大多發(fā)生在接插件、封裝和過孔處。地彈實(shí)際上是同一個(gè)導(dǎo)體上返回電流重疊而出現(xiàn)的一種特殊情況。

四、軌道塌陷噪聲

當(dāng)通過電源路徑和地路徑的電流發(fā)生變化時(shí),如芯片翻轉(zhuǎn)或者內(nèi)核中的門翻轉(zhuǎn)時(shí),在電源路徑和地路徑之間的阻抗上產(chǎn)生一個(gè)壓降,這個(gè)壓降意味著供給芯片的電壓減小了,稱為電源與地之間的電壓降低或者坍陷。

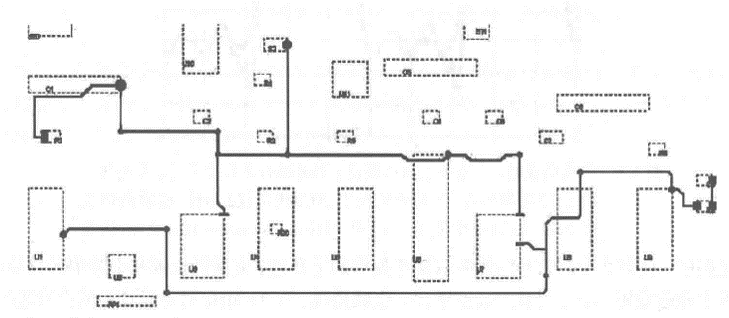

微處理器電源軌道上的電壓變化

五、電磁干擾

電磁干擾問題包括3個(gè)方面:噪聲源、輻射傳播路徑和天線。?

兩種常見的電磁干擾源:

1.一部分差分信號(hào)轉(zhuǎn)換成共模信號(hào),最終在外部的雙絞電纜線上輸出;2.電路板上的地彈在外部單端屏蔽線上產(chǎn)生共模電流。附加的噪聲可以由內(nèi)部產(chǎn)生的輻射泄漏溢出屏蔽罩而引起。

鐵氧體扼流圈的剖視圖。

鐵氧體通常用在電纜周圍,

以減小類似共模電流這種主要的輻射源。

六、信號(hào)完整性的兩個(gè)重要推論

第一個(gè)重要推論:所有信號(hào)完整性問題都是以電流或者電壓的變化速度來衡量的,通常指的是dI/dt或者dV/dt,上升邊越短意味著dI/dt或者dV/dt越大。隨著上升邊縮短,噪聲問題必然增加,并且更難以解決。?

第二個(gè)重要推論:解決信號(hào)完整性的有效辦法在很大程度上基于對(duì)互連線阻抗的理解。把互連線的物理設(shè)計(jì)與互連線阻抗聯(lián)系起來,在設(shè)計(jì)過程中就能消除許多信號(hào)完整性問題。

七、電子產(chǎn)品的趨勢(shì)

時(shí)鐘頻率越來越高的趨勢(shì)都是由同一種技術(shù)——光刻法所引起的。由于能夠生產(chǎn)更小尺寸的晶體管門溝道長度,晶體管的開關(guān)速度提高了。?

溝道長度越短,電子與空穴移動(dòng)距離就越短,且能在更短時(shí)間內(nèi)通過門并引起狀態(tài)轉(zhuǎn)變。當(dāng)提到0.18 μm 或 0.13 μm 的技術(shù)階段時(shí),實(shí)際上是指能夠制造的最小溝道長度。

一個(gè)時(shí)鐘周期所需的最小時(shí)間受該周期內(nèi)需要執(zhí)行的所有操作的限制。通常制約最小時(shí)間的因素有3個(gè):

1.所有開關(guān)門必要的固有開關(guān)時(shí)間;

2.信號(hào)經(jīng)系統(tǒng)互連線傳播到所有開關(guān)門的時(shí)間;

3.所有門讀取輸入信號(hào)所需的建立和保持時(shí)間。

八、仿真

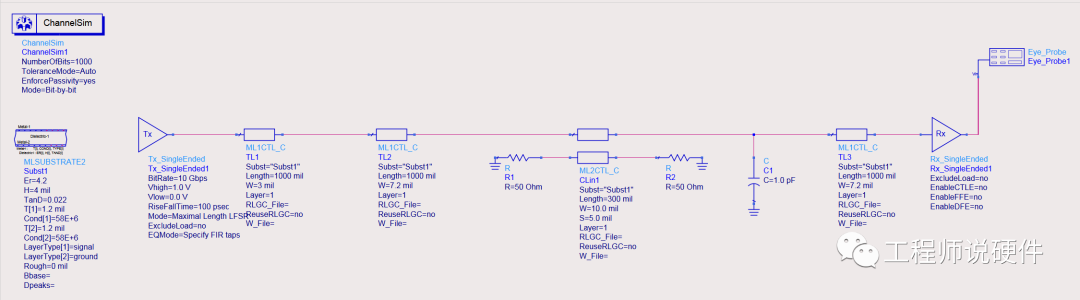

三種電氣仿真工具可用來預(yù)估互連線對(duì)信號(hào)行為造成的模擬效應(yīng)。?

電磁仿真或3D全波-場求解器。在時(shí)域或頻率中,使用所設(shè)計(jì)的幾何邊界條件和材料屬性對(duì)麥克斯韋方程組進(jìn)行求解,并仿真出各個(gè)位置電場和磁場;?

電路仿真器。在時(shí)域或頻域中,對(duì)各種電路元件對(duì)應(yīng)的微分方程進(jìn)行求解,并運(yùn)用基爾霍夫電流、電壓關(guān)系來預(yù)估各個(gè)電路節(jié)點(diǎn)處的電壓和電流。這些通常都是與SPICE兼容的仿真器;?

數(shù)值仿真工具。先綜合輸入波形,再依據(jù)互連線的S參數(shù)模求解其沖擊響應(yīng),然后采用卷積積分或其他數(shù)值方法計(jì)算每個(gè)端口的輸出波形。

1.電磁仿真:

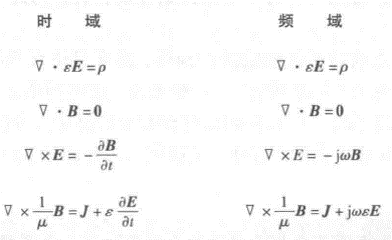

關(guān)于電磁仿真,應(yīng)該把信號(hào)完整性問題歸結(jié)為麥克斯韋方程組。這4個(gè)方程描述了導(dǎo)體和電介質(zhì)與電場和磁場之間的相互作用。歸根到底,信號(hào)只是在傳播電場和磁場。當(dāng)仿真電場和磁場本身時(shí),互連線和所有無源元件必須轉(zhuǎn)換為與其幾何結(jié)構(gòu)和材料特性相關(guān)的導(dǎo)體和介質(zhì)。

在時(shí)域和頻域中的麥克斯韋方程組描述了

在時(shí)間和空間上電磁場如何與材料相互作用

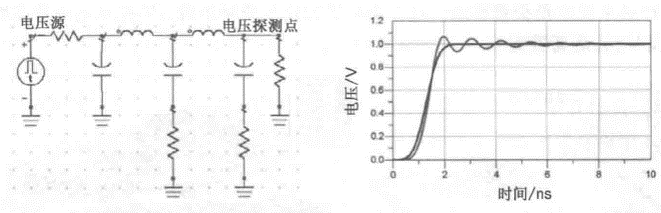

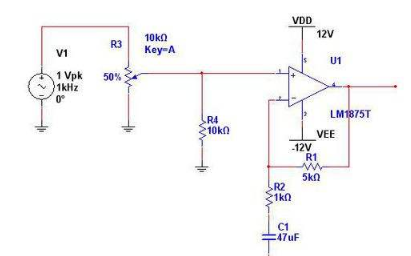

2.電路仿真:

用電壓和電流表示信號(hào),將各種導(dǎo)體和電介質(zhì)轉(zhuǎn)換成電阻、電容、電感和傳輸線等基本電路元件及其之間的耦合關(guān)系。這種將物理結(jié)構(gòu)轉(zhuǎn)換為電路元件的過程稱為建模。?

電路仿真器未能考慮電磁效應(yīng),如電磁兼容問題、諧振和非均勻波傳播等。

最常用的電路仿真器為SPICE(Simulation Program with Integrated Circuit Emphasis),是一種基于晶體管的幾何結(jié)構(gòu)和材料特性來預(yù)估晶體管性能的工具。

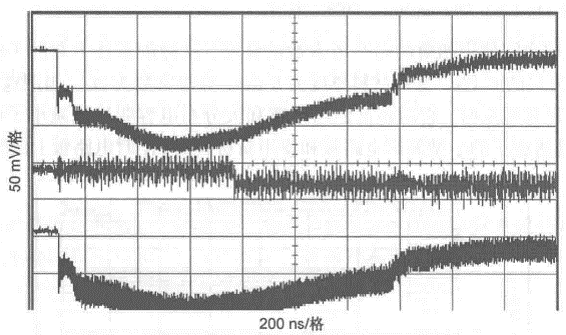

左圖為長約5 cm的典型示波器探針的電路模型;

右圖為無雜波的上升邊為1 ns的信號(hào)的仿真波形結(jié)果。

其中,振蕩是由探針的附加電感引起的。

3.數(shù)值仿真工具:

MATLAB,Python,Keysight PLTS,以及Teledyne Lecroy SI Studio等數(shù)學(xué)仿真器是仿真工具的示例,可以根據(jù)輸入波形的綜合來預(yù)估輸出波形,分析它們?nèi)绾闻cS參數(shù)互連線模型進(jìn)行交互。?

與電路仿真器相比,它們的主要優(yōu)點(diǎn)在于運(yùn)算速度。許多這類仿真器使用專門的仿真引擎,并且對(duì)特殊類型的波形,例如正弦波、時(shí)鐘或非歸零數(shù)據(jù)模式等進(jìn)行了優(yōu)化。

九、模型與建模

建模是指為待仿真的元器件創(chuàng)建一種電氣表征與描述模型。有源器件(如晶體管和輸出驅(qū)動(dòng)器)的模型與無源元件(如所有互連線和分立元件)的模型是完全不同的。?

有源器件的SPICE模型要用到理想源和無源元件的組合,或基于晶體管幾何結(jié)構(gòu)的專用晶體管模型,所以工藝技術(shù)改變時(shí)也能很容易地按比例改變晶體管的行為。

IBIS 是定義輸入或輸出驅(qū)動(dòng)器的V-I和V-t 特性響應(yīng)的一種格式。行為仿真器提取有源器件的V-I和V-t 曲線,并仿真出這些曲線受傳輸線和表示互連線的集總元件電阻器(R)、電感器(L)、電容器(C)影響時(shí)的變化程度。

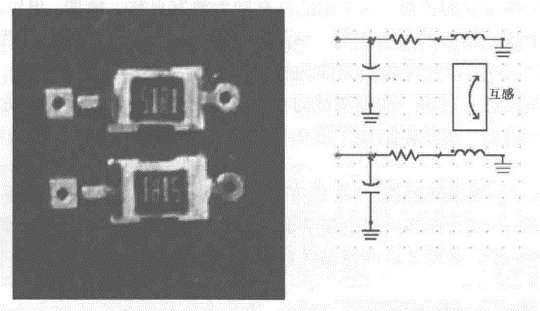

創(chuàng)建互連線的精確電路模型有兩種基本方法:計(jì)算和測(cè)量。?

通過計(jì)算來創(chuàng)建模型稱為分析,通過測(cè)量來創(chuàng)建模型稱為表征。

兩個(gè)貼片式0805電阻器及其等效電路模型

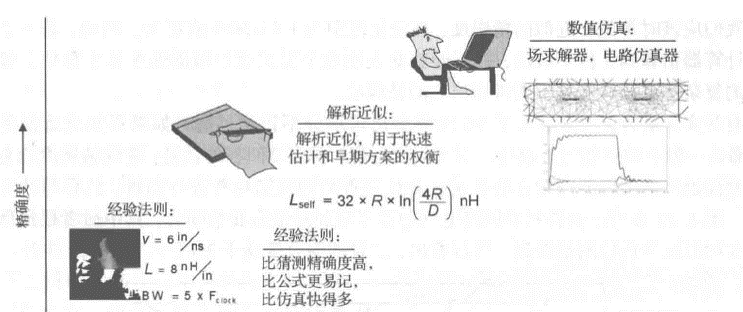

將預(yù)估性能或電氣特性的近似方案分成如下3級(jí):

?經(jīng)驗(yàn)法則?

?解析近似?

?數(shù)值仿真

十、三種測(cè)量技術(shù)

1.阻抗分析儀

阻抗分析儀在頻域中工作,一般有4個(gè)接頭,其中第一對(duì)接頭產(chǎn)生流過被測(cè)元器件(Device Under Test,DUT)正弦波恒定電流,第二對(duì)接頭測(cè)量被測(cè)元器件上的正弦電壓。

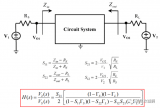

2.矢量網(wǎng)絡(luò)分析儀(Vector-Network Analyzer,VNA)

矢量網(wǎng)絡(luò)分析儀也在頻域中工作。每個(gè)接頭或端口發(fā)出一個(gè)正弦電壓,其頻率范圍從幾kHz到50 GHz,在每個(gè)頻率點(diǎn),測(cè)量入射電壓幅度與相位及反射電壓的幅度和相位。

3.時(shí)域反射計(jì)(Time-Domain Reflectometer,TDR)

時(shí)域反射計(jì)與矢量網(wǎng)絡(luò)分析儀相似,但工作在時(shí)域中。它發(fā)射邊沿快速上升的階躍信號(hào),上升邊一般為35~150 ps,然后測(cè)量反射的瞬時(shí)幅度。另外,利用反射電壓提取被測(cè)元器件的阻抗。

總結(jié)

整個(gè)信號(hào)完整性理論方面的基礎(chǔ)知識(shí)都在這里有了羅列。前面的基礎(chǔ)概念知識(shí),建議深入理解,后面的建模和仿真,特別是數(shù)值仿真工具,可能是一個(gè)趨勢(shì)。

編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論