主要介紹了ADC學(xué)習(xí)——采樣電路相關(guān)的知識(shí),希望對(duì)你有一定的參考價(jià)值。

一. 基本跟蹤保持電路及其非理想性

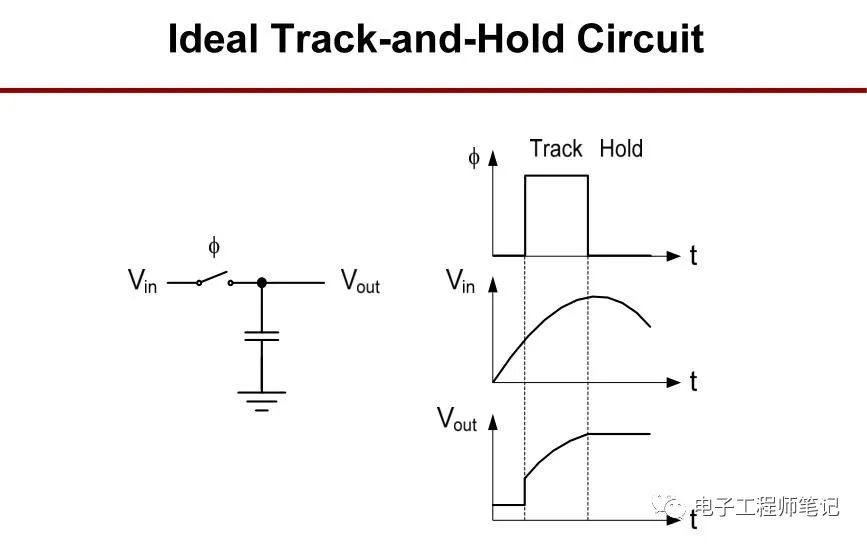

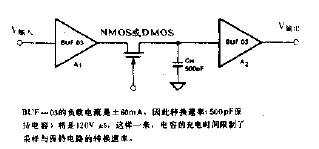

理想的跟蹤保持電路。

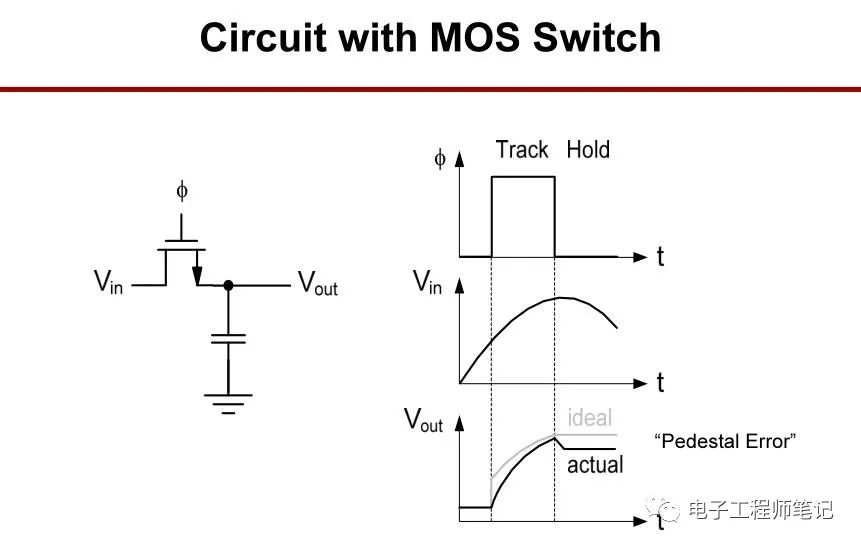

實(shí)際的MOS開(kāi)關(guān)采樣電路會(huì)有一系列的非理想性。

1.1 有限采集時(shí)間

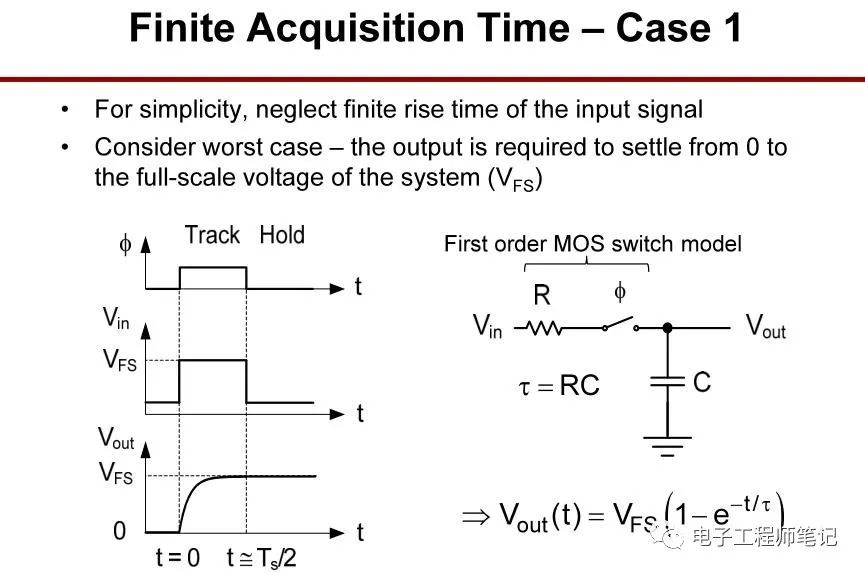

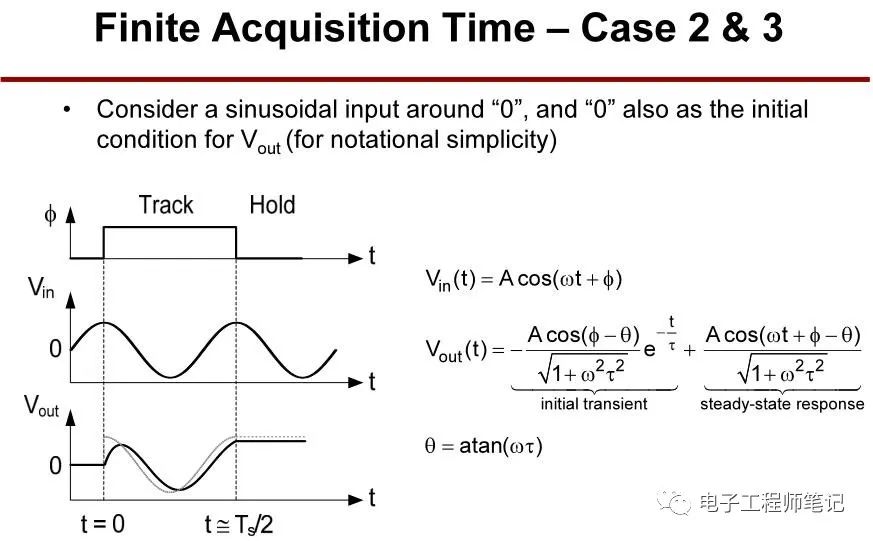

考慮輸入為case1采樣的數(shù)據(jù),case2慢速連續(xù)數(shù)據(jù)和case3快速連續(xù)數(shù)據(jù)三種情況。

case1中的輸出信號(hào)時(shí)域公式。

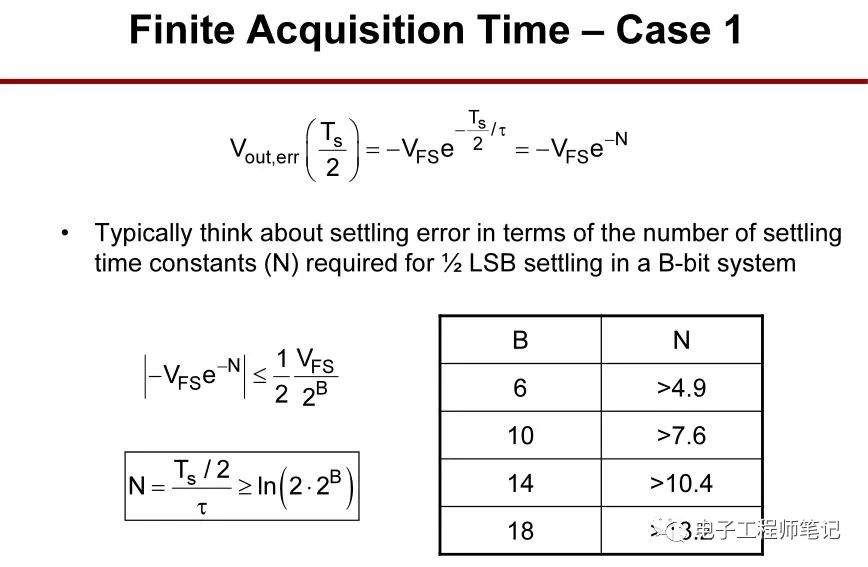

case1中的輸出信號(hào)建立誤差可以推導(dǎo)出位數(shù)(B)與建立時(shí)間常數(shù)(N)關(guān)系。

?

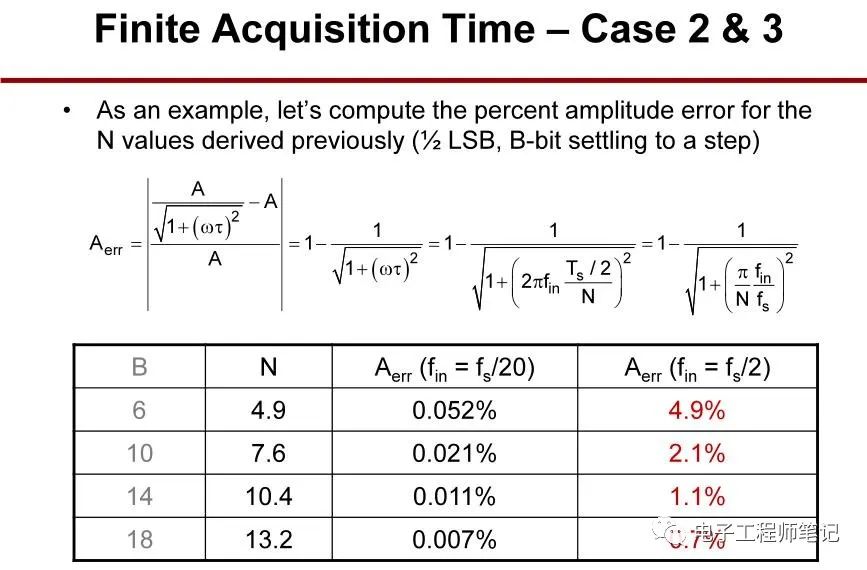

case2&case3時(shí),位數(shù)(B)與振幅誤差百分比(?A e r r A_err?Aerr)的關(guān)系。

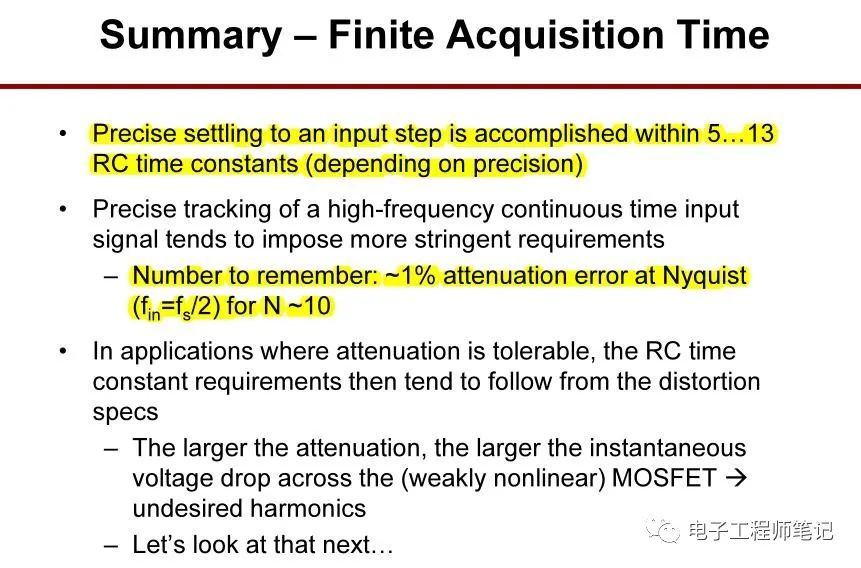

輸入階躍的精確建立在5~13 RC時(shí)間常數(shù)內(nèi)完成。對(duì)于N ~10,奈奎斯特頻率下約1%的衰減誤差(?f i n = f s / 2 f_in =f_s/2?fin=fs/2)。

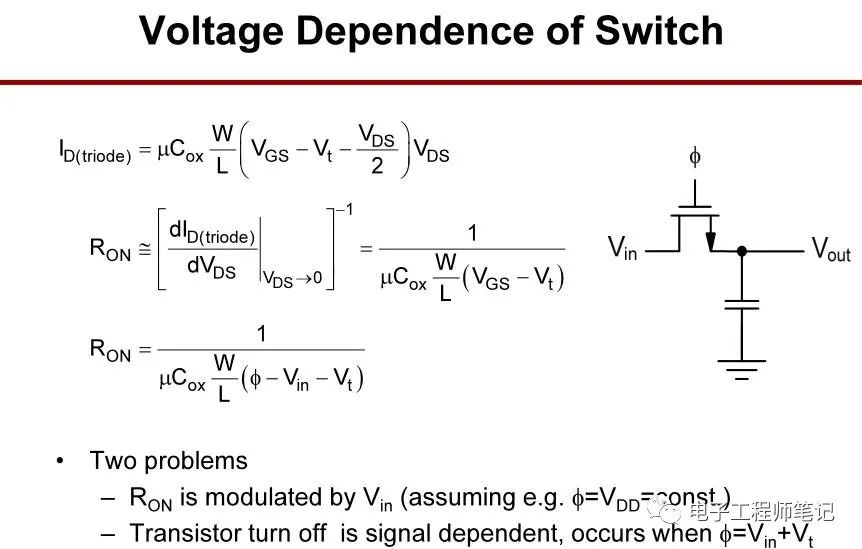

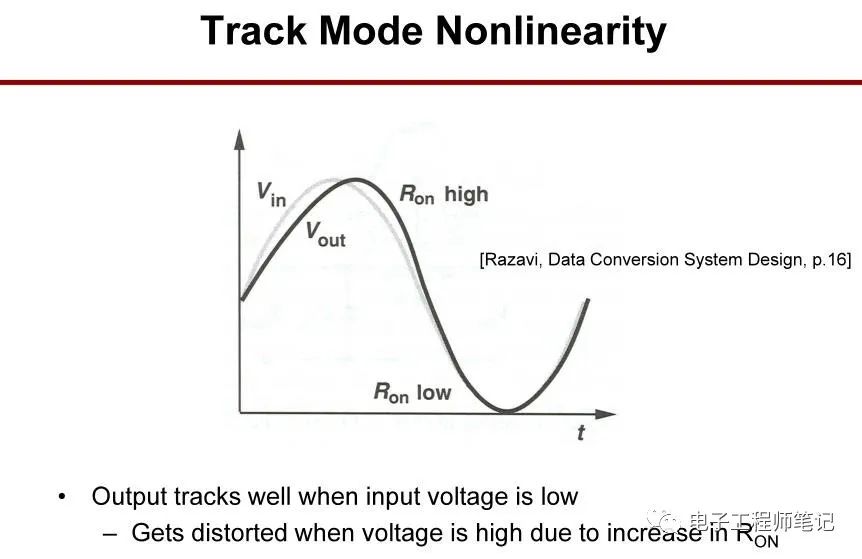

1.2 跟蹤非線性

直接使用MOS管作為開(kāi)關(guān)進(jìn)行采樣保持會(huì)帶來(lái)一些問(wèn)題,如開(kāi)關(guān)電阻會(huì)受到輸入信號(hào)的調(diào)制,大的輸入信號(hào)會(huì)帶來(lái)大的開(kāi)關(guān)電阻。

跟蹤非線性在輸入信號(hào)較小時(shí)不明顯,但隨著輸入信號(hào)增大,開(kāi)關(guān)電阻增大,跟蹤信號(hào)會(huì)產(chǎn)生失真。

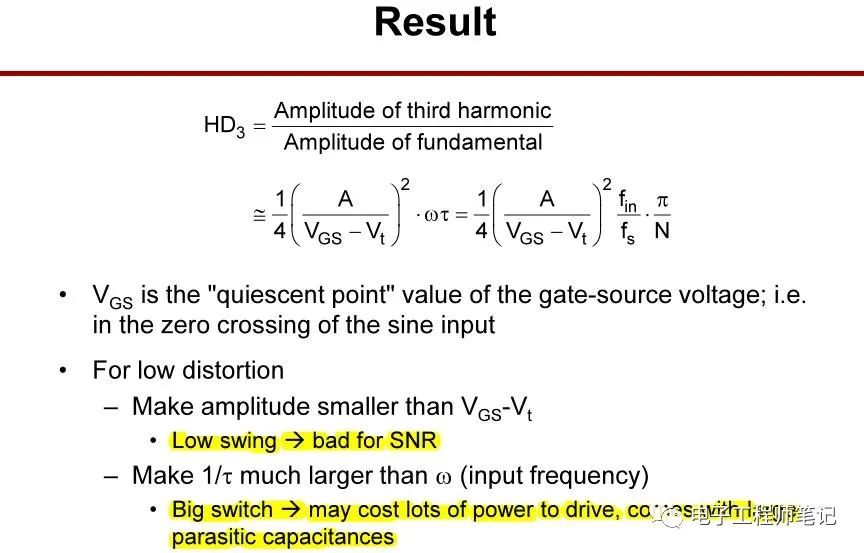

非線性帶來(lái)的諧波失真,可以由上面的公式來(lái)近似估計(jì)。可以看到,低諧波失真可以通過(guò)使輸入信號(hào)幅度A小于?V G S ? V t V_GS-V_t?VGS?Vt來(lái)實(shí)現(xiàn),但帶來(lái)SNR惡化。

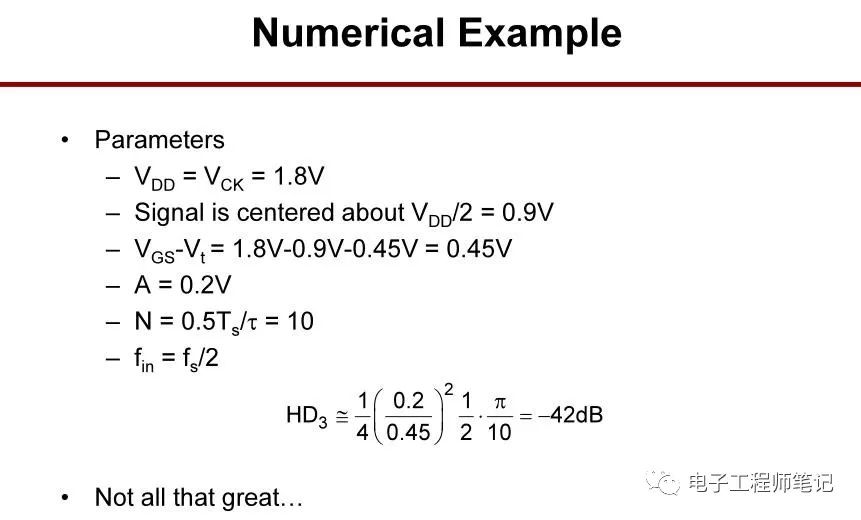

下面是跟蹤非線性帶來(lái)的諧波失真計(jì)算。

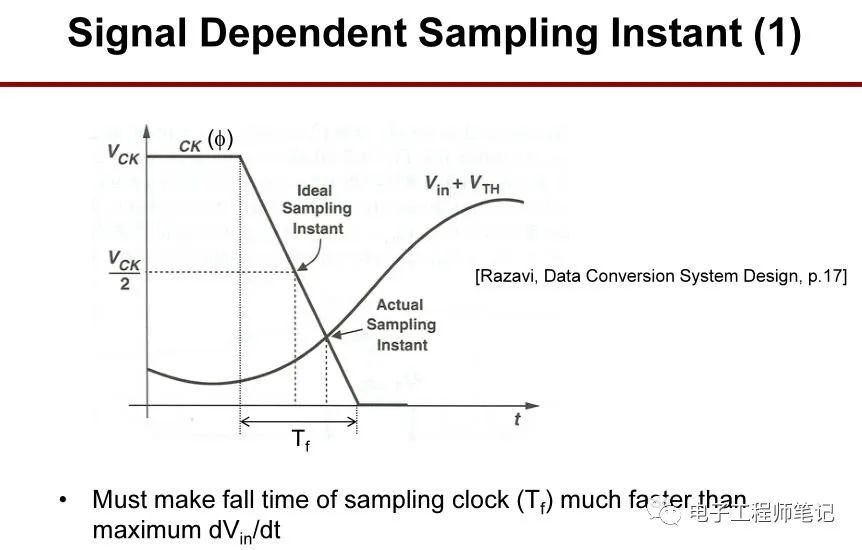

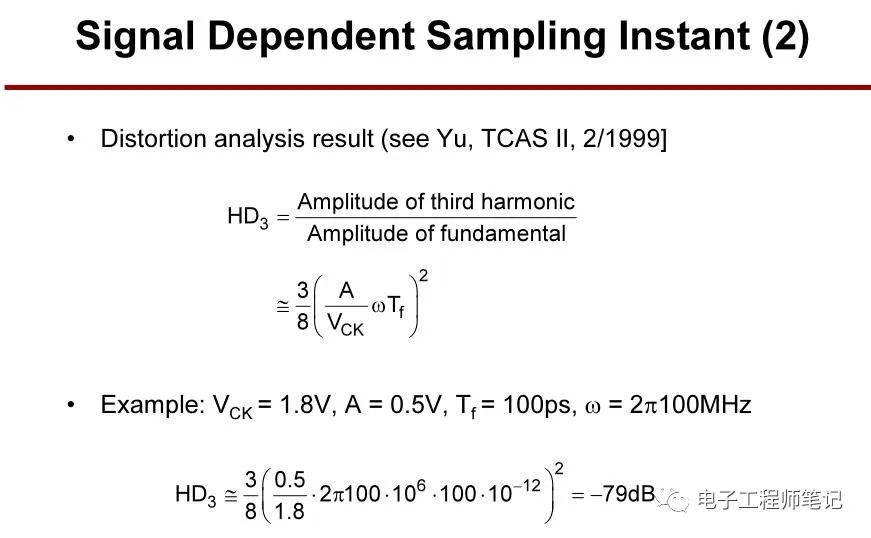

1.3 信號(hào)相關(guān)保持瞬間

必須使采樣時(shí)鐘的下降時(shí)間(?T f T_f?Tf)比最大的?d V i n / d t dV_in/dt?dVin/dt快得多,否則也會(huì)帶來(lái)諧波失真。

三次諧波失真的計(jì)算公式及示例。

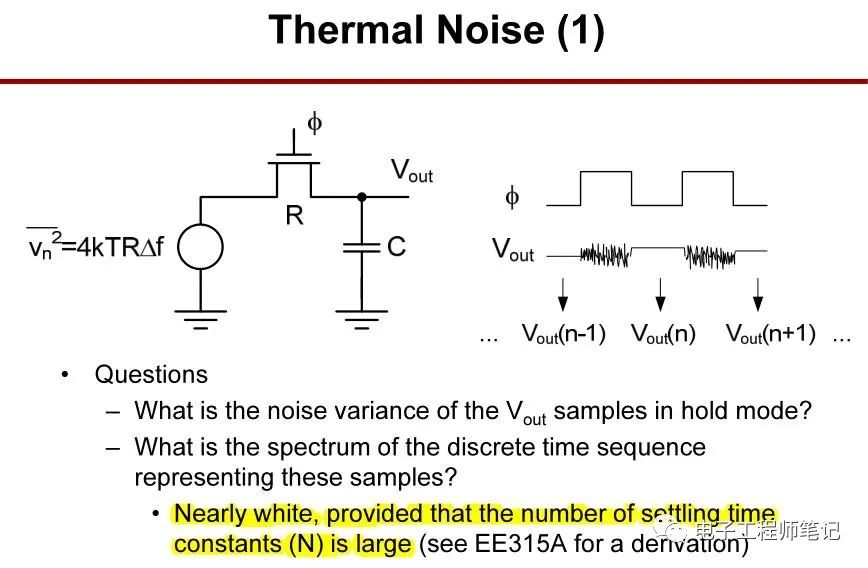

1.4 熱噪聲

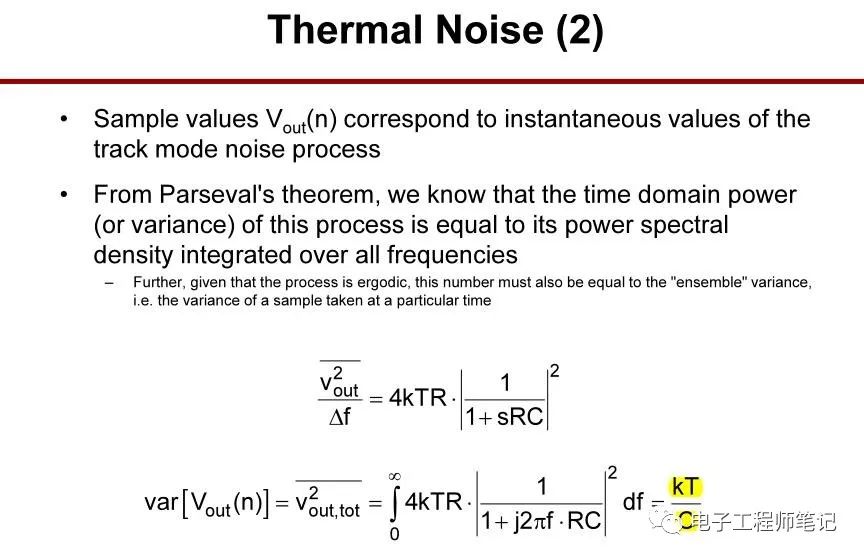

熱噪聲開(kāi)關(guān)采樣后的頻譜近似為白噪聲。

熱噪聲的噪聲功率為?k T / C kT/C?kT/C。

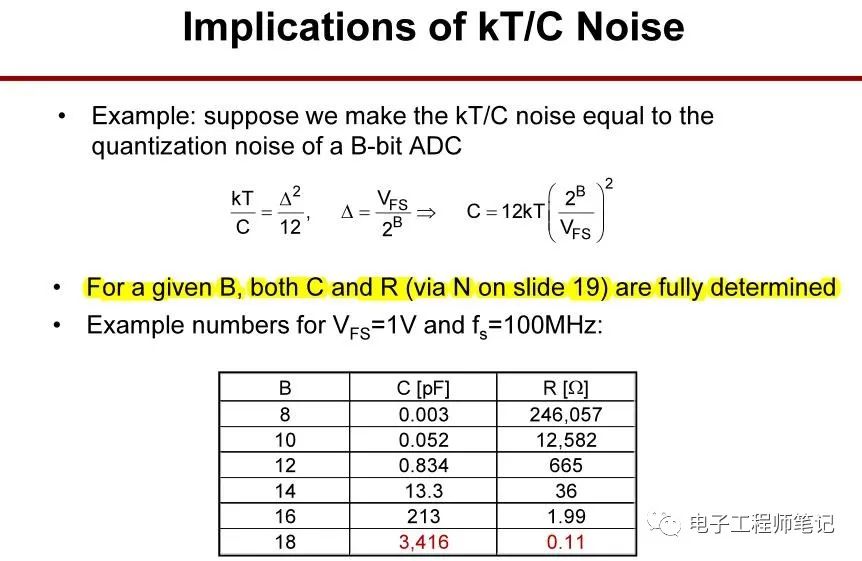

當(dāng)熱噪聲與量化噪聲的功率相同時(shí),ADC的位數(shù),全量程電壓和信號(hào)頻率可以決定電容C和電阻R。

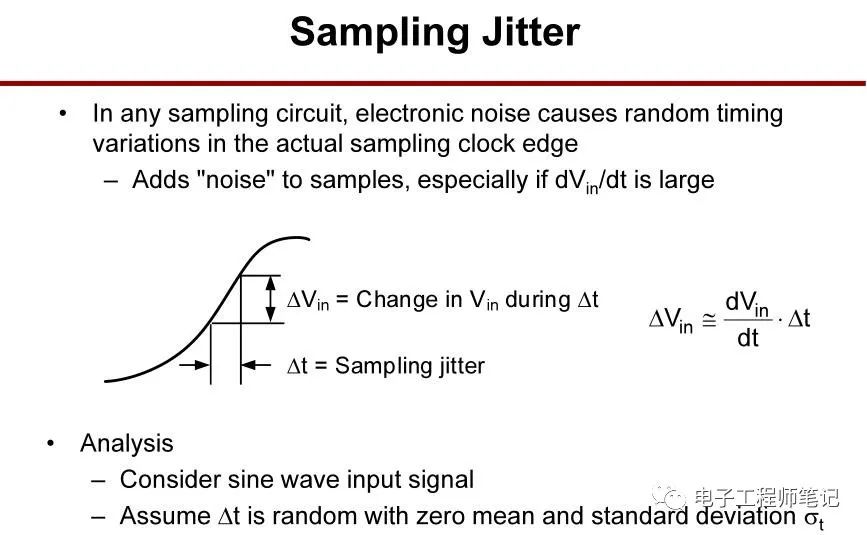

1.5 時(shí)鐘抖動(dòng)

采樣的抖動(dòng)帶來(lái)了噪聲。

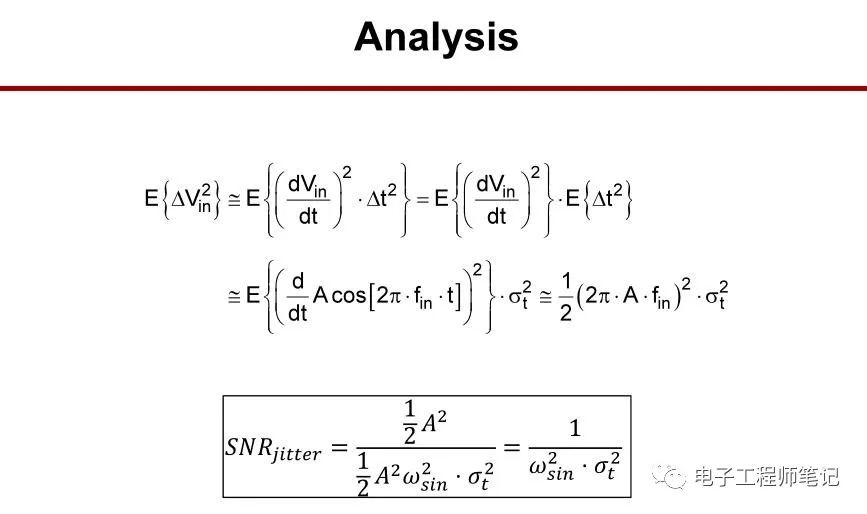

抖動(dòng)的信噪比可以通過(guò)輸入信號(hào)的頻率與抖動(dòng)的方差來(lái)計(jì)算。

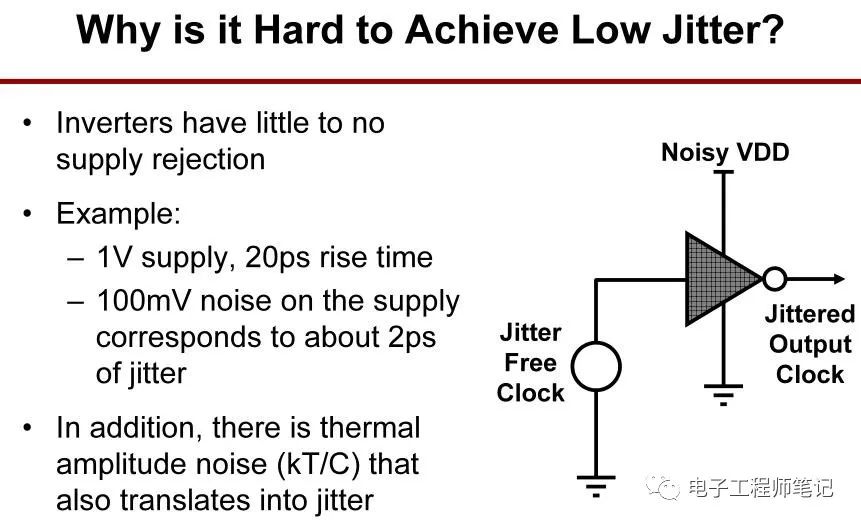

抖動(dòng)來(lái)源于電源的噪聲或熱噪聲。

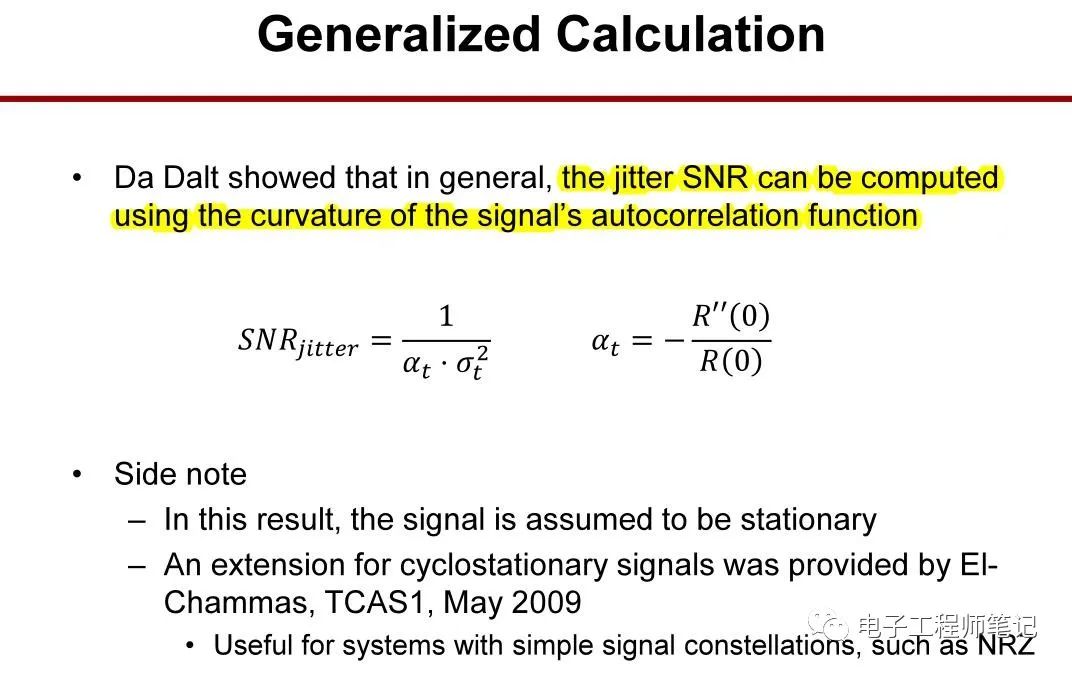

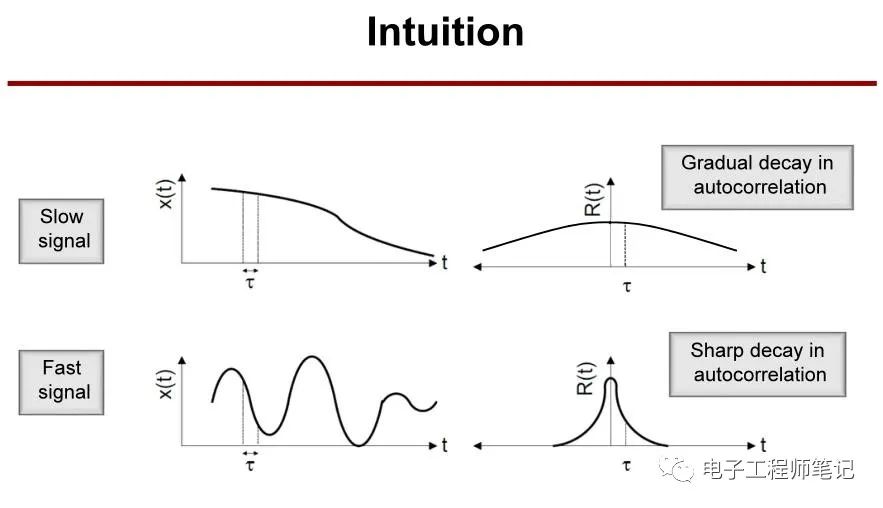

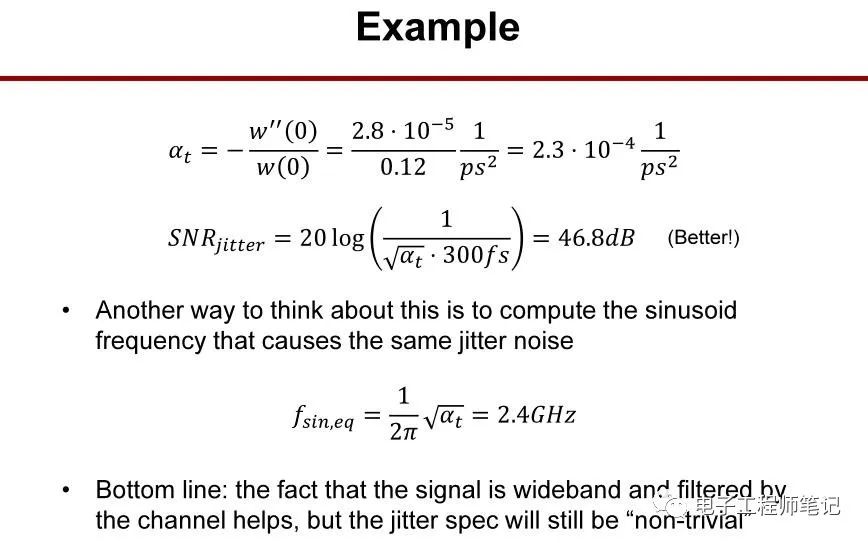

抖動(dòng)的信噪比也可以通過(guò)信號(hào)的自相關(guān)函數(shù)的曲率計(jì)算。

?

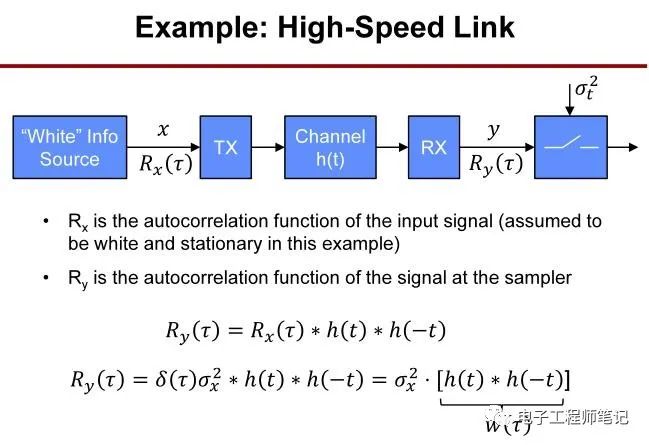

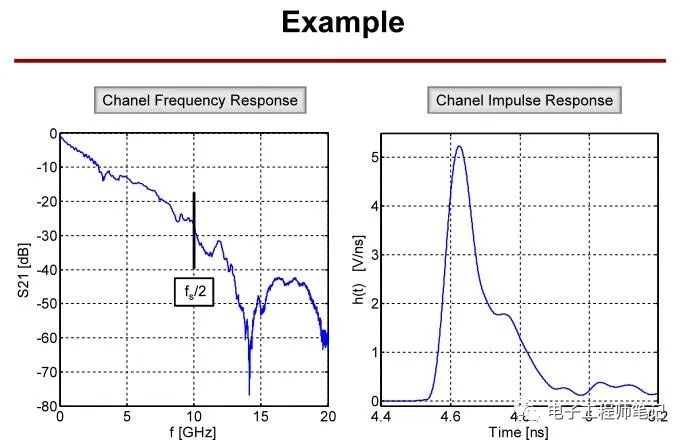

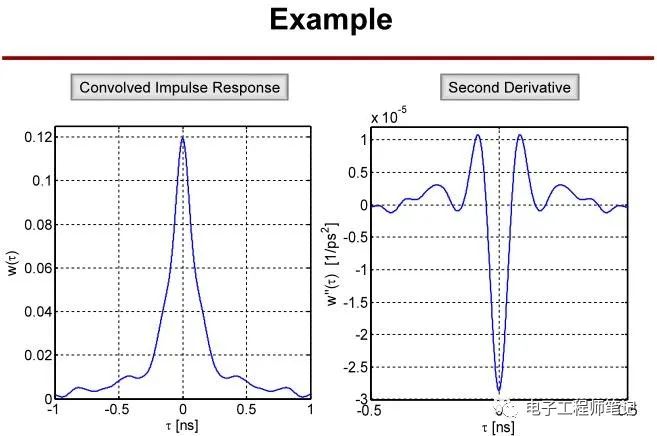

這是一個(gè)信號(hào)經(jīng)過(guò)信道的抖動(dòng)信噪比計(jì)算示例。

?

?

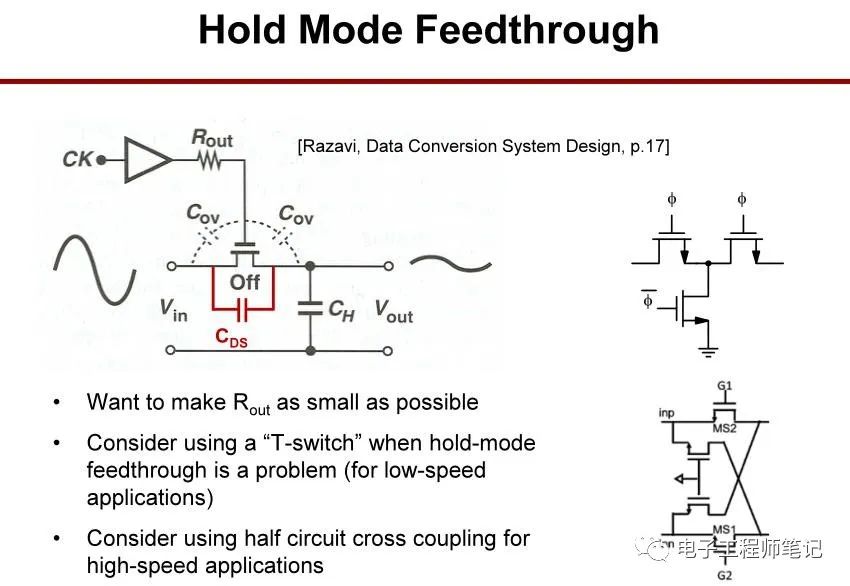

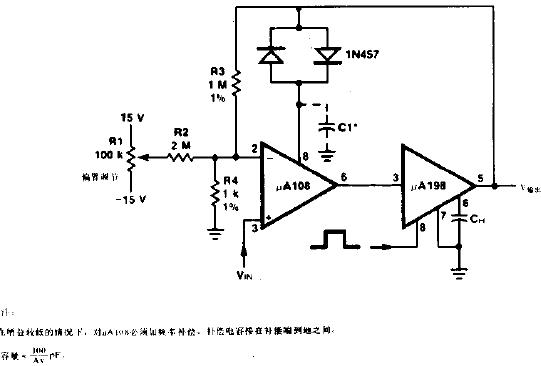

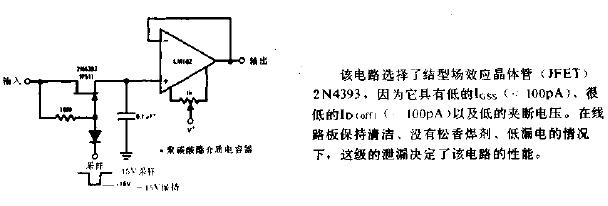

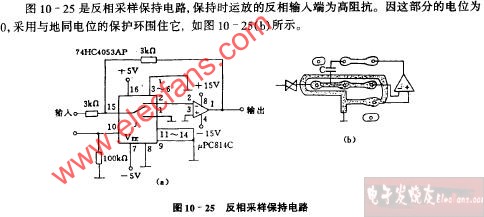

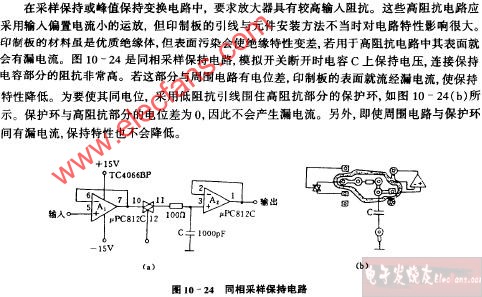

1.6 保持模式饋通和泄漏

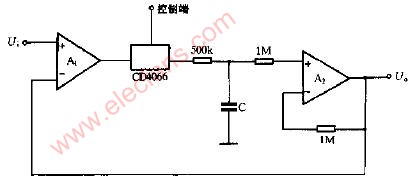

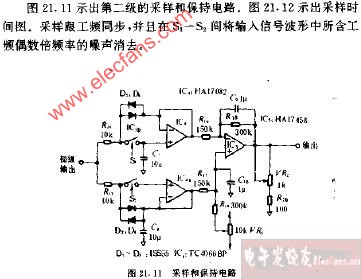

低速應(yīng)用使用?“T”開(kāi)關(guān),高速應(yīng)用使用半電路交叉耦合開(kāi)關(guān)。

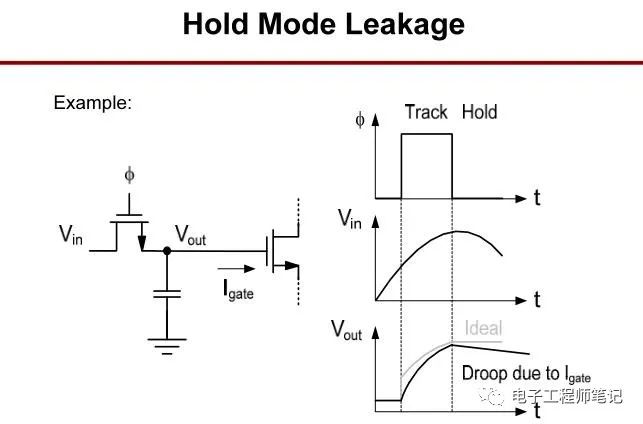

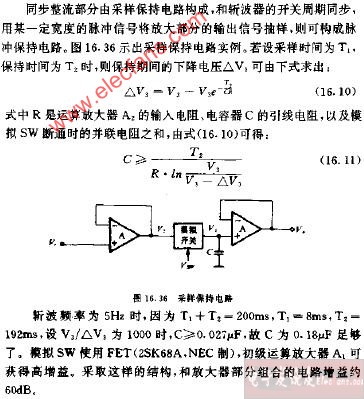

在保持模式時(shí),信號(hào)由于柵電流泄露會(huì)導(dǎo)致保持電壓下降。

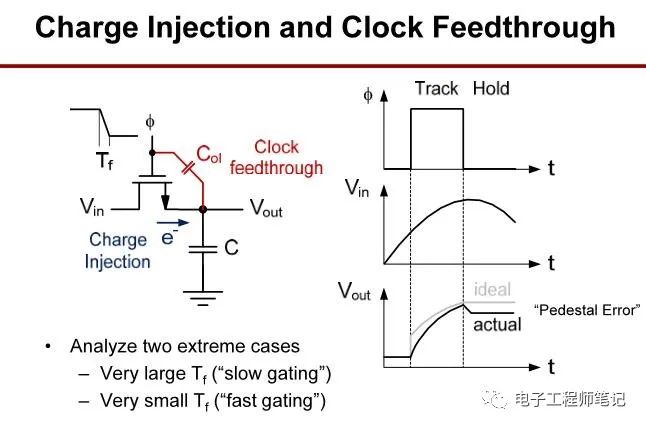

1.7 電荷注入和時(shí)鐘饋通

電荷注入與時(shí)鐘饋通的產(chǎn)生與影響。

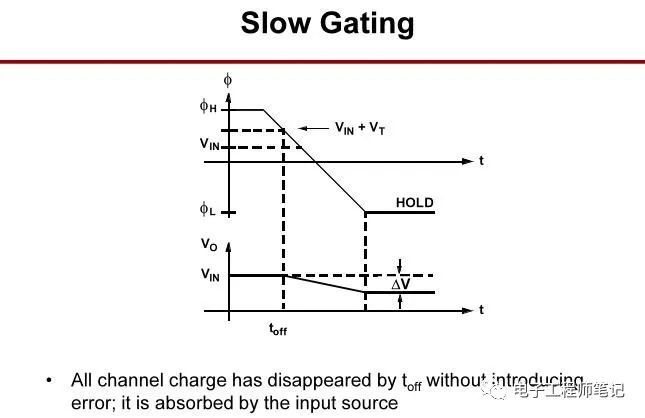

慢柵即開(kāi)關(guān)關(guān)斷轉(zhuǎn)換較慢,在關(guān)斷過(guò)程中,MOS管從電容中抽取部分電子補(bǔ)充溝道,出現(xiàn)了時(shí)鐘饋通。

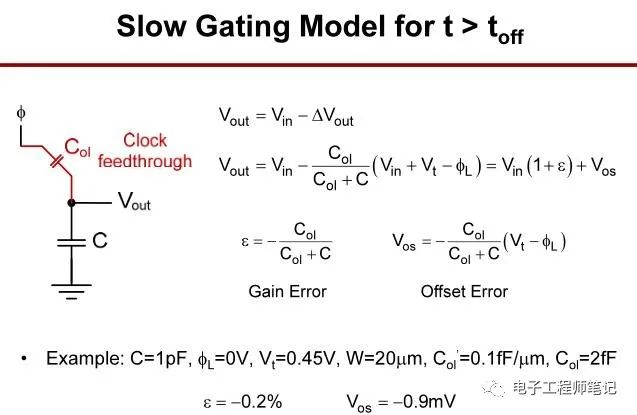

時(shí)鐘饋通模型帶來(lái)了增益與失調(diào)的誤差。

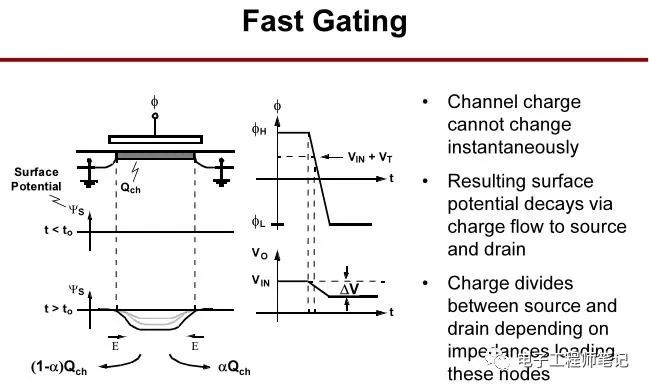

溝道電荷不能瞬間改變,由此產(chǎn)生的表面電位通過(guò)電荷流向源極和漏極而衰減,電荷在源極和漏極之間分配取決于加載這些節(jié)點(diǎn)的阻抗。

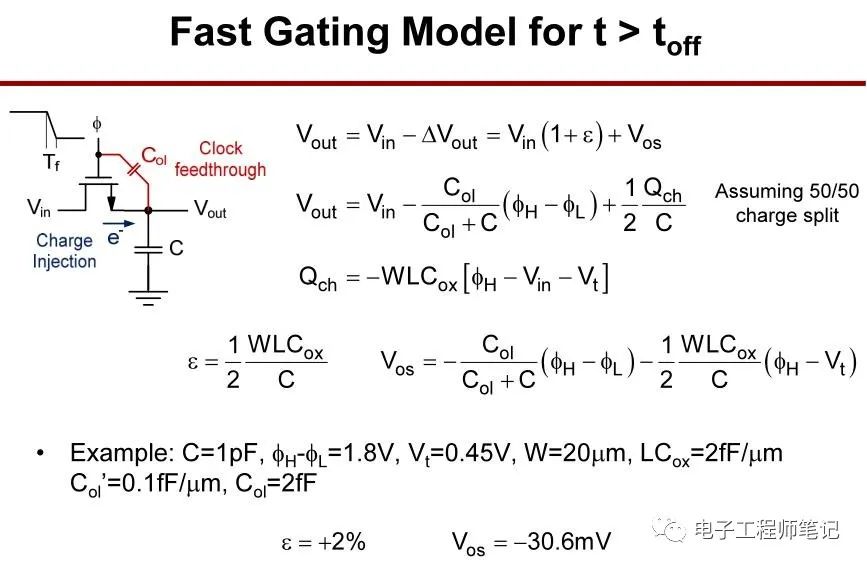

快柵即開(kāi)關(guān)關(guān)斷轉(zhuǎn)換較快,導(dǎo)致時(shí)鐘饋通與電荷注入,產(chǎn)生增益與失調(diào)誤差。

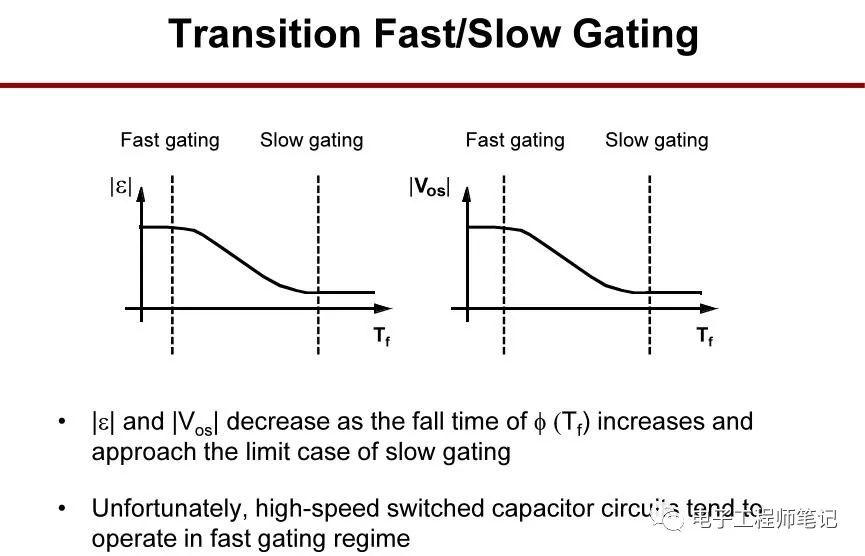

快柵帶來(lái)的增益與失調(diào)誤差較大,慢柵帶來(lái)的增益與失調(diào)誤差較小,?但高速開(kāi)關(guān)電容電路傾向于在快柵狀態(tài)下工作。

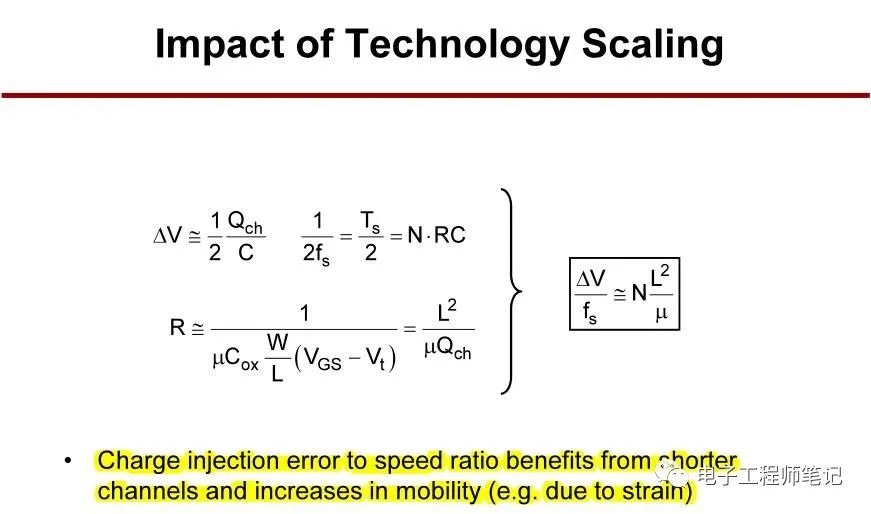

電荷注入誤差與速度之比取決于更短的溝道(L)和更大的遷移率(μ)。

二. 初級(jí)跟蹤保持的一階改進(jìn)

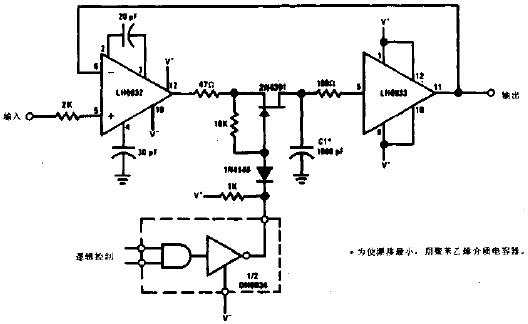

2.1 電荷消除

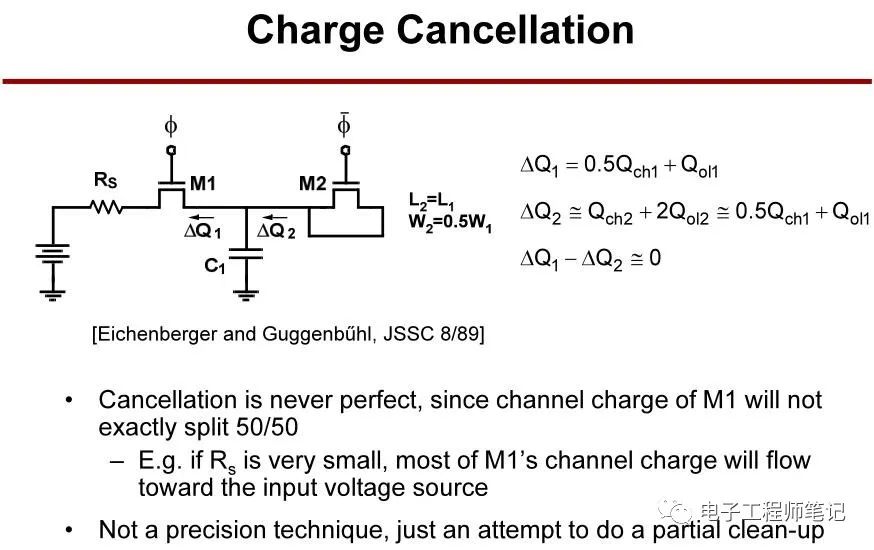

通過(guò)增加另一個(gè)MOS管的反向時(shí)鐘饋通來(lái)抵消電荷被時(shí)鐘饋通抽取的影響。這不是一種精確的技術(shù),只是一種部分抵消的嘗試。

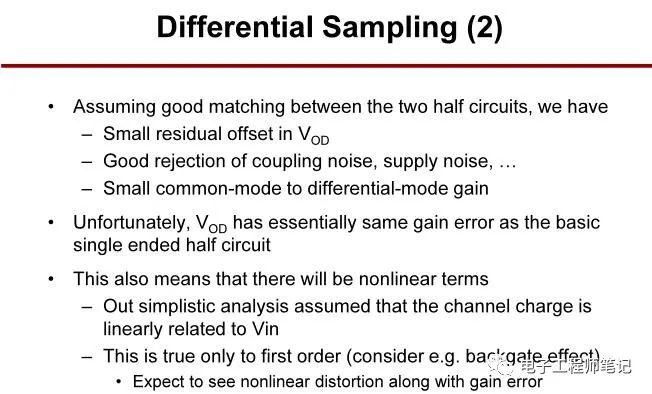

2.2 差分采樣

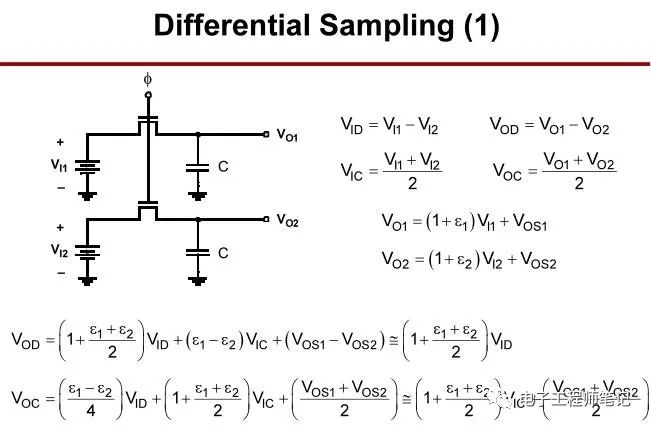

?

假設(shè)兩個(gè)半電路之間匹配良好,差分采樣具有很小的電壓失調(diào),很好的耦合噪聲和電源噪聲抑制能力,很小的共模到差模增益。但是增益誤差與單端相同,同時(shí)會(huì)具有非線性項(xiàng)。

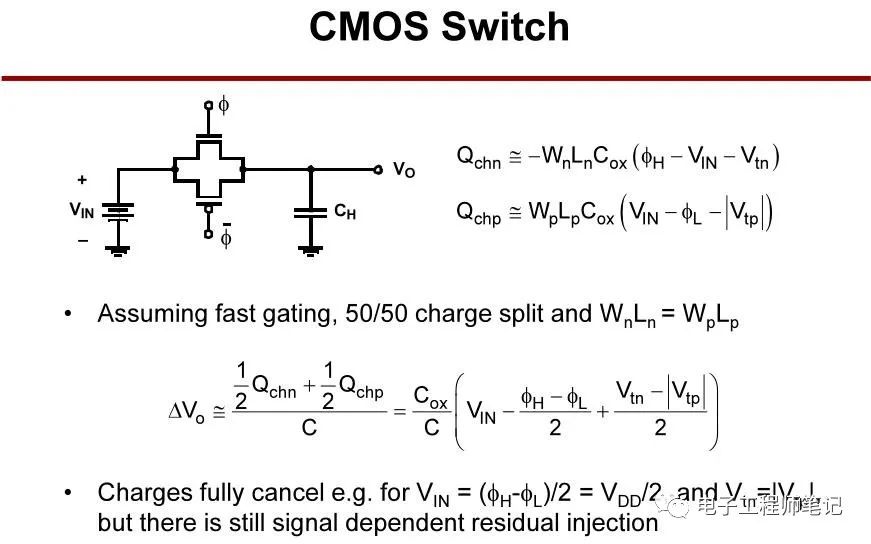

2.3 CMOS開(kāi)關(guān)

對(duì)于?V I N = ( ? H ? ? L ) / 2 = V D D / 2 和 V t n = ∣ V t p ∣ V_IN = ( phi_H-phi_L)/2 = V_DD /2和V_tn =|V_tp |?VIN=(?H??L)/2=VDD/2和Vtn=∣Vtp∣,電荷完全抵消,但仍有信號(hào)相關(guān)的殘余注入。

?

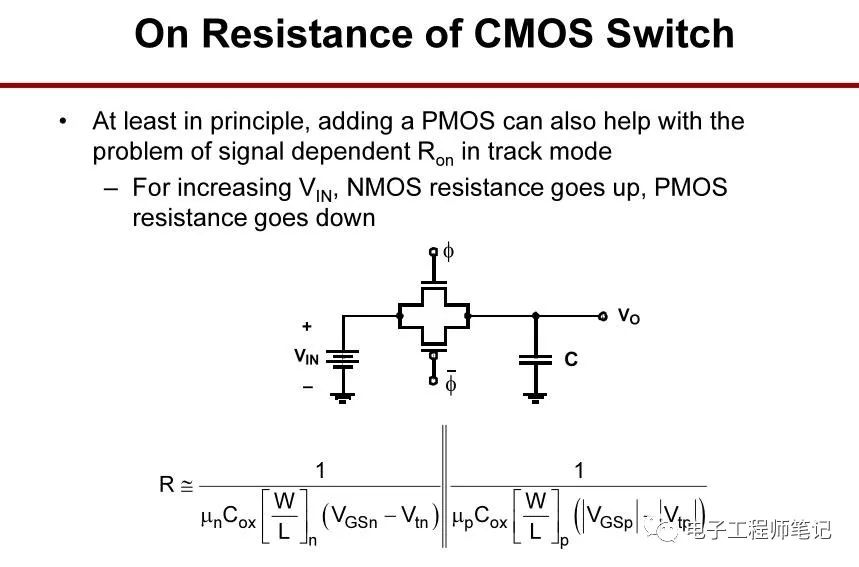

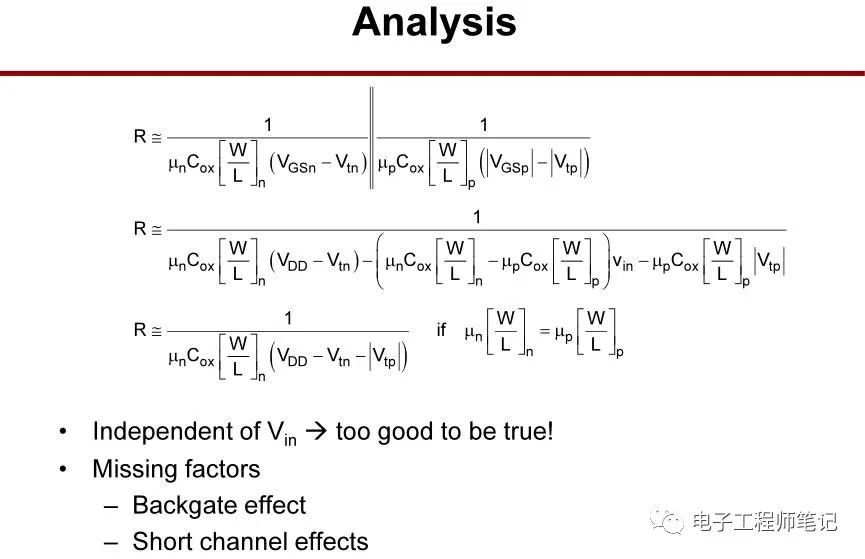

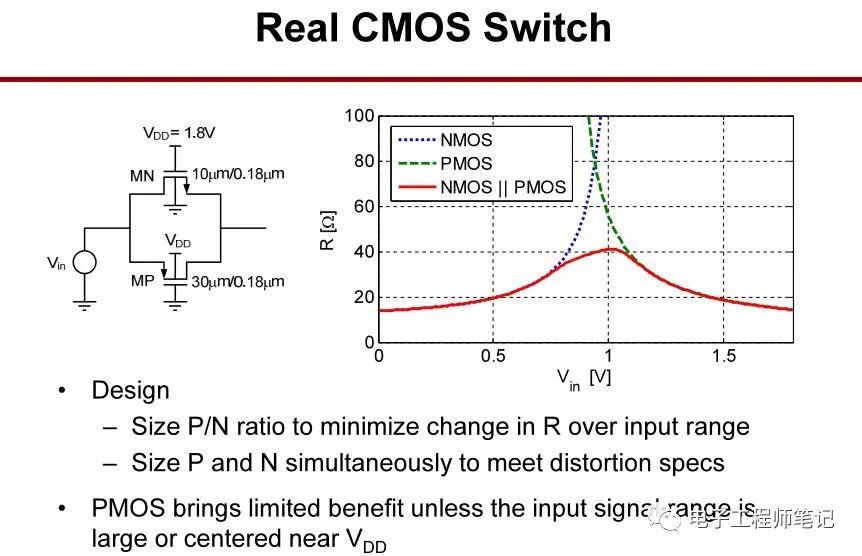

增加一個(gè)PMOS也有助于解決跟蹤模式下信號(hào)依賴開(kāi)關(guān)電阻?R R?R的問(wèn)題,電阻?R R?R與輸入?V i n V_in?Vin無(wú)關(guān)。

真實(shí)情況下,需要調(diào)整P/N比,使輸入范圍內(nèi)的電阻變化最小。

三. 先進(jìn)技術(shù)

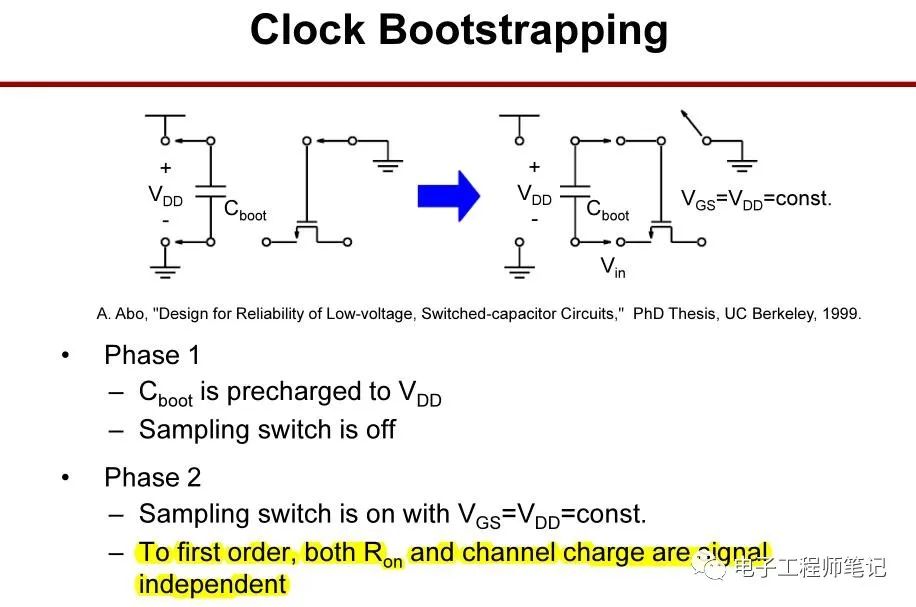

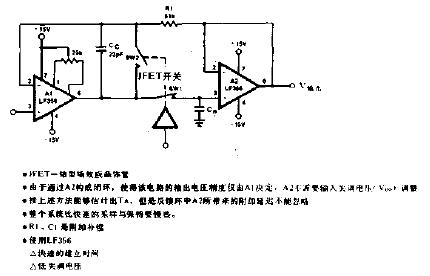

3.1 時(shí)鐘自舉

使用時(shí)鐘自舉技術(shù),柵極電壓始終比輸入信號(hào)電壓高?V D D V_DD?VDD,實(shí)現(xiàn)了恒定的?V G S V_GS?VGS,開(kāi)關(guān)電阻和溝道電荷與輸入信號(hào)不相關(guān),消除了跟蹤非線性影響。

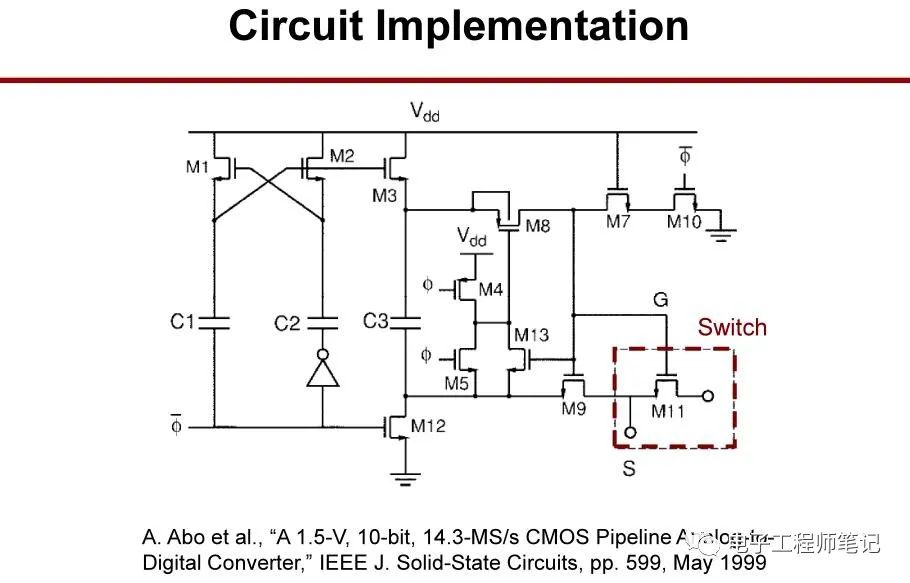

時(shí)鐘自舉電路的實(shí)現(xiàn)方法,但仍存在一些問(wèn)題。

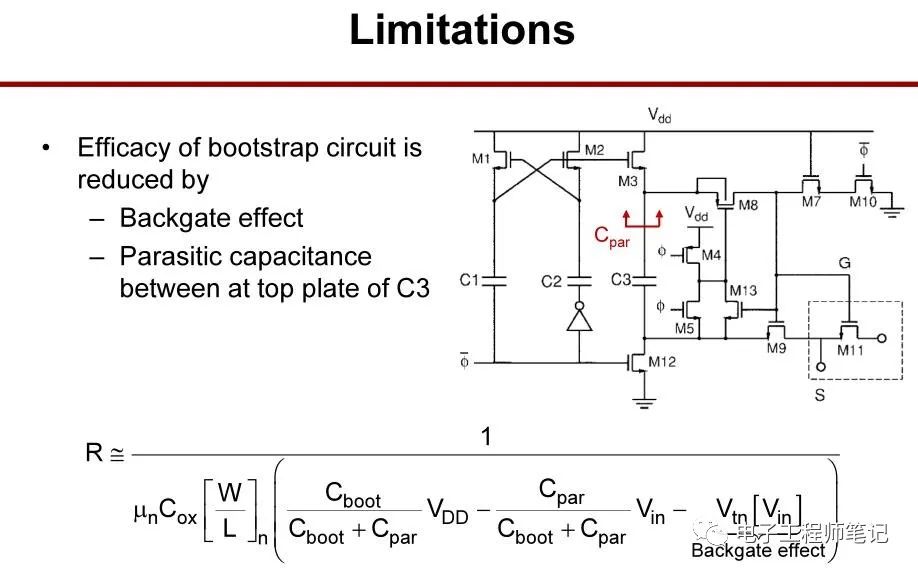

背柵效應(yīng)和寄生電容會(huì)減小自舉電路的效率。

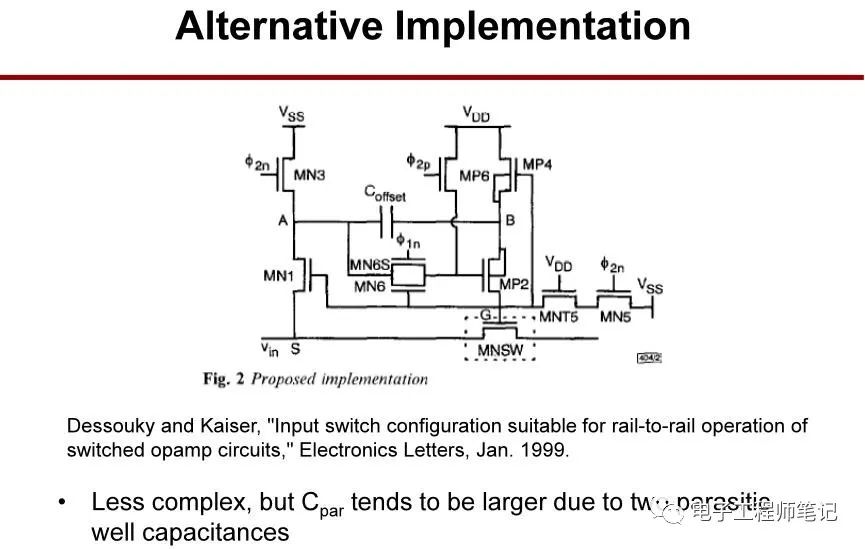

另一種自舉電路的實(shí)現(xiàn)更簡(jiǎn)單,但寄生電容更大。

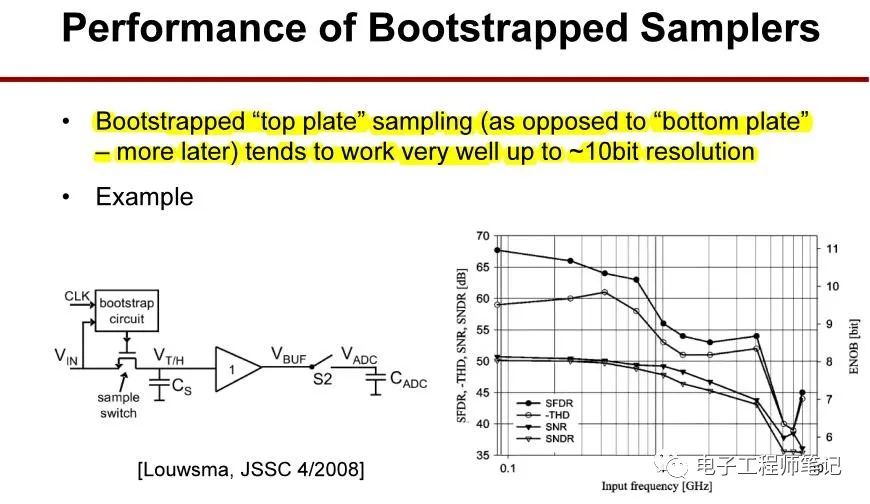

自舉技術(shù)是頂板采樣,在10位以內(nèi)的分辨率下效果較好。

3.2 底板采樣

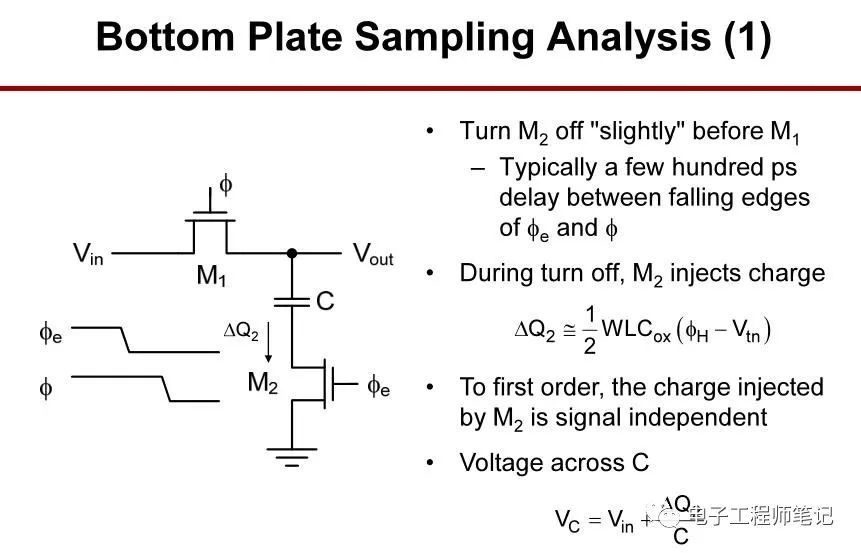

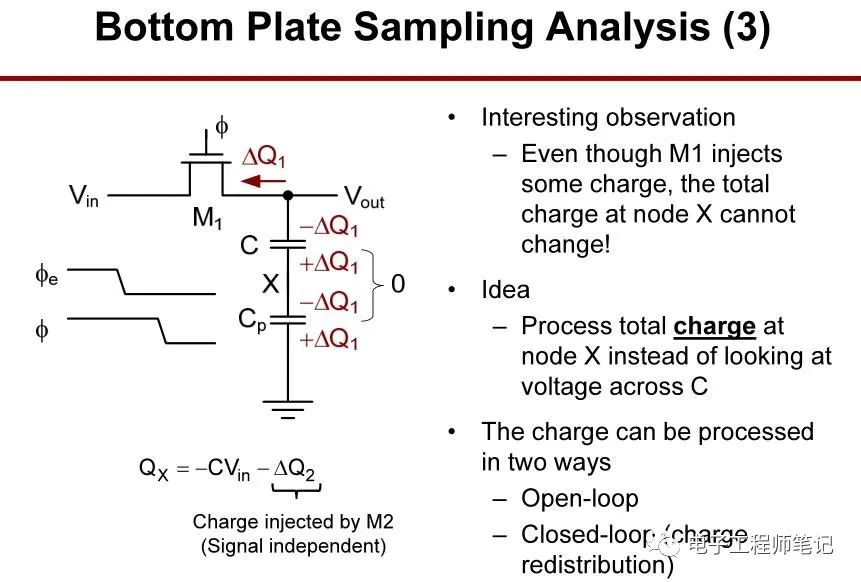

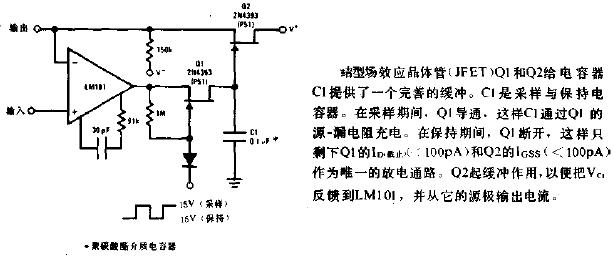

M2閉合時(shí),由于電荷注入效應(yīng),M2從電容C抽取電荷?Δ Q 2 Delta Q_2?ΔQ2。這是與信號(hào)?V i n V_in?Vin無(wú)關(guān)的。

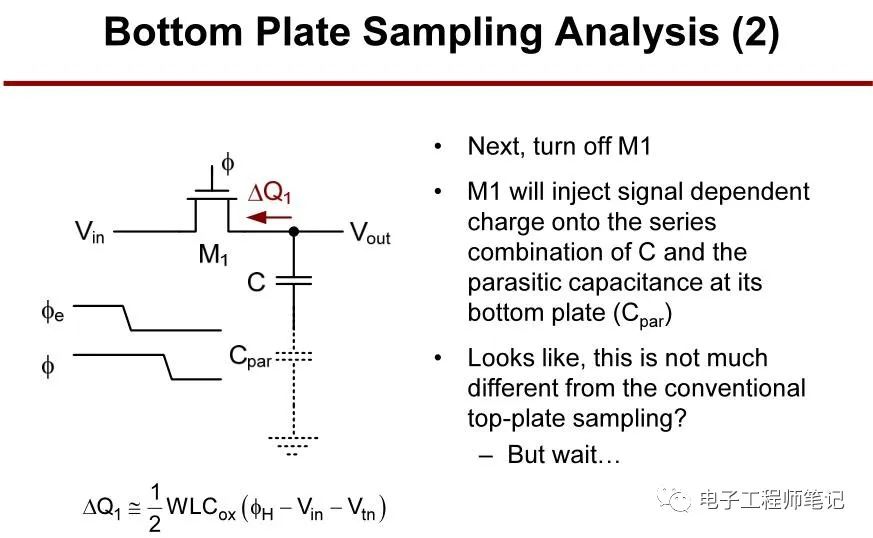

M1閉合時(shí),同樣由于電荷注入效應(yīng),M1從電容C與寄生電容Cpar(來(lái)自M2)的串聯(lián)電容中抽取電荷?Δ Q 1 Delta Q_1?ΔQ1。這是與信號(hào)?V i n V_in?Vin相關(guān)的。

M1與M2相繼閉合后,分析X點(diǎn)處的電荷量并沒(méi)有發(fā)生變化。

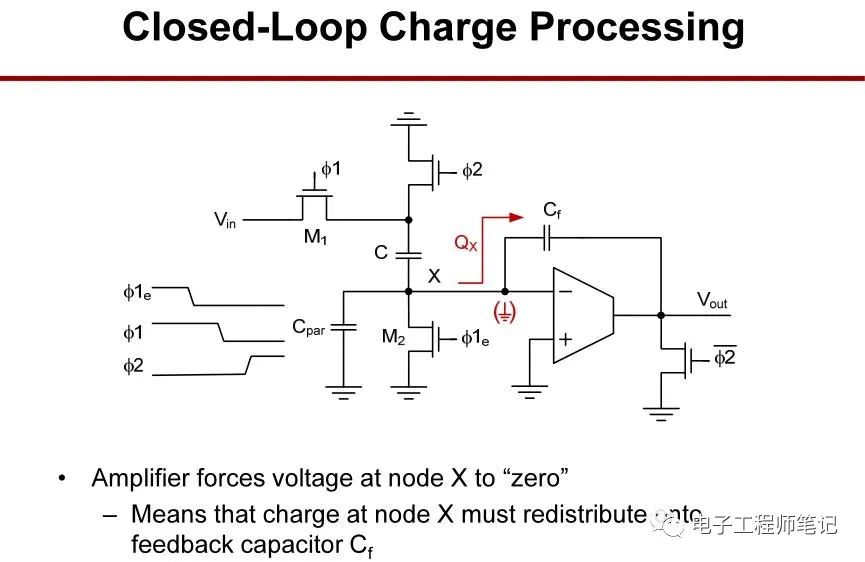

使用閉環(huán)跟隨器,可以使X點(diǎn)處的電壓鉗制在地點(diǎn)位,X點(diǎn)處的電荷重分配至反饋電容?C f C_f?Cf。

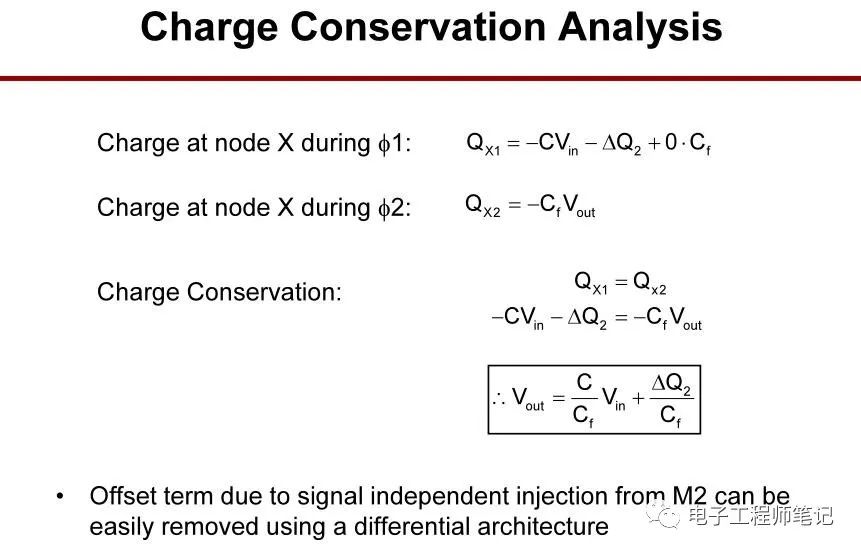

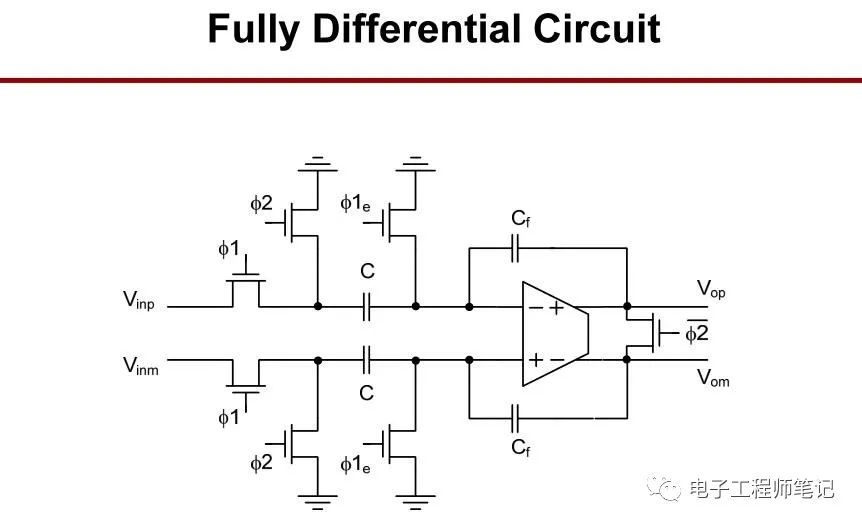

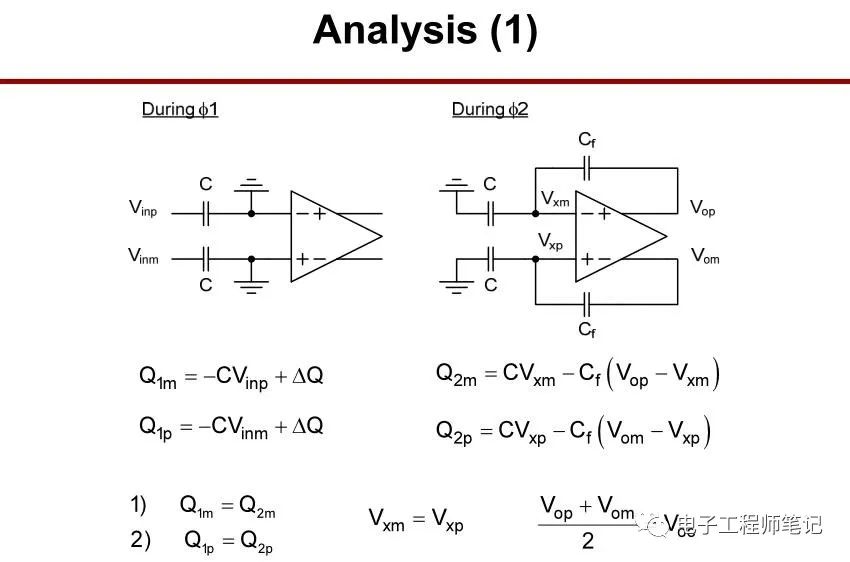

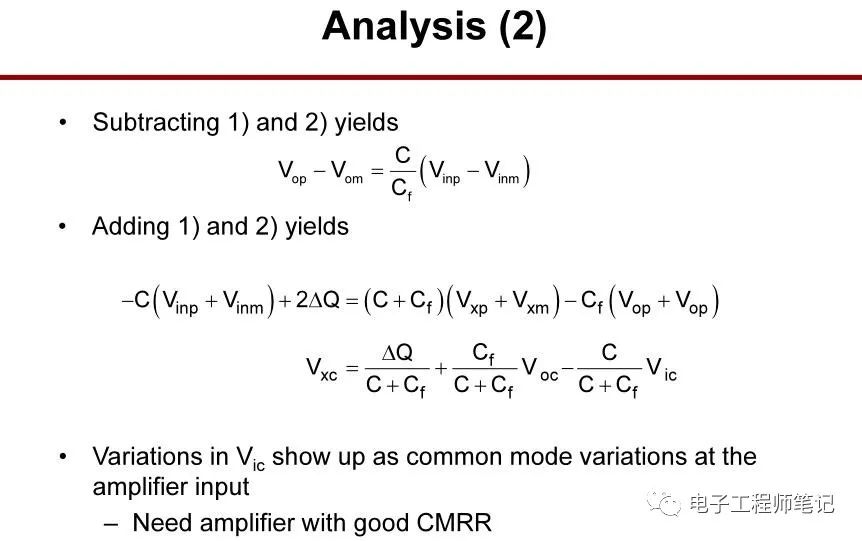

通過(guò)?? 1 phi 1??1與?? 2 phi 2??2階段的電荷分配,電荷守恒,可建立等式得出,最終采樣后的輸出電壓與輸入電壓之間的關(guān)系。使用差分架構(gòu)可以消除M2信號(hào)獨(dú)立注入引起的失調(diào)項(xiàng)。

?

?

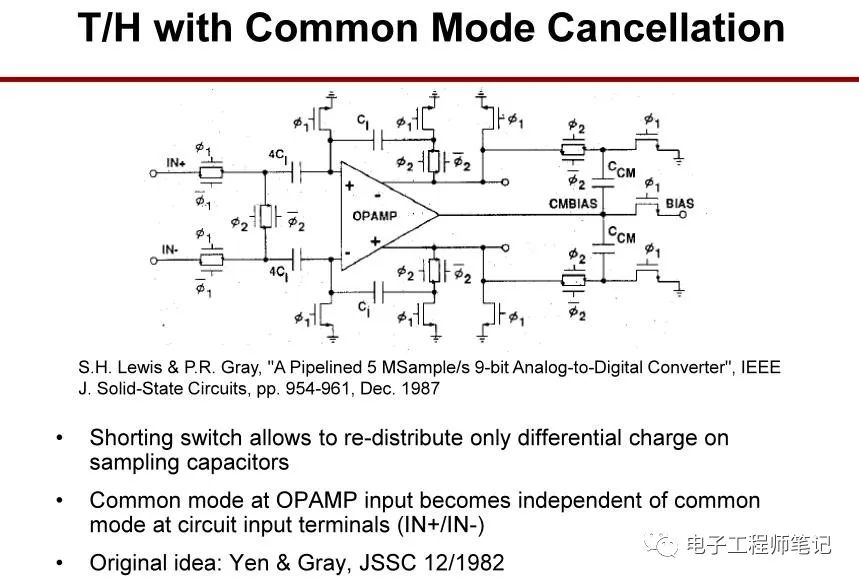

但是差分結(jié)構(gòu)會(huì)帶來(lái)共模失調(diào)。下面是一些解決方案。

?

四. 電荷再分配采樣保持電路的建立和噪聲分析

4.1 建立分析

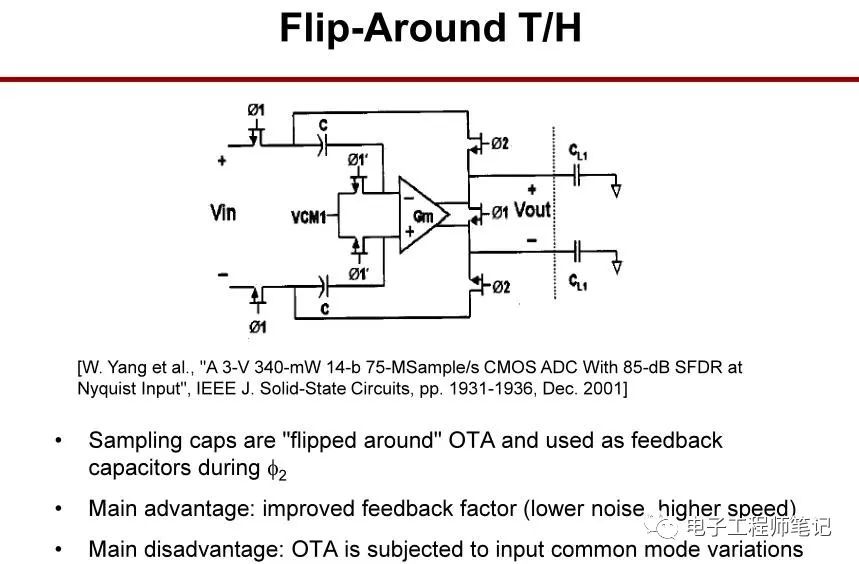

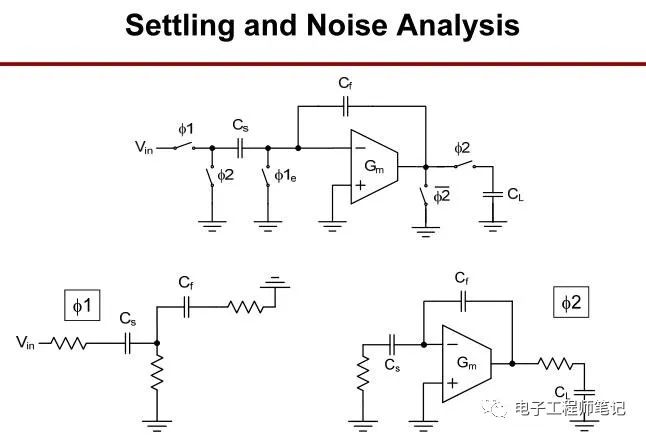

前面分析的電荷再分配采樣保持電路工作分為兩個(gè)階段。

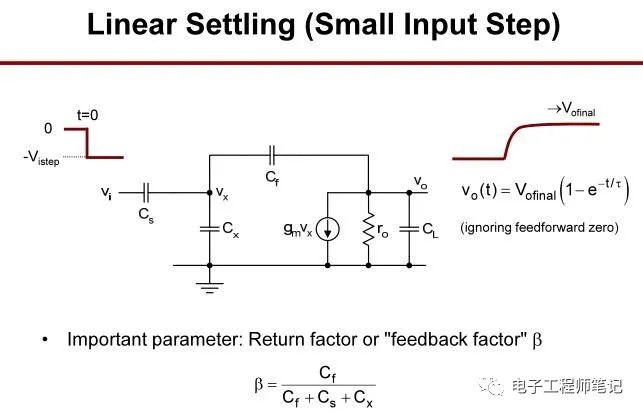

對(duì)于小信號(hào)的階躍輸入,輸出體現(xiàn)了線性建立過(guò)程,其中最重要的參數(shù)是反饋因子?β β?β。

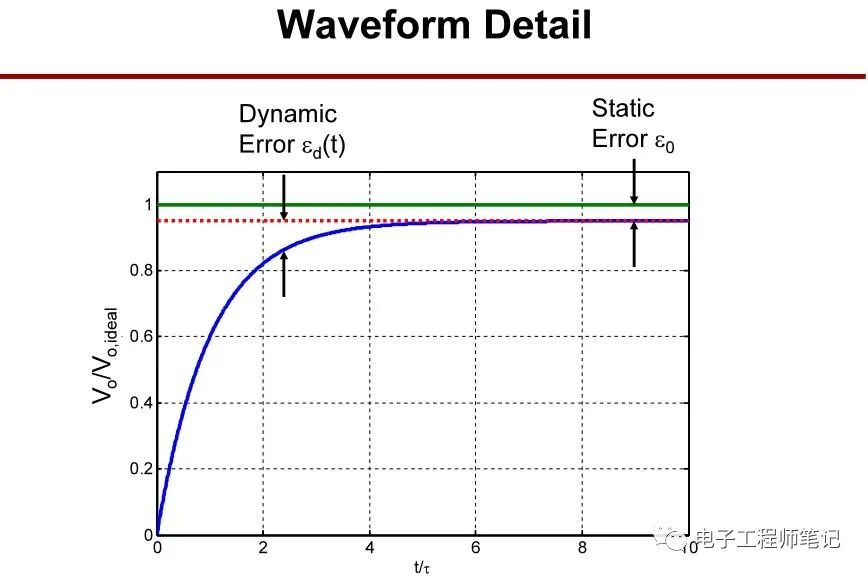

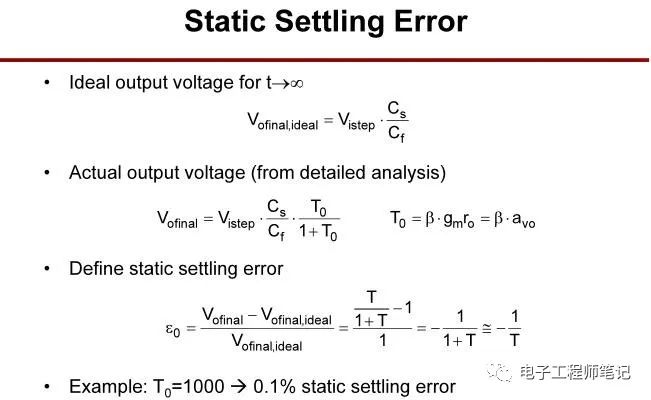

建立的波形如圖所示,開(kāi)始的動(dòng)態(tài)誤差與時(shí)間有關(guān),但最終會(huì)趨向于一個(gè)輸出電壓,這個(gè)電壓與理想輸出之間的差距就是靜態(tài)誤差,此誤差與時(shí)間無(wú)關(guān)。

靜態(tài)建立誤差與?T 0 T_0?T0有關(guān),?T 0 T_0?T0定義為?β g m r o βg_mr_o?βgmro,其中?β β?β為反饋因子。

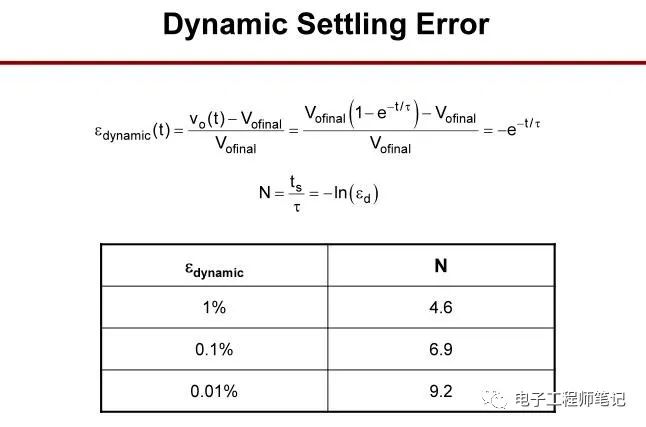

動(dòng)態(tài)誤差與位數(shù)N的關(guān)系。

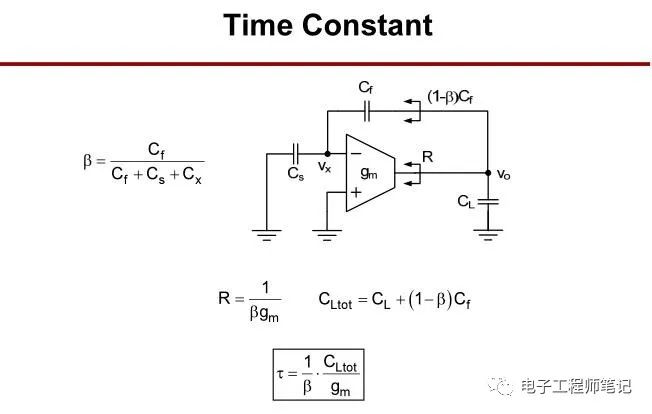

建立過(guò)程時(shí)間常數(shù)?τ τ?τ的定義。

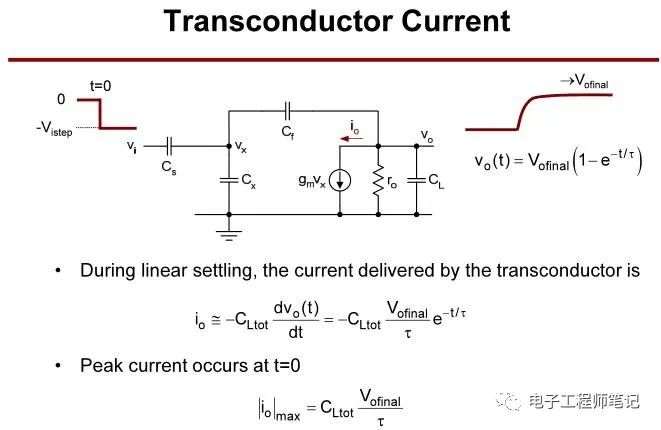

跨導(dǎo)電流及此電流的峰值。

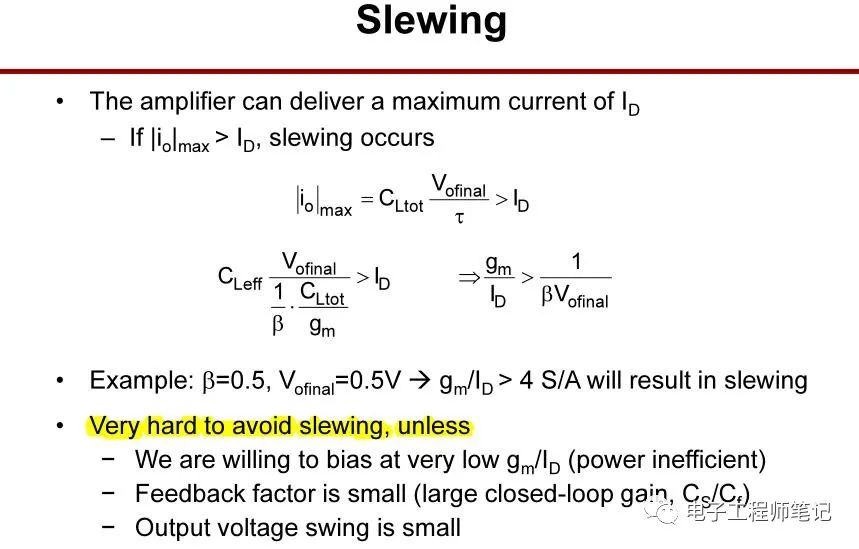

對(duì)于大信號(hào)階躍輸入,會(huì)導(dǎo)致輸出為轉(zhuǎn)換狀態(tài),即輸出電壓變化的斜率為定值,不隨時(shí)間而變化,通常難以避免。

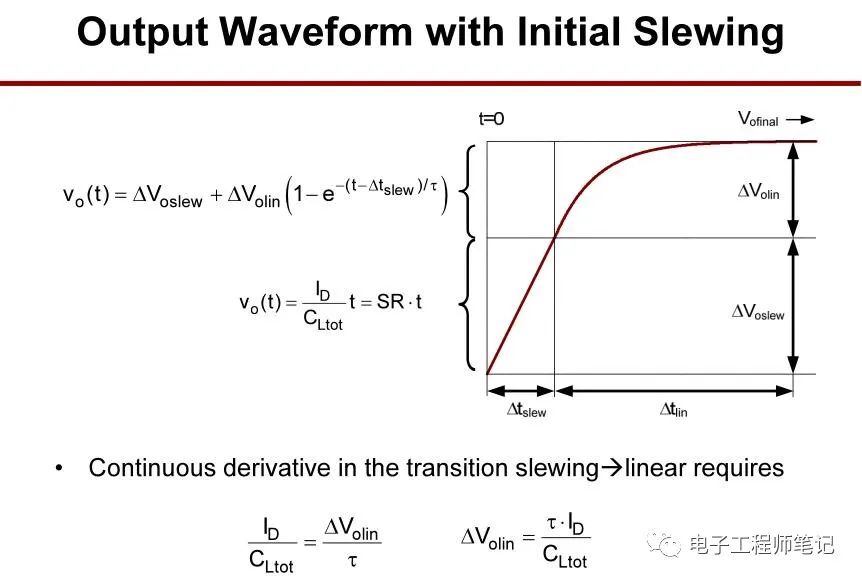

輸出從非線性轉(zhuǎn)換狀態(tài)過(guò)渡至線性的建立過(guò)程的輸出電壓波形及表達(dá)式。

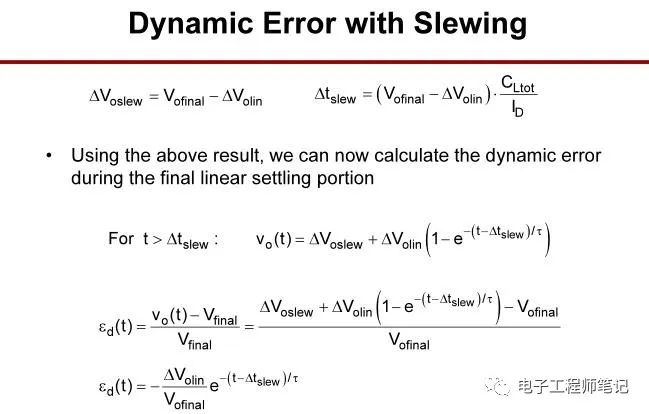

在轉(zhuǎn)換狀態(tài)下的動(dòng)態(tài)誤差公式。

4.2 噪聲分析

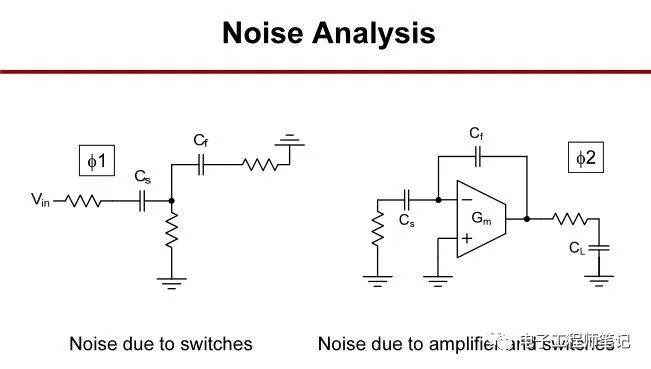

電荷再分配采樣保持電路的兩個(gè)過(guò)程中的噪聲產(chǎn)生與分析。

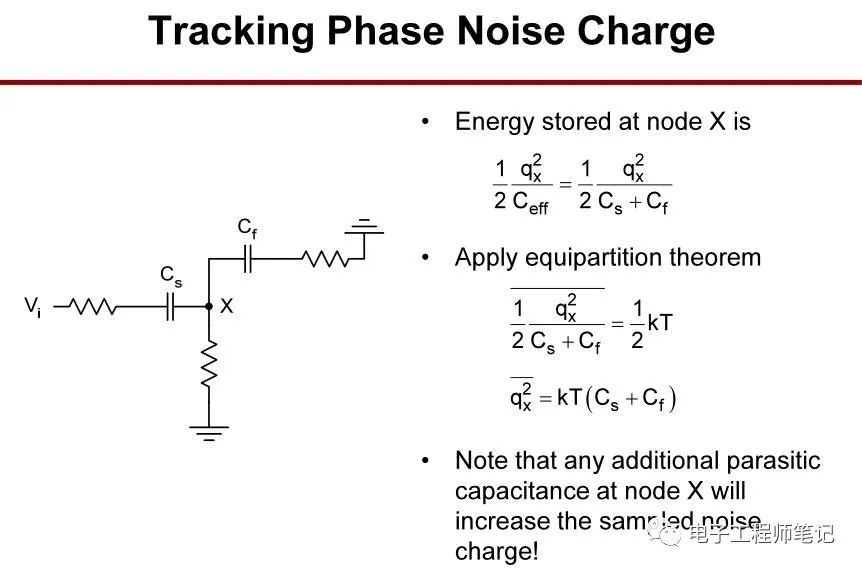

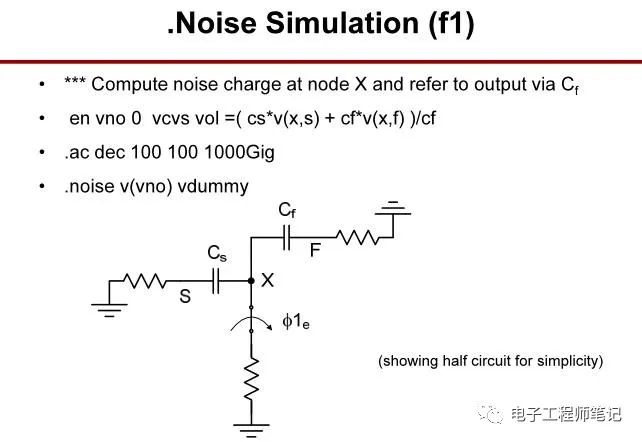

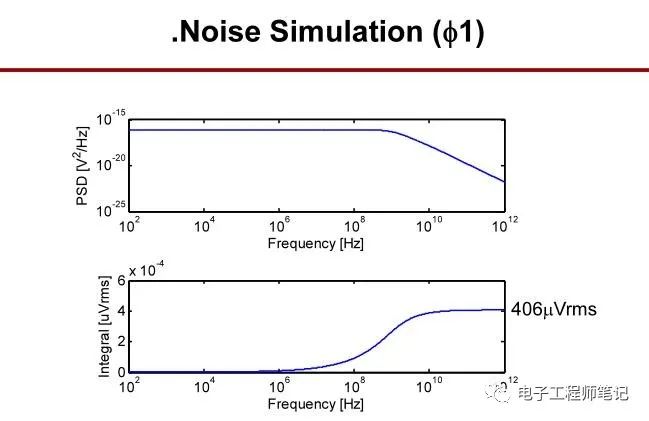

第一階段,跟蹤相位噪聲電荷的估計(jì)。

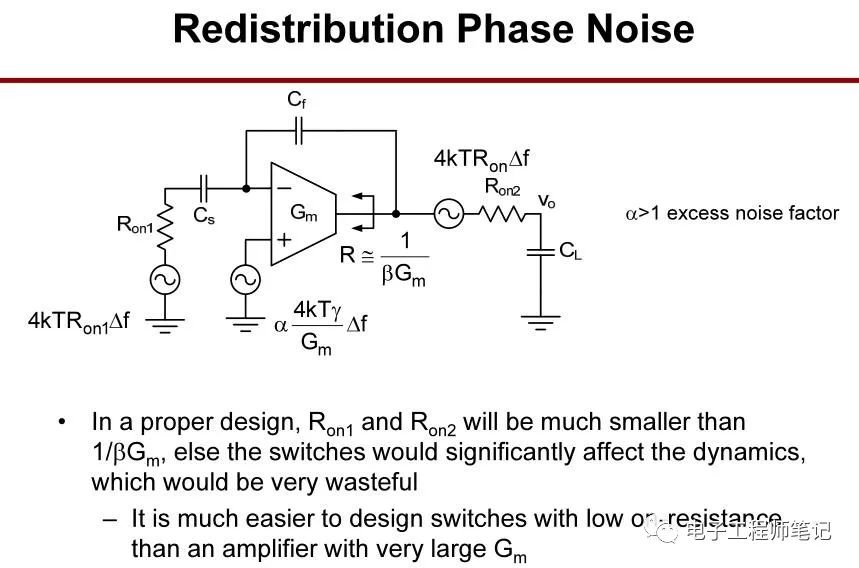

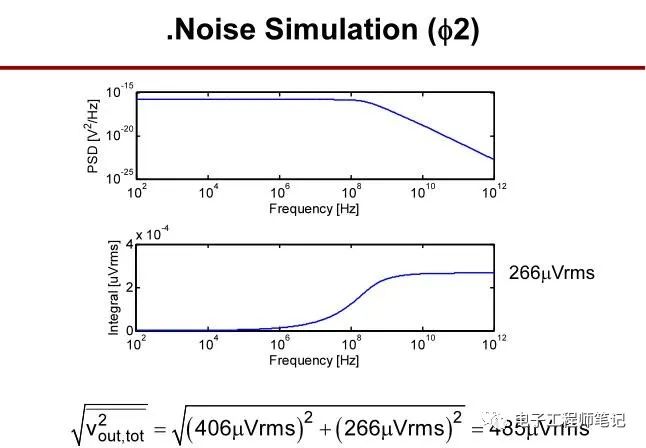

第二階段,再分配相位噪聲估計(jì)。

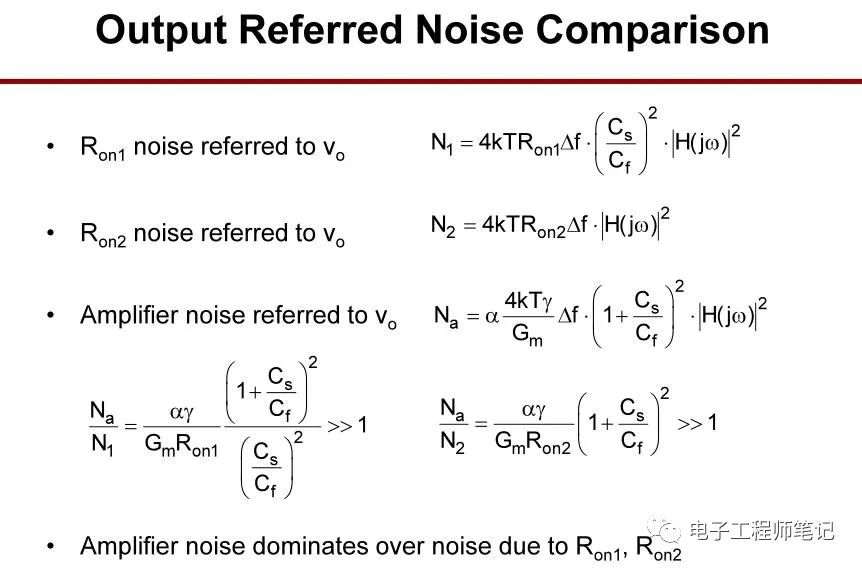

第二階段中,放大器的噪聲往往比開(kāi)關(guān)電阻?R o n 1 R_on1?Ron1和?R o n 2 R_on2?Ron2大的多。

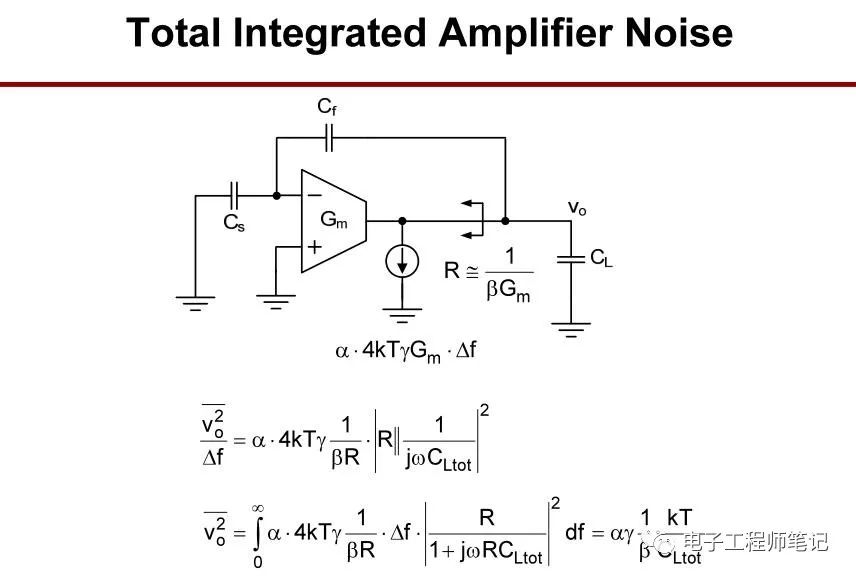

第二階段中,集成放大器的總噪聲。

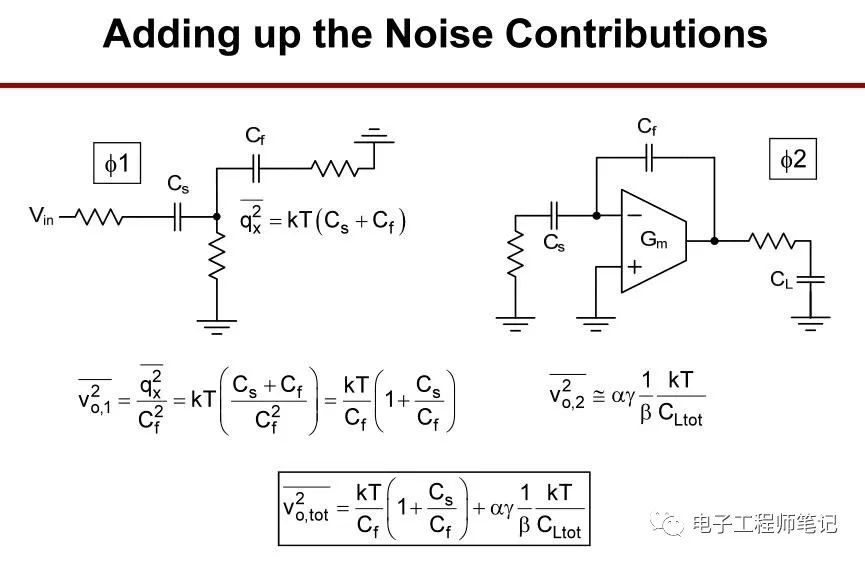

將第一階段與第二階段的噪聲貢獻(xiàn)相加,得到電荷再分配采樣保持電路的總噪聲。

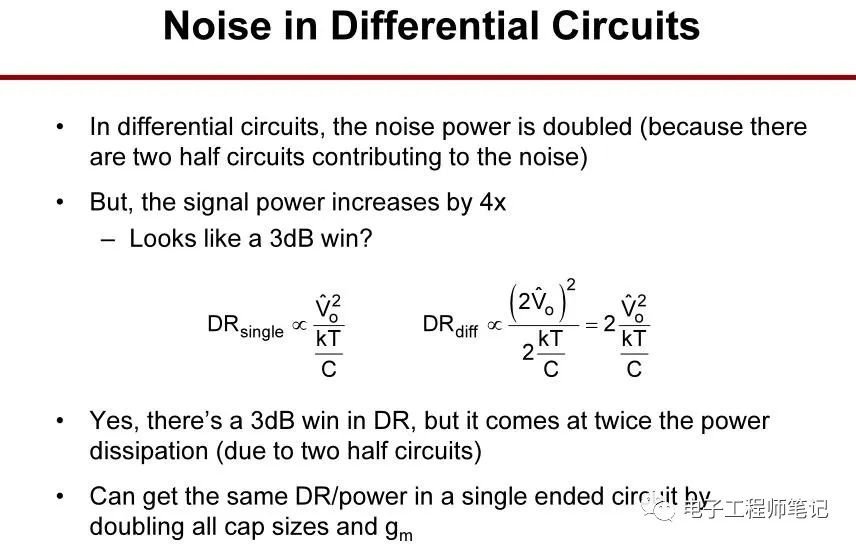

在差分電路中,噪聲功率加倍,但是信號(hào)功率增加了4倍。

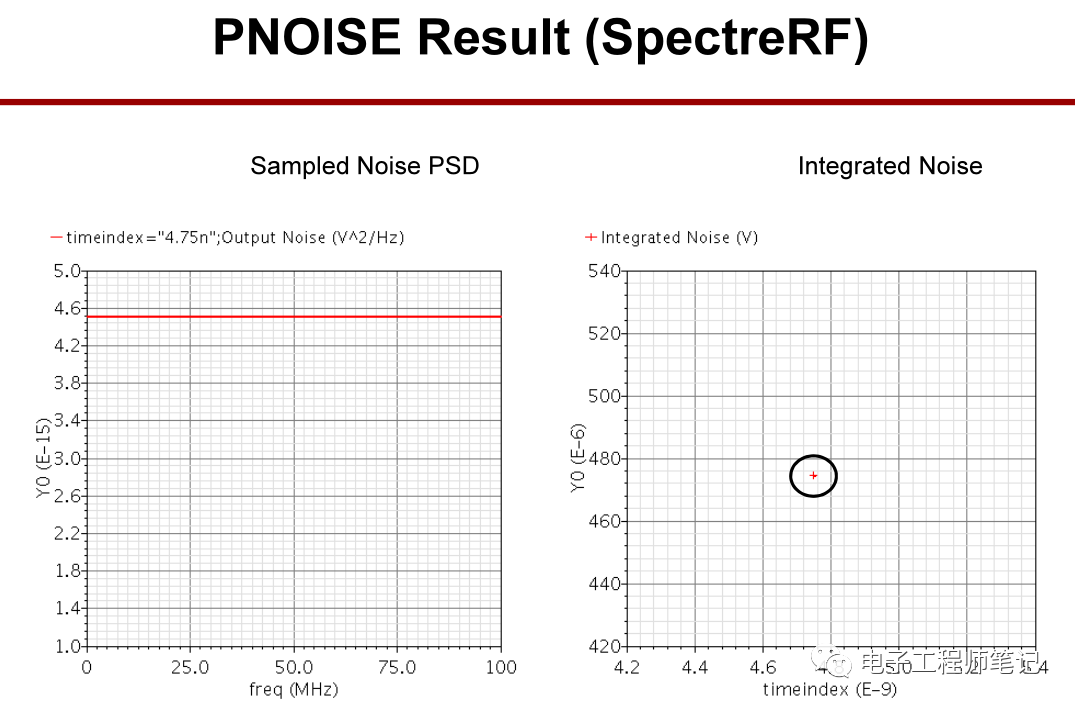

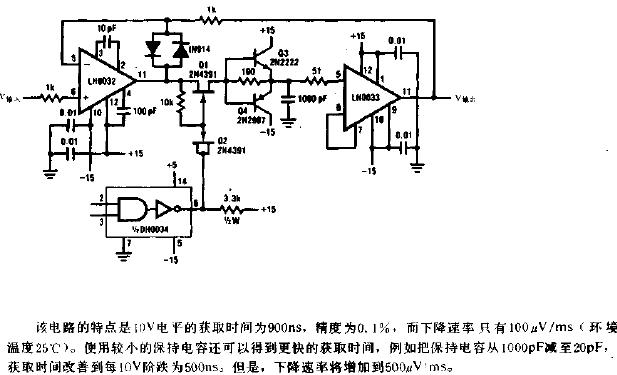

五. 噪聲仿真示例

?

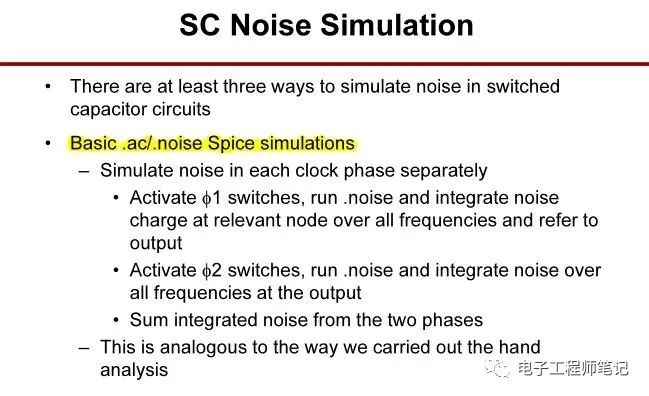

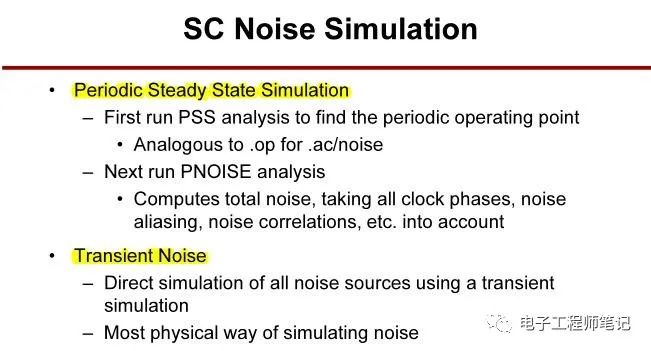

開(kāi)關(guān)電容的噪聲仿真通常有三種方法:基本的.ac/.noise Spice仿真,周期穩(wěn)態(tài)仿真,瞬態(tài)噪聲。

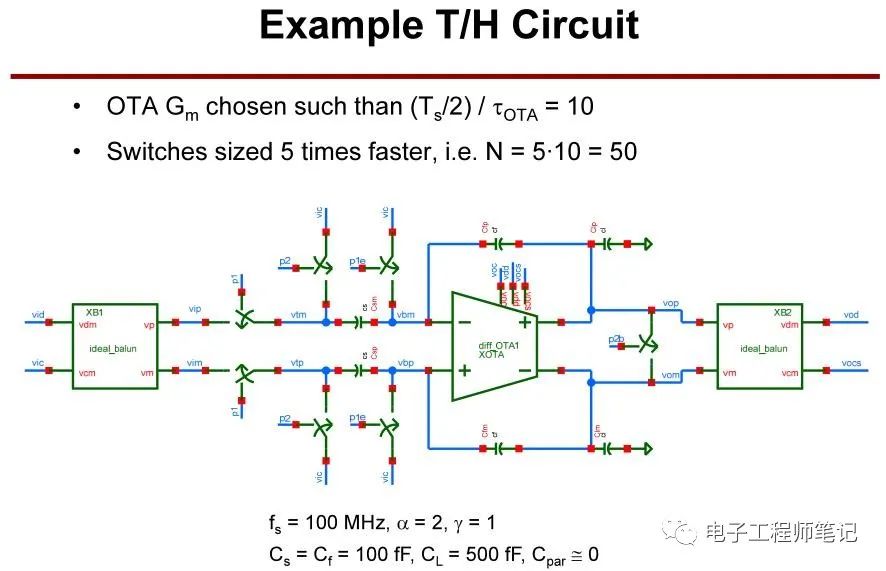

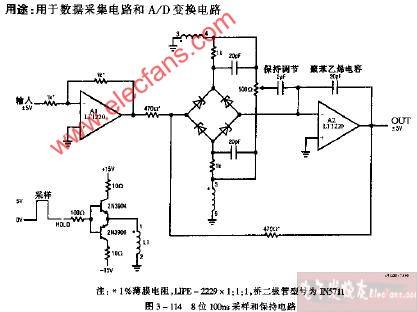

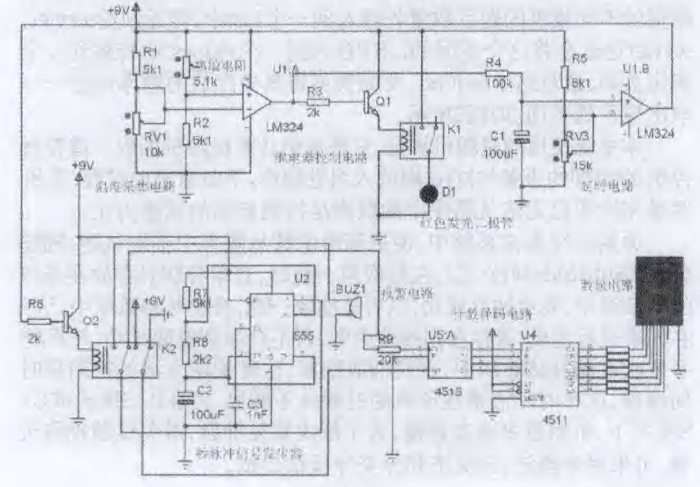

示例的采樣/保持電路及其參數(shù)如圖。

5.1 基本的.ac/.noise Spice仿真

?

?

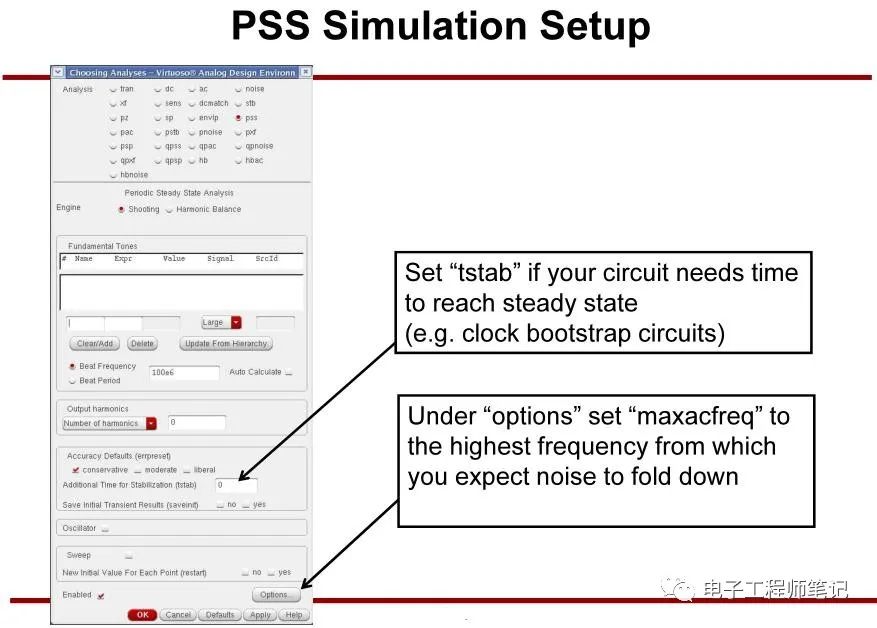

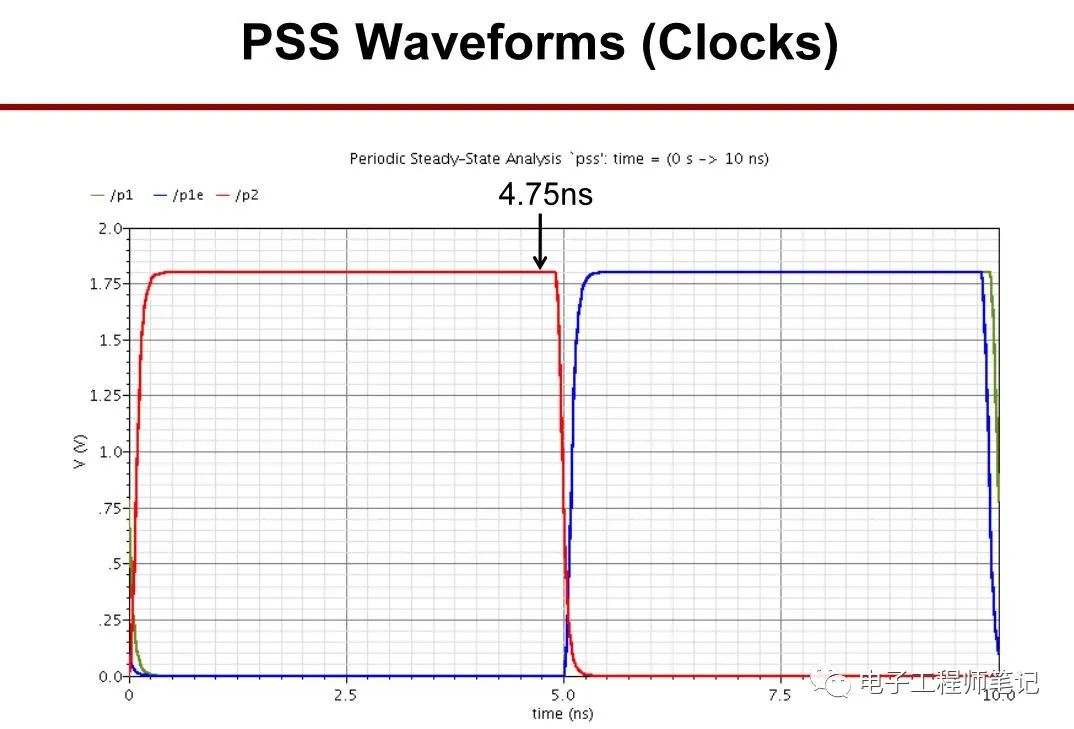

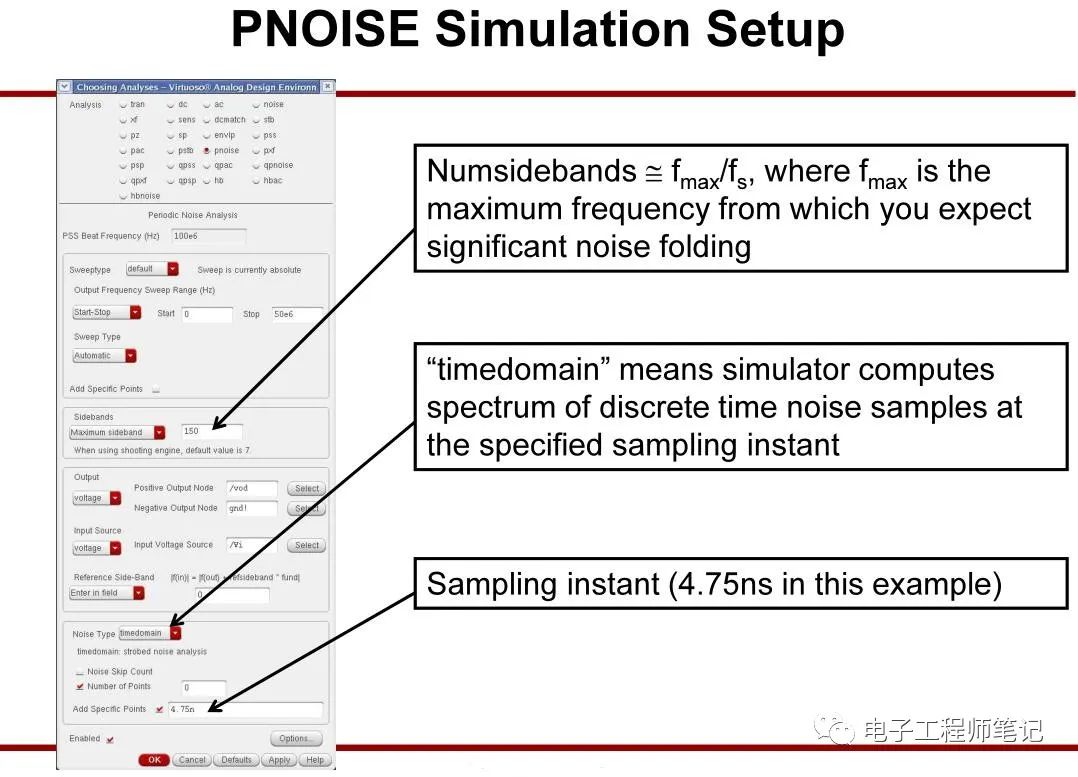

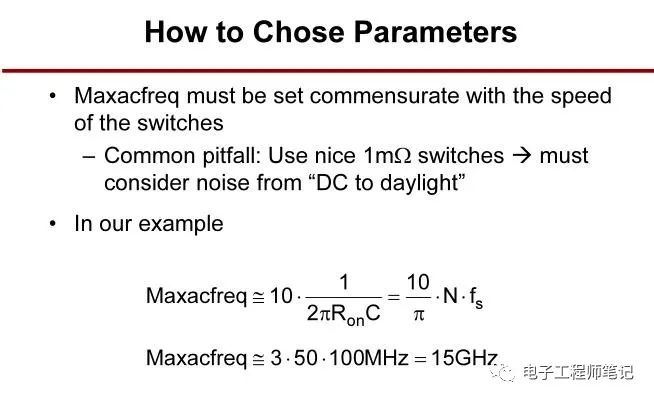

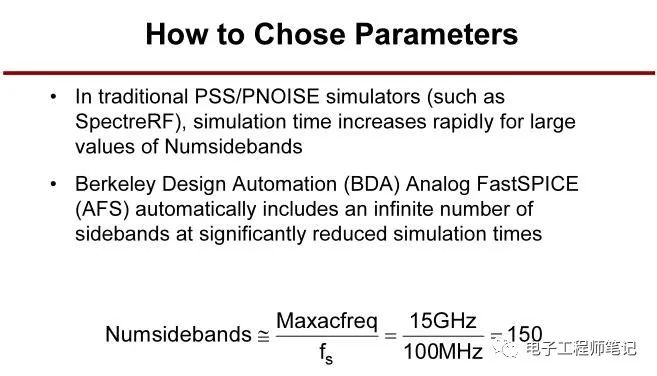

5.2 周期穩(wěn)態(tài)仿真

?

?

?

?

?

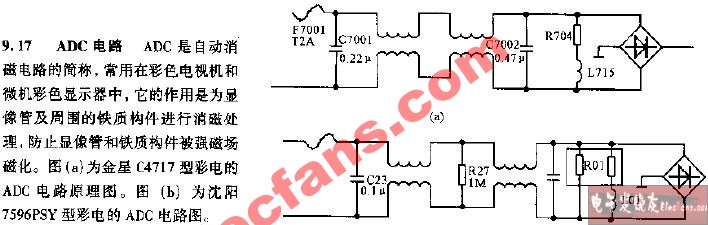

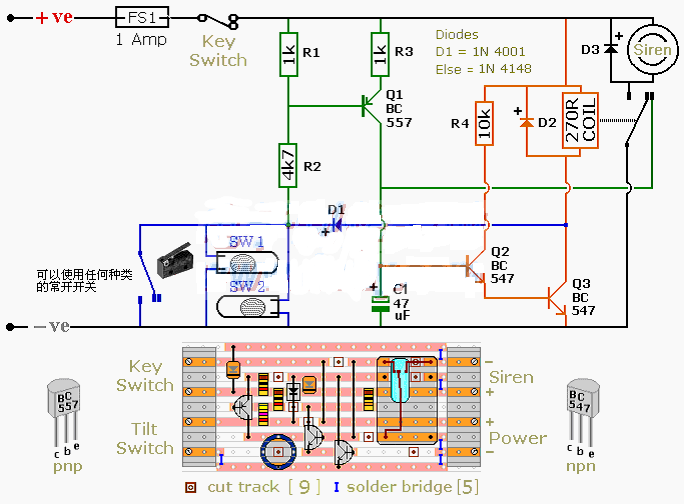

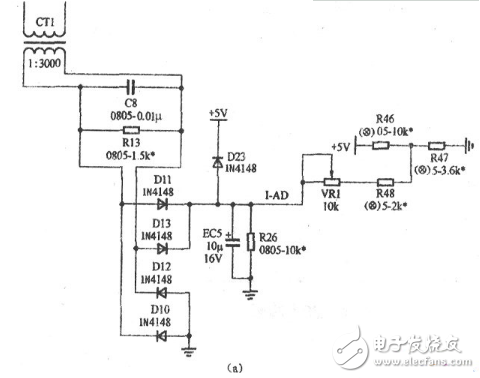

低功耗電池電壓ADC采樣電路,墨水屏通電掉電控制電路,PMOS電子開(kāi)關(guān),可用于待機(jī)低功耗的項(xiàng)目

推薦閱讀

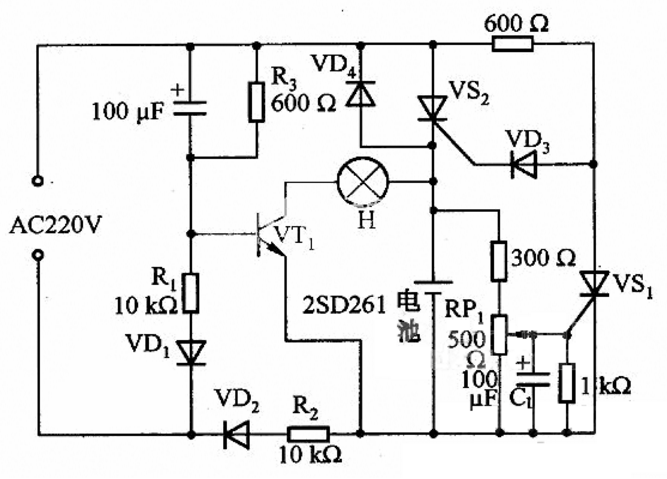

如何用電路實(shí)現(xiàn)檢測(cè)過(guò)零點(diǎn)?這個(gè)簡(jiǎn)單電路就能搞定

?

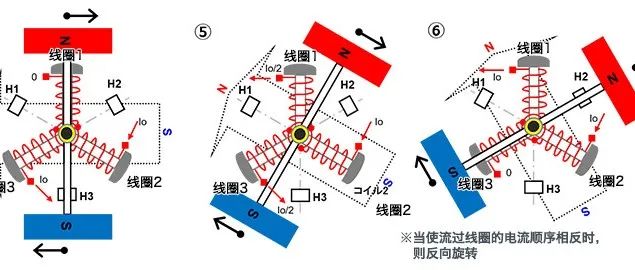

電機(jī)就是這樣轉(zhuǎn)起來(lái)的~

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論