概念

MOSFET釋義:

MOSFET即金屬-氧化物-半導體場效應晶體管,其全稱為METAL-OXIDE-SEMICONDUCTOR FIELD EFFECT TRANSISTOR,顧名思義,是利用電場效應去感應電荷的晶體管,它利用柵極電壓去感應出反型層溝道,從而使電荷能夠在溝道中移動,即“導通”。

MOSFET工作原理:

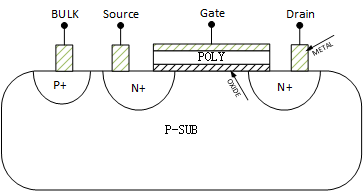

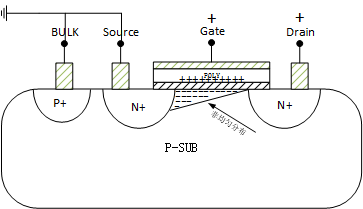

MOS管的工作原理用其剖面圖來解釋最為直觀。

上圖為N型MOS管的剖面圖,可以看出這是一個四端器件,分別由柵極GATE,源極SOURCE,漏極DRAIN和體端BULK構成,其結構也比較簡單,在P型襯底上通過離子注入等方法產生兩個N阱,分別作為源極和漏極,上面再覆蓋一層氧化層作為絕緣層,再通過腐蝕等方法將部分氧化層去除后在源極、漏極、柵極上墊積金屬。

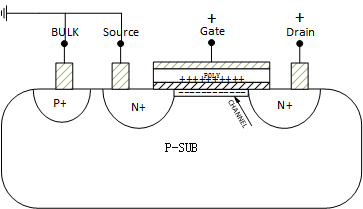

柵極和襯底由于絕緣層的存在而構成了柵極電容,在柵極未加正電壓時,MOS管處于斷開狀態,即使源極和漏極之間存在壓差,它們之間依然無電流流過; 當柵極加上正電壓后,柵極電容上極板正電荷往下跑,下極板負電荷往上跑,而絕緣層的存在阻隔了這個行動,因此上極板累積正電荷,下極板感應出同樣數量的負電荷,這些負電荷在源漏之間形成了一層耗盡區; 隨著柵極電壓的上升,源漏之間的負電荷累積得越來越多,當其濃度大于等于P襯底的摻雜濃度時,耗盡區就轉變成了反型區,源漏之間能夠通過反型層連接。 這個能夠在產生反型層溝道的臨界電壓就是該MOS管的閾值電壓(VTH); 以上描述針對的是N型MOS管,對于P型MOS管,襯底為N型,柵極電壓應低于源極電壓。 此時,若在源漏之間存在一定壓差,就會有電流流過。

由于MOS管結構上的對稱性,原則上其沒有固定的源極和漏極,但對于P型MOS管來說,電流流入的一端為源極,電流流出的一端為漏極,襯底接電源; 對于N型MOS管來說,電流流入的一端為漏極,電流流出的一端為源極,襯底接地。 下面繼續以N型MOS管為例進行分析。

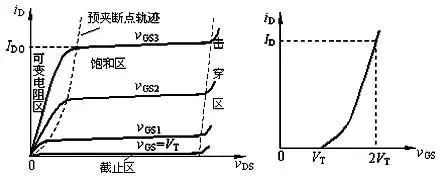

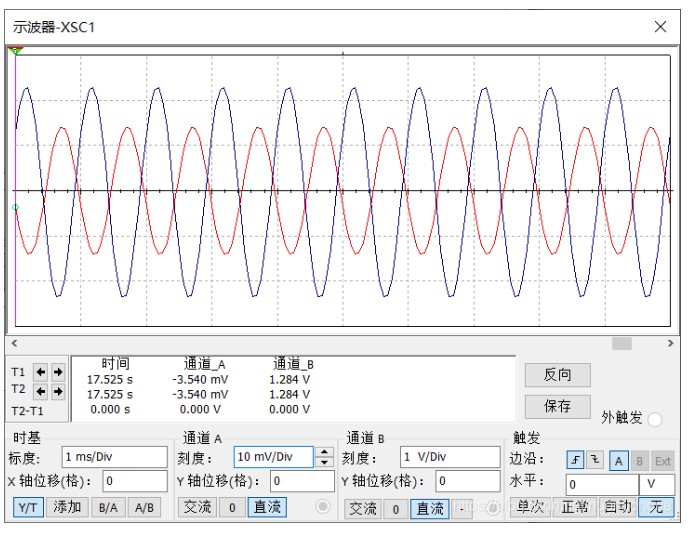

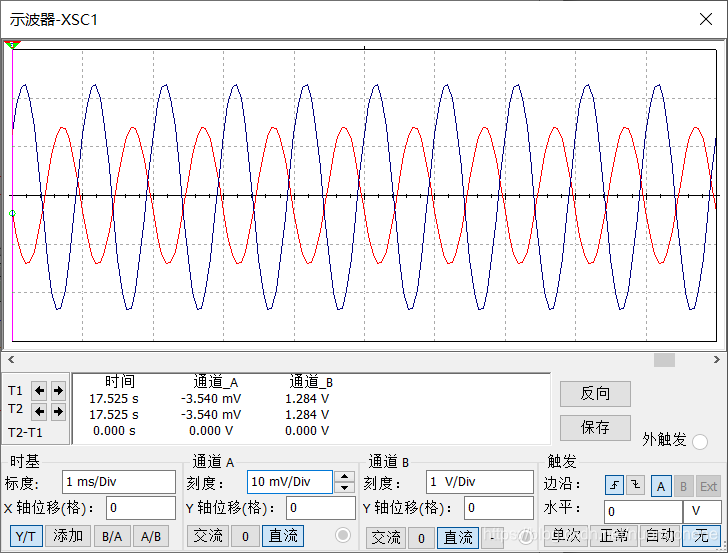

左圖為在不同柵源電壓VGS下,漏源電流iDS隨漏源電壓VDS變化的曲線圖;右圖為漏源電流iDS隨柵源電壓VGS變化的曲線圖,此時漏源電壓VDS為定值。從圖中可以發現如下幾個特性:

①當VGS較小時,MOS管處于截止區,無電流流過;

②iDS隨VDS的增大先線性上升(線性區),再趨于平緩(飽和區);

③iDS隨VGS的增大呈平方律上升;

下面對上述特性依次分析,讓大家對MOS管有一個更全面的認識。首先是截止區,器件工作在截止區的主要原因是柵極電壓太小了,還沒能把柵極下方的耗盡區轉換成反型區,也就是說源漏之間還是斷開的,這就不可能有電流流過了。

隨著柵極電壓的上升,當VGS電壓到達閾值電壓時,耗盡區終于變為反型區,源漏通過溝道連起來了,這時如果VDS還不大,器件就工作在線性區,如下圖所示。

可以看出反型層是均勻分布的,均勻分布的反型層可以看作均勻電阻,從源極到漏極流過的電流是接近線性的,因此線性區又叫做可變電阻區,電阻的大小和VGS電壓有關。

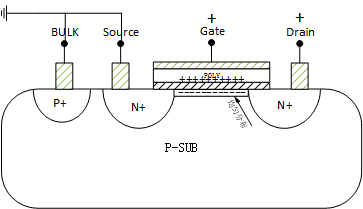

但隨著VDS電壓的增大,由于柵極和源極之間的壓差會大于柵極和漏極之間的壓差,因此反型層就會變得不均勻,如下圖所示。

非均勻分布的反型層,就讓器件慢慢進入了飽和區,因為隨著VDS電壓的上升,柵極和漏極之間就會因為壓差的逐漸減小,而從反型區回到耗盡區,從而出現一個新的狀態——夾斷。夾斷的出現正是保證電流恒定和區的關鍵,因為漏極電壓過大而產生的耗盡區實際上是一個大電阻,此后VDS增加的電壓都會分到這個大電阻上而不是反型層上,因此可以認為反型層上出現了恒壓的狀態,IDS電流也就基本恒定了。

此處插入一條公式:IDS=1/2*K'W/L(VGS-VTH)2,此處k'為工藝因子。

下面就可以根據上述過程推出MOS管進入飽和區的條件了,即VDG≤VTH,其中VGD為柵極和漏極的壓差,VTH為MOS管開啟的閾值電壓,當VDG≤VTH器件就會出現夾斷,也就是進入恒流的標志。將VDG≤VTH進行分解,就可以得到一個很經典的MOS管進入飽和區的條件公式:VDS>VGS-VTH。

那么,眼尖的童鞋們就會發現了,上面的ID/VDS圖中,當MOS管進入飽和區后,電流并不是一條平的直線,還是微微上升的呀!這時候就需要給大家帶來今天的第一個著名效應了,那就是溝道調制效應,溝道調制效應讓進入飽和區的IDS電流受VDS影響而變得不恒流。隨著VDS電壓的上升,耗盡區其實是不斷擴大的,這就讓反型層的實際長度變短了,畢竟器件的溝道長度也就只有L那么長。因此,為了讓器件的恒流做的更好,會考慮把MOS管的溝道長度L做長些,這樣耗盡區變長帶來的影響就會減小了。

此處插入一條公式:

IDS=1/2K'(VGS-VTH)2W/[L(1-λVDS)]

=1/2K'W/L(VGS-VTH)2(1+λVDS)

=1/2K'W/L(VGS-VTH)2(1+VDS/VA),此處VA為著名的厄利電壓,VA越大說明器件的恒流特性越好。

除了溝道調制效應,還有一個很出名的效應就是——襯底偏置效應,這個效應是說假設襯底和源極不是一個電位的,這個狀態是很容易出現的,因為通常同一工藝中器件的襯底都是接一塊的,比如一般NMOS管的襯底都接在地上,這時如果源極電位比襯底電位高的話,源極和襯底首先就反偏了,在溝道里先感應了點負電荷; 我們上面也說過,柵極和襯底構成了柵電容,下極板先感應了負電荷,那上極板需要感應相應的正電荷才行,因此襯底偏置效應會讓閾值電壓變高,也就是需要更大的VGS電壓才能讓MOS管開啟。

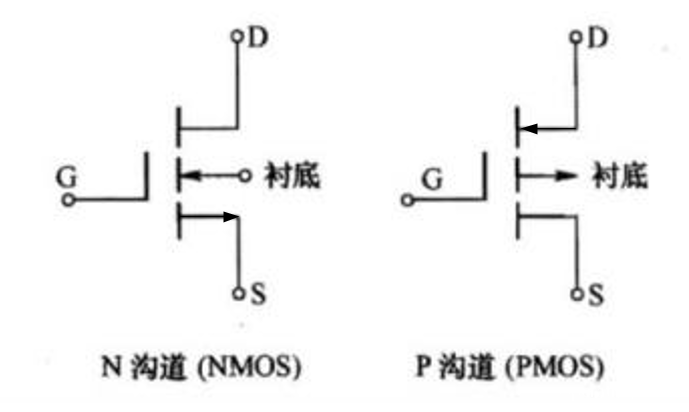

最后我們來看看NMOS和PMOS的符號吧。

還有一種柵極畫圈圈的我就不畫了,圈圈代表低電平有效,柵極有圈圈的是PMOS,柵極沒有圈圈的是NMOS。

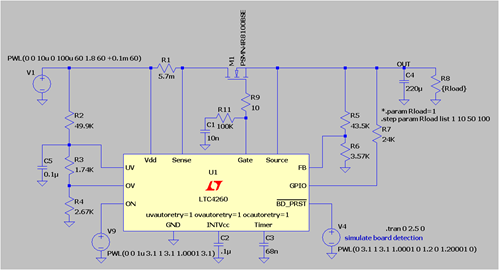

電子發燒友App

電子發燒友App

評論