非線性特性有關。以下將重點分析由電源、外部基準源、數字連接、外部干擾等造成的固定頻率雜散。根據應用情況,可降低或完全避免這些類型的雜散,以助于實現最佳的信號鏈性能。 由ADC周圍DC-DC電源而導致的雜散

2019-02-14 14:18:45

雜散測試線損問題? 有的時候是一個范圍,怎么確定線損呢?

2020-05-08 05:55:31

雜散測試線損問題? 有的時候測得是一個范圍,怎么確定線損呢?

2016-09-11 23:41:06

之一。確保設計出低損耗、高能效產品的另一個重要因素是功率半導體的開關速度,而開關速度受不同逆變器解決方案的雜散電感影響。IGBT技術不能落后于應用要求。因此英飛凌推出幾款最新的IGBT芯片,以滿足具體

2018-12-10 10:07:35

惱人的雜散問題怎么破?雜散來源如何確定?...請參考本帖中列舉的相關實戰問題!在此版主將整理發布有關雜散的一問一答專題帖,將理論聯系到實際應用總結出可行方案!包括AD9914、HMC833...當然

2019-01-16 12:27:07

惱人的雜散問題怎么破?雜散來源如何確定?...請參考本帖中列舉的相關實戰問題!在此版主將整理發布有關雜散的一問一答專題帖,將理論聯系到實際應用總結出可行方案!當然鼓勵跟帖向大家分享你的實戰經驗~Q

2017-04-27 15:58:16

出現一個與基帶信號相關的雜散點幅度-50dBm左右,影響了射頻輸出的Sfdr。具體現象:

輸出2.2ghz點頻時,雜散點在2.6GHz

輸出2.3ghz點頻時,雜散在2.5ghz

輸出2.4ghz點頻

2023-12-04 07:39:16

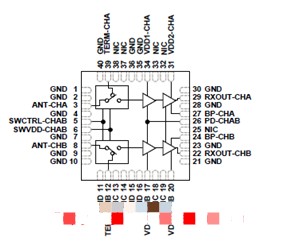

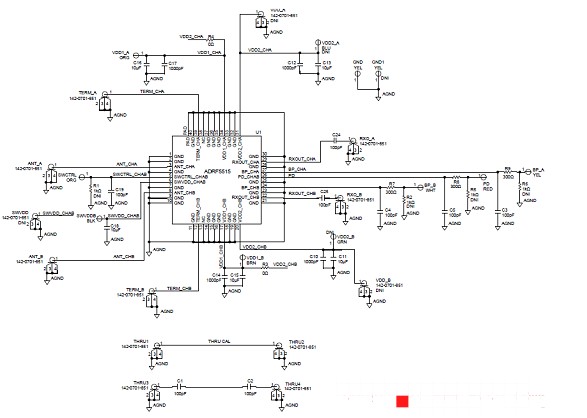

我們準備把AD9361用于TDD系統,但由于時延等問題,想把9361配置成FDD模式,通過外部的開關實現TDD切換;需要了解一下FDD模式下TX通道的雜散/噪底等情況,以便設計開關的收發隔離;1

2018-12-27 09:24:47

的是載波信號,2.5Ghz,如圖,頻譜很好,我用DDS產生一個500K的單音信號,理論上出來是2.5G偏移500K的單音信號,用頻譜測得確實輸出了2.5G偏移500K的信號,但是周圍還有很多雜散,不知道

2018-08-27 11:51:16

各位大牛,請教一下。我現在用AD9467-250,采樣時鐘用AD9517-3出的200MHz,采集70M、0dBm單音信號。頻譜上出現較多的雜散。ADC前端電路按照AD9467手冊推薦的設計。ADC

2019-01-25 08:21:14

各位大牛,請教一下。我現在用AD9467-250,采樣時鐘用AD9517-3出的200MHz,采集70M、0dBm單音信號。頻譜上出現較多的雜散。ADC前端電路按照AD9467手冊推薦的設計。ADC

2023-12-08 06:52:03

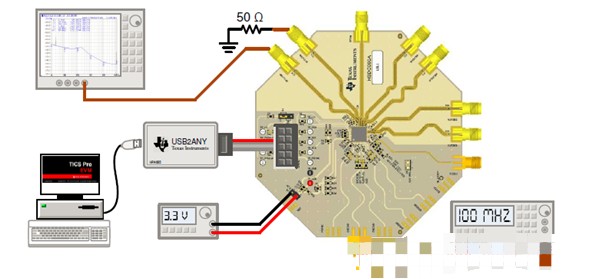

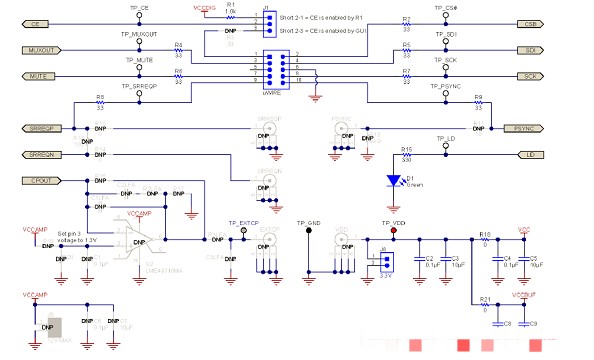

近日通過多次測試,發現AD9912的DAC輸出端雜散比較大。望幫忙分析分析 環境條件如下:1、3.3v,1.8v均為LDO電源供電;原理圖參考的是官方提供的文件。2、外部1G時鐘輸入,旁路內部PLL

2019-03-08 15:14:23

參考輸入為245.76MHz/0dBm,輸出61.44MHz附近給鎖相環做參考,可是輸出一直有雜散。我改用信號源直接給鎖相環提供參考就沒有雜散了,所以推斷出是AD9912引入的雜散。我同事他也用

2018-12-25 11:41:21

,85Hz和110Hz及其N次諧波的雜散。時鐘采用400MHz,對時鐘的實現是100MHz晶振通過放大器飽和區取出4次諧波,通過聲表濾波器和放大器,對400MHz進行放大濾波處理。不知道這種時鐘的實現有沒有問題?時鐘的功率肯定夠。求解?

2019-02-22 08:27:59

我使用ADF4351,其輸出在中心頻率偏移184k附近有雜散輸出,通過減小環路帶寬,減小充電電流等,雜散有一定的降低, 此時帶來靠近中心頻率出的噪聲升高,通過對比不同的板卡,都存在類似的現象,環路

2018-10-12 09:24:23

鎖定,置940M頻率產生920M頻率左右波動,960M在940M左右,而且周圍每10M有很高的雜散,請問我該怎么解決,大概問題出在哪里

2019-01-16 08:17:56

/10?現在計算到小數部分([size=13.3333330154419px]分子/2^24)在0.05至0.2之間,其最差雜散能測到多少?PFD在50MHz和100MHz間選擇。

2019-02-26 13:56:03

我用cc1120實現頻分復用,現在發現存在雜散現象,尤其是2個以上不同信道一起發射時,他們的雜散疊加導致其他信道被污染,請問這種情況有解決方法么

2018-06-24 03:14:54

是90度,即360度的1/4。這樣的頻譜會多出一根雜散信號,如果延遲匹配寄存器位不設置為1,就會有兩根,雜散而且是有規律的,想請問一下這種現像是不是正常現像,可否解決,用MATLAB仿真的時候看不到這根雜散信號。

2018-08-30 11:49:24

本帖最后由 EMChenry 于 2015-8-6 10:17 編輯

EMC案例之輻射雜散測試

2015-08-06 10:15:32

在使用HMC704中遇到非整數邊界雜散問題,麻煩各位看看: REFin:100MHz, N=2, 鑒相頻率50MHz輸出分別為10025MHz,10050MHz和10075MHz環路濾波器帶寬:1

2019-02-21 14:05:56

,即N為整數,則鑒相頻率PFD=fvco/N,算出鑒相頻率后AD9912再輸出這個頻率送至HMC的參考輸入腳,鑒相頻率范圍為68MHz~72MHz,環路帶寬為手冊上推薦的90KHz,當輸出頻率變化小于

2019-02-22 12:27:30

偏離10KHz,如此近的一個頻率偏移導致的結果就是整數邊界雜散IBS(此處為5000MHz和5000.02MHz)異常大,接近-40dBc。所以我想請教的就是如何通過合理的設置各寄存器各參數(如果有

2018-09-04 11:35:47

3GPP TS 36.104以Band40為例,基于傳統的共址雜散測試方案,探討了一種新型的共址雜散測試方案,采用了雙工器和低噪放相結合的方法。在此方案中,雙工器的主要作用是將載波信號和雜散發

2020-12-03 15:58:08

每隔3KHz存在雜散,無法通過降低信號功率,改變時鐘數據相位來改善

更改參考時鐘為60MHz,雜散間隔變為15K

更改參考時鐘為20MHz是,雜散消失

請問各位大神這個問題應該怎么考慮,謝謝

另外當去掉DAC輸出輔助之后用示波器測試波形如下,這種現象是信號發生反射了嗎?

2023-12-07 07:09:55

(并且在大多數情況下消除)整數邊界雜散。前文提到整數邊界雜散發生在PFD頻率的整數倍之處,并且在靠近載波頻率時最大。如果可以改變PFD頻率,使PFD頻率的整數倍落在足夠大的載波頻率偏移頻率處,那么IBS功率

2019-10-11 08:30:00

于相位噪聲、鎖定時間或雜散卻并非如此。表1給出了環路帶寬對這些性能指標的影響的大致參考。 性能指標最優帶寬備注抖動BWJIT最優值一般為BWJIT。在低集成限制更高的一些情況下,有時較窄的環路帶寬實際上效果更好。鎖定時間無限VCO鎖定時間隨著環路帶寬的增加而提高,但有時會受到VCO校準時間…

2022-11-16 07:56:45

,也就是說,一個發射系統要實現雜散信號的在線(不中斷通信)測試,從技術上幾乎是不可實現的,必須斷開主饋線,串入測試系統(見下圖),這樣才能準確測量標準中所規定的全頻段雜散輻射。蜂窩基站雜散的正確接入點

2017-11-15 10:35:09

整數邊界雜散不受歡迎的原因有哪些?如何改變PFD頻率?怎樣將ADIsimFrequencyPlanner應用到寬帶VCO里?

2021-04-12 06:28:29

小數分頻器整數邊界雜散問題的提出小數分頻器整數邊界雜散的優化設計

2021-04-19 08:32:15

DDS的工作原理是什么?如何抑制DDS輸出信號中雜散問題?

2021-05-26 07:15:37

如何滿足高性能基站(BTS)接收機對半中頻雜散指標的要求?為達到這一目標,工程師必須理解混頻器的IP2與二階響應之間的關系,然后選擇滿足系統級聯要求的RF混頻器。混頻器數據手冊以二階交調點(IP2)或2x2雜散抑制指標的形式表示二階響應性能。

2019-08-21 07:53:30

,相干雜散就是有射頻信號輸入時的雜散信號,非相干雜散就是沒有射頻信號輸入時的雜散信號。檢測的信號鏈路大體是:信號發生器-->X低噪放-->下變頻-->中頻開關-->頻譜儀。鏈路

2019-11-14 10:59:39

圖2中,同一100 KHz音以完全相同的頻率偏移傳輸到DDS/DAC輸出,不受調諧字頻率影響。圖2中的頻率調諧字表現出四個相互疊加的不同DDS載波。注意,在全部四個載波改變時,參考時鐘雜散的頻率

2023-12-15 07:38:37

如何滿足高性能基站(BTS)接收機對半中頻雜散指標的要求?為達到這一目標,工程師必須理解混頻器的IP2與二階響應之間的關系,然后選擇滿足系統級聯要求的RF混頻器。混頻器數據手冊以二階交調點(IP2)或2x2雜散抑制指標的形式表示二階響應性能。

2019-08-30 07:53:12

DDS的工作原理是什么如何降低輸出信號雜散電平?DDS作為分頻器在鎖相環中的應用研究

2021-04-22 06:09:32

將不同通道的LO頻率設置為相同的頻率時,雜散頻率也處于相同的頻率,如圖3a所示。圖3b所示為LO2的設置頻率高于LO1的情況。數字NCO同等地偏移,使RF信號實現相干增益。鏡像和三次諧波失真積處于

2021-05-08 07:30:00

邊帶雜散,其頻率偏移等于參考時鐘頻率。參考時鐘源雜散圖1所示為DDS的500 MHz參考時鐘,由一個100 KHz音實現10%的AM調制。該參考時鐘源是一款Rohde andSchwartz具有調制

2018-11-01 11:24:06

雜散測試的一些資料,期刊論文,有需要的朋友自行下載吧

2018-09-26 10:15:21

例如,若是鑒相器頻率為100MHz,輸出頻率為2001MHz,那么整數邊界雜散將為1MHz的偏移量。在這種情況下,1MHz還是可以容忍的。但當偏移量變得過小,卻仍為非零值時,分數雜散情況會更加嚴重

2022-11-18 07:51:05

當偏移量變得過小,卻仍為非零值時,分數雜散情況會更加嚴重。 采用可編程輸入倍頻法來減少整數邊界雜散可編程倍頻器的理念是讓鑒相器頻率發生位移,這樣壓控振蕩器(VCO)頻率就能遠離整數邊界。考慮一下用

2018-09-06 15:11:00

隨著5G時代的推進,智能終端產品作為寬帶射頻應用最大的消費市場面臨著一系列開發與驗證的問題。其中,越來越小的設計空間與電磁輻射雜散性能之間的矛盾,將是商業研究人員開發和驗證中面臨的巨大挑戰。若要

2019-06-10 06:38:45

傳導和輻射雜散的FCC限值是什么情況,沒看懂,求指點。另外,2G和3G的雜散測試,除了測試頻率范圍不同外,還有哪些不同,提前謝謝大神!!!!!!!

2013-03-10 21:38:03

小弟正在調試一款X波段(9.6-10.8GHz)的鎖相環,采用的是內部集成VCO的HMC778LP6CE芯片。在調試中,我發現在距中心頻率50Hz整數倍的頻率處有很多雜散,請問各位大神這些雜散

2014-07-21 15:47:54

要求的不同,有多種處理此類問題信號的方法。謹慎的頻率規劃和濾波雖然能夠有助于大幅度減少雜散脈沖的數量,但是它們總是會有。因此,系統設計師必需在混頻器輸出端上準確地測量雜散電平,以確定怎樣用最佳的方式應對它們,這一點是很重要。

2019-07-23 08:17:34

。(2)電氣判斷法由于雜散電流難以直接測量,所以對于管道是否受到雜散電流影響,目前通常是按管地電位較自然電位正向偏移值來判斷,如果管地電位較自然電位正向偏移值難以測量時,可采用土壤電位梯度來判定雜散電流

2020-12-01 16:22:35

至19位(MSB)。 當DDS頻率調諧字發生變化時,相對基波(載波)的頻率偏移不發生改變的雜散一般分為兩類:要么以某種方式耦合至DDS電源;要么是驅動DDS的參考時鐘源上的一個元件。 注意,如果

2018-08-27 11:34:36

ADC內核可以并行工作,從而實現高于單核的采樣速率。然而,每個這些內核的輸入端之間都存在相位、失調、增益和帶寬微小差異。結果,新的交錯偽像和圖像雜散可能進入頻譜中,從而導致ADC寬帶SFDR下降。這會減小

2018-11-01 11:31:37

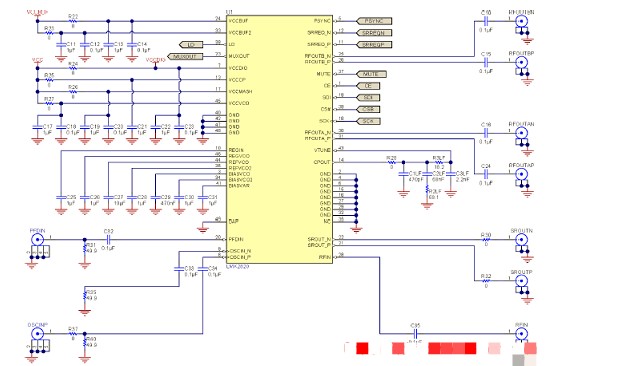

最近使用AD9910時發現,在960MHz時鐘下。AD9910輸出300MHz、290MHz和302MHz(均為單音模式),3個點頻信號。其中300MHz信號在100MHz頻寬內雜散較好,基本都在

2018-11-29 09:49:07

貴公司的專家們好,我最近在做的項目使用的AD9914芯片,芯片使用3.2GHz參考時鐘,DDS輸出950MHz信號時150MHz,200MHz,處有-65dBc左右的雜散,300MHz處有

2018-11-13 09:35:04

ADF4351輸出,相噪遠不及器件參考值理想。而且在離中心頻率最近處的雜散出現在偏離中心頻率5KHz的地方。從頻譜來分析,我估計如果能減小或者消除該雜散,則相噪應該可以明顯變好。電源我采用了兩顆

2018-09-29 15:40:47

ADF4355,采用100MHz OCXO作為參考,輸出2280MHz,鑒相頻率100MHz,近端出現70Hz左右(及其倍數)的雜散,抑制度在47dBc左右,CP電流設置0.3mA,調整Bleed

2018-08-22 10:40:08

您好,請問我在做ADF4356鎖相環時發現在PFD諧波處有較強雜散,高達-75dBc,可以看成就是整數邊界雜散,但是雜散距離中心頻率已經有了15M左右,環路帶寬40KHz,請問一下這是什么原因導致

2019-02-15 13:26:51

如圖,這是數據手冊上說的HMC833參考為50MHz輸出為5900.8Mhz時的雜散情況。圖上頻偏頻偏為400KHz和800Khz的地方都有雜散。根據數據手冊上的理論,我能理解800Khz處的雜散是整數邊界雜散,但我沒弄懂400Khz處的雜散緣由?哪位明白的,可以解釋一下?謝謝

2018-10-09 17:57:58

HMC833低雜散(1)HMC833是否有低雜散模式。(2)改變seed in fraction是否有作用?

2019-01-15 08:42:05

,參考源用50M,如果發送頻率是50M的整數倍,如3.9G時,雜散指標很好,可達60dB以上,而發送頻率為3.9001G時,就會在100K或200K或300K處出現雜散,有時只有40dBc不到,當頻率偏移50M整數倍更多,超出環路濾波器帶寬時,又會變小。請問這是AD9361的指標水平嗎?

2018-08-23 07:15:55

各位好我在看模擬對話的時候,看到邊帶雜散和開關雜散不太明白,請問大家這其中的含義以及它將導致什么后果?謝謝大家了!!!

2019-01-09 09:29:01

而言是最優的,但對于相位噪聲、鎖定時間或雜散卻并非如此。表1給出了環路帶寬對這些性能指標的影響的大致參考。 性能指標最優帶寬備注抖動BWJIT最優值一般為BWJIT。在低集成限制更高的一些情況下,有時

2018-08-29 16:02:55

Hello! 請教個關于鑒相頻率雜散與環路濾波器布線的問題。例如ADF4360,鑒相頻率的雜散抑制的典型值為-70dBc左右,而實測為-60~-65dBc,也能接受,只是感覺各次倍頻的鑒相頻率太多

2018-11-07 09:03:01

一例。其他PLL/VCO器件需要采取一些額外措施來改善雜散水平,以便支持某些高性能產品。改變PFD頻率以消除整數邊界雜散一種技術是利用頻率規劃算法改變PLL的PFD頻率。這樣可以將PFD模塊引起的雜散

2018-10-17 10:49:00

最近調試遇到個問題,40W功放輸出功率時在225K左右會有雜散,抑制在-50dB左右,初步認為是由于風扇引起的,如過是風扇引起的話,該如何解決

2014-03-28 09:58:41

雖然目前的高分辨率SAR ADC和Σ-Δ ADC可提供高分辨率和低噪聲,但系統設計師們可能難以實現數據手冊上的額定SNR性能。而要達到最佳SFDR,也就是在系統信號鏈中實現無雜散的干凈噪底,可能就更加困難了。雜散信號可能源于ADC周圍的不合理電路,也有可能是因惡劣工作環境下出現的外部干擾而導致。

2019-08-12 06:51:54

降低或完全避免這些類型的雜散,以助于實現最佳的信號鏈性能。由ADC周圍DC-DC電源而導致的雜散問題由于DC-DC開關穩壓器會產生較高的紋波噪聲,通常建議將LDO作為在精密測量系統中為精密ADC生成

2018-10-19 10:38:17

電子發燒友App

電子發燒友App

評論