注意:Maxim提供各種精度的電流輸出DAC。本文中,將以MAX5891 作為測(cè)量和規(guī)格說明的特例。但所介紹的參數(shù)和測(cè)量方法可以用于其他的差分輸出、電流模式DAC。

線性參數(shù)說明

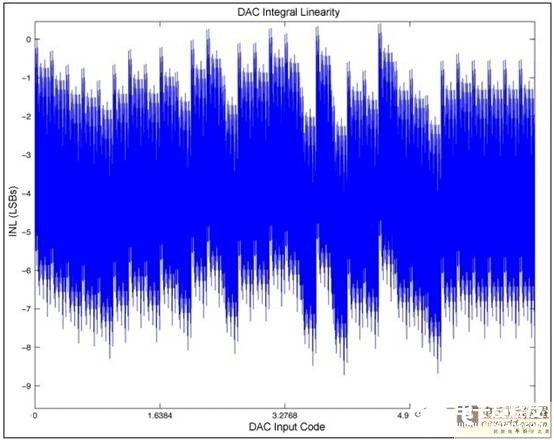

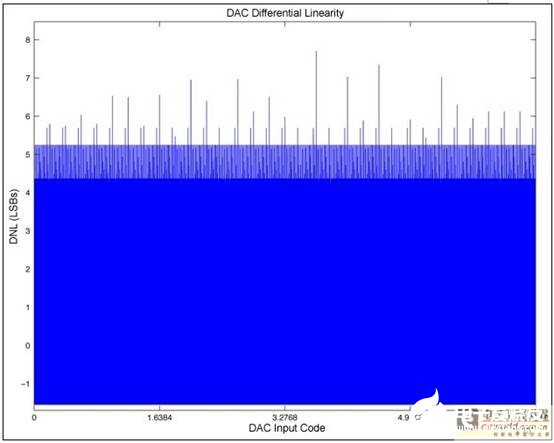

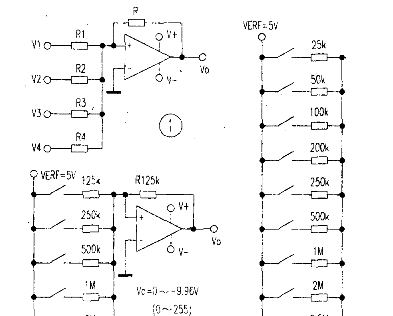

定義數(shù)據(jù)轉(zhuǎn)換器線性精度主要有兩個(gè)參數(shù):積分(INL)和差分(DNL)非線性。INL是輸出傳輸函數(shù)和理想直線之間的偏差;DNL是轉(zhuǎn)換器輸出步長(zhǎng)相對(duì)于理想步長(zhǎng)的誤差。

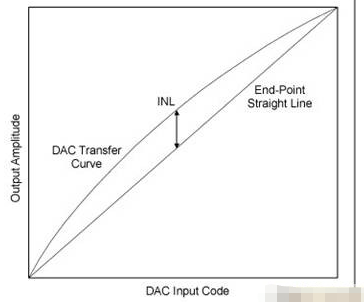

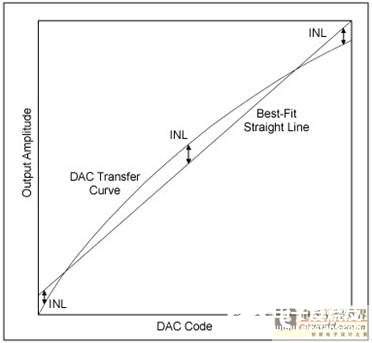

可以采用兩種方法之一對(duì)INL進(jìn)行定義:(1)端點(diǎn)INL或(2)最佳擬合INL。端點(diǎn)INL是采用DAC傳輸函數(shù)端點(diǎn)測(cè)得的實(shí)際值計(jì)算轉(zhuǎn)換器的線性度;最佳擬合INL則是計(jì)算傳輸函數(shù)的斜率獲得INL的峰值。

圖1a. 端點(diǎn)積分非線性誤差

圖1b. 最佳擬合積分非線性誤差

圖1a和圖1b以圖形的形式顯示了兩種測(cè)試方法與給定傳輸函數(shù)之間的關(guān)系。注意,兩種情況中,DAC傳輸函數(shù)曲線的數(shù)值和形狀都一樣。還要注意,圖1a的端點(diǎn)線性度有較大的正INL,而沒有負(fù)誤差。

采用圖1b所示的最佳擬合方法,將部分正誤差轉(zhuǎn)移到直線的負(fù)側(cè),以降低報(bào)告的最大INL。注意,線性度誤差總量和直線計(jì)算結(jié)果相同。

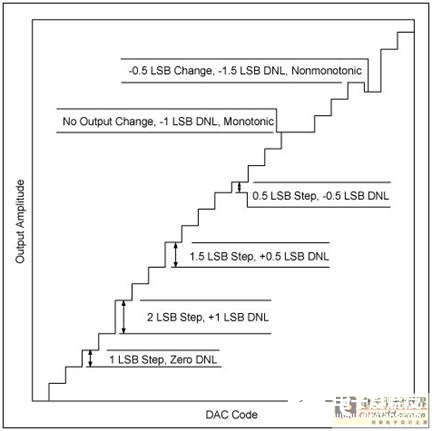

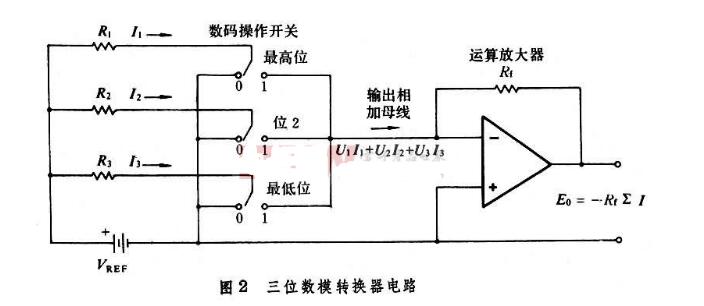

DNL定義理解起來要難一些,確定最低有效位(LSB)的權(quán)值會(huì)影響DNL。DAC中需要考慮DNL沒有小于-1 LSB的編碼。小于這一電平的DNL誤差表明器件是非單調(diào)的。當(dāng)輸出不隨輸入碼增大而減小時(shí),或者輸出不隨輸入碼減小而增大時(shí),DAC是單調(diào)的。圖2解釋了正、負(fù)DNL誤差,澄清了單調(diào)的概念。

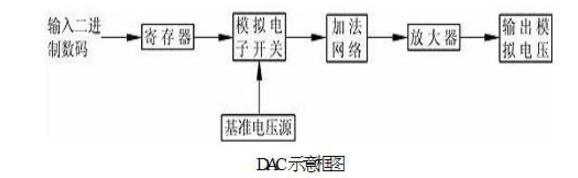

測(cè)量線性度所采用的方法需要考慮待*估DAC的體系結(jié)構(gòu)。優(yōu)先選擇將電流模式DAC輸出轉(zhuǎn)換為電壓,因?yàn)檫@樣可以使用電壓表而不是電流表。普通的萬用表在測(cè)量電壓時(shí)分辨率要高于電流測(cè)量。電流源的配置決定了需要測(cè)量多少位編碼才能對(duì)器件性能進(jìn)行精確的*估。

圖2. DNL誤差實(shí)例

有很多方法可以將電流(I)轉(zhuǎn)換為電壓(V),主要取決于幾種因素。首先考慮使用萬用表進(jìn)行測(cè)量,能夠得到的最高分辨率決定了精確測(cè)量的最小LSB權(quán)重。推薦LSB權(quán)重與儀表分辨率的比是100比1;儀表應(yīng)能夠測(cè)量LSB的1/100。

待測(cè)DAC的輸出額定容限也影響了如何進(jìn)行I至V的轉(zhuǎn)換。電流模式DAC輸出容限是指器件在輸出上能夠承受多大的電壓而不會(huì)對(duì)性能有影響。增大負(fù)載電阻會(huì)提高電壓擺幅和LSB的大小,但是容限限制了最大負(fù)載。

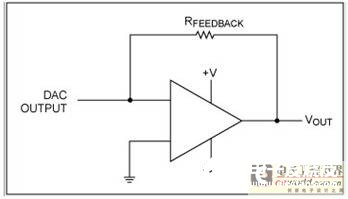

替代簡(jiǎn)單的電阻轉(zhuǎn)換的方法是使用虛擬地配置的運(yùn)算放大器,如圖3所示。由于DAC輸出電壓保持為零,這種配置的優(yōu)勢(shì)是能夠提高LSB的大小,明顯高于容限限制。然而,放大器容限和線性度以及熱梯度會(huì)影響測(cè)量。同樣的,需要兩個(gè)匹配放大器來測(cè)量差分輸出器件。

圖3. 虛擬地的I至V轉(zhuǎn)換

測(cè)量線性度時(shí)需要考慮的另一因素是待*估DAC的分辨率。器件分辨率越高,LSB越小。考慮MAX5891 (16位)、MAX5890 (14位)、MAX5889 (12位)器件。每一器件的滿量程輸出為20mA。使用50Ω負(fù)載時(shí),相應(yīng)的LSB大小為15.25?V、61.04?V和244.2?V。LSB越小,萬用表需要的精度和分辨率就越高。

考慮到DAC的分辨率,還應(yīng)該確定需要多少位編碼才能精確地測(cè)量器件性能。16位器件有65,536個(gè)可能的輸入編碼,12位器件有4,096個(gè)。由于不可能人工測(cè)量所有這些編碼,因此,常用的方法是測(cè)量編碼子集。少量的編碼減少了采集數(shù)據(jù)所需要的時(shí)間,并且能夠提供非常精確的結(jié)果。掌握器件的體系結(jié)構(gòu)有助于選擇某一器件的最佳編碼。

測(cè)量電流輸出器件的線性度時(shí),溫度效應(yīng)比較明顯。輸出負(fù)載電阻的功耗導(dǎo)致發(fā)熱,從而改變了電阻值(除非采用的電阻具有0ppm溫度系數(shù))。解決這一問題的方法是轉(zhuǎn)換輸入編碼,有效地對(duì)負(fù)載功耗進(jìn)行平均。

這里采用的方法非常適合自動(dòng)測(cè)量,因?yàn)樗軌驕p小所有編碼的延遲時(shí)間。測(cè)量每一編碼及其補(bǔ)碼,例如0x4800,然后是0xB7FF。通過測(cè)量每一編碼及其補(bǔ)碼,負(fù)載平均功率保持固定,這是因?yàn)椴捎昧藦牧愕綕M量程遞增的方式來測(cè)量最高有效位(MSB)輸入。由于在量程中部測(cè)量LSB,該方法不太適合,因?yàn)楣β实淖兓喈?dāng)小。

測(cè)量說明

以下是Maxim開發(fā)的幾種器件所采用的線性度測(cè)量方法。MAX5873 、MAX5875 、MAX5885、MAX5888 MAX5891、MAX5895 和MAX5898 /都采用了該方法進(jìn)行測(cè)量。在最初設(shè)計(jì)*估和產(chǎn)品測(cè)試時(shí)進(jìn)行了實(shí)驗(yàn)室測(cè)量。雖然下面實(shí)例針對(duì)MAX5891,該方法也可以用于其他器件。

MAX5891采用了5-4-3-4分段結(jié)構(gòu)。分段是指將一個(gè)16位器件有效地分成四個(gè)單獨(dú)的DAC,一個(gè)5位、一個(gè)4位、一個(gè)3位和第二個(gè)4位器件。5個(gè)MSB含有31個(gè)(25 - 1)等權(quán)重電流源,對(duì)于5位分辨率,每個(gè)輸入編碼采用一個(gè)等權(quán)重電流源。下一個(gè)4位使用15個(gè)源,再下一個(gè)3位使用7個(gè)。4個(gè)LSB是二進(jìn)制權(quán)重電流源,每個(gè)低位比特等于前一比特值的一半。

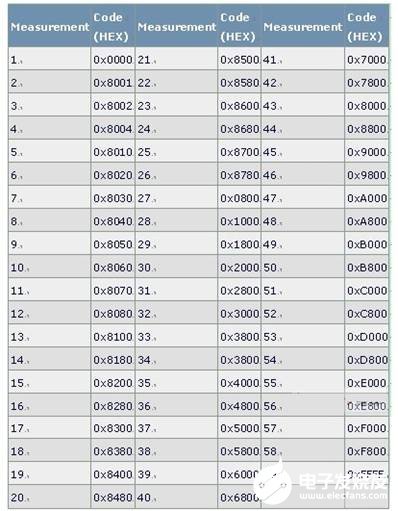

電流源的總數(shù)57 (31 + 15 + 7 + 4)加上滿幅值和零值,確定了測(cè)量MAX5891線性度所需的最少編碼數(shù)。59次測(cè)量支持重新構(gòu)建完整的DAC輸出傳輸函數(shù)。一旦確定了傳輸函數(shù),即可計(jì)算線性度。該方法雖然縮短了測(cè)試時(shí)間,但降低了測(cè)量精度。表1列出了推薦的MAX5891編碼組。

表1. 5-4-3-4體系結(jié)構(gòu)16位編碼組

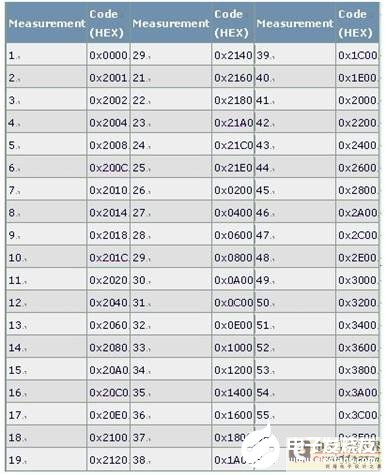

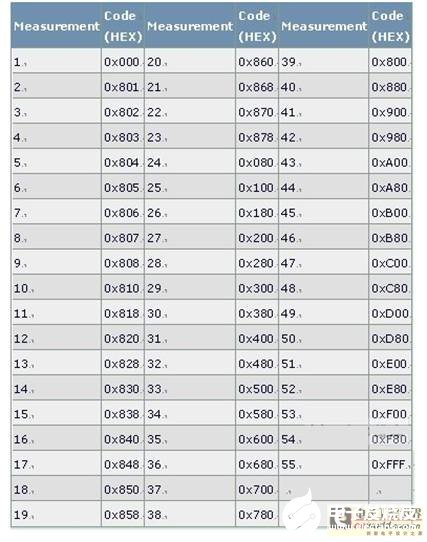

MAX5890和其他Maxim 14位器件使用5-4-3-2分段體系結(jié)構(gòu),14位體系結(jié)構(gòu)的編碼組如表2所示。MAX5889和其他Maxim 12位器件使用5-4-3體系結(jié)構(gòu),12位體系結(jié)構(gòu)的編碼組如表3所示。

表2. 5-4-3-2體系結(jié)構(gòu)的14位編碼組

你知道OpenVINO嗎?如何快速研制先進(jìn)多通道傳感器仿真系統(tǒng)?測(cè)量差分輸出,電流模式數(shù)/模轉(zhuǎn)換器(DAC)的線性度

表3。5-4-3系統(tǒng)結(jié)構(gòu)的12位編碼組

定義了編碼組后,必須解決采集測(cè)量點(diǎn)的問題。適合此類測(cè)量的萬用表是安捷倫?3458,分辨率高達(dá)8.5位。該表連接在MAX5891的OUTP和OUTN端之間,輸出端以50Ω負(fù)載接地。當(dāng)DAC設(shè)置為20mA滿量程電流時(shí),萬用表輸入得到的電壓擺幅為±1V。

萬用表最小設(shè)置為固定的1.2V,使用最大分辨率,得到10nV最小測(cè)量結(jié)果。切換表的會(huì)議會(huì)測(cè)量值的增益誤差;因此,使用單電壓變化可以避免其他的誤差源。由于需要鎖存數(shù)字輸入,MAX5891還需要時(shí)鐘信號(hào)。一旦連接好了萬用表,時(shí)鐘源,電源和數(shù)字輸入控制,就可以采集線性度測(cè)量點(diǎn)。

采集所有測(cè)量點(diǎn)后,需要畫出重建后的DAC輸出傳輸函數(shù)。由于對(duì)每一電流源都進(jìn)行了測(cè)量,很容易產(chǎn)生對(duì)應(yīng)于所有編碼的傳輸函數(shù)。例如,考慮器件的4個(gè)LSB。我們測(cè)量編碼0x8000、0x8001、0x8002、0x8004和0x8008。對(duì)于編碼0x8000,LSB計(jì)算的基準(zhǔn)是DAC等級(jí)中部。LSB權(quán)重是在0x8001測(cè)得的電壓值指示燈在0x8000測(cè)得的電壓值。

在0x8001和0x8780之間測(cè)量的所有編碼采用相同的公式。0x0800到0xF800的其他點(diǎn)是MSB電流源,以編碼0x0000為基準(zhǔn)進(jìn)行計(jì)算。考慮編碼0x4F31作為各種電流相加的例子。

首先,我們需要確定哪一測(cè)量點(diǎn)什么時(shí)候相加能夠等于實(shí)例編碼。0x4800是小于目標(biāo)編碼的最大MSB。從0x4F31中編碼0x4800后的余數(shù)為0x0331。編碼0x0300是可以減掉的次最大編碼(0x8300-0x8000),接下來是0x0030(0x8030-0x8000),最后是0x0001(0x8001-0x8000)。

因此,可以采用下面的等式來表示編碼0x4F31的電壓值:

[V(0x4800)-V(0x0000)] + [V(0x8300)-V(0x8000)] + [V(0x8030)-V(0x8000)] + [V(0x8001)-V(0x8000)](公式1 )

使用相似的等式,可以計(jì)算任意給定輸入編碼的電壓值。利用MATLAB?或Excel?軟件等工具可以很容易地計(jì)算所有編碼的電壓,重建全部的DAC傳輸。

一旦建立了傳輸函數(shù),就。可以計(jì)算線性度第一步是根據(jù)傳輸函數(shù)的端點(diǎn)計(jì)算LSB的電壓值(端點(diǎn)法)

VLSB = [V(0xFFFF的) - V(0×0000)] / [2N - 1](公式2)

其中

?是器件分辨率(16、14或12位)

V(0x0000)是測(cè)得的DAC零標(biāo)輸出電壓

。V(0xFFFF)是測(cè)得的DAC滿幅輸出電壓。采用

下面的等式來計(jì)算任意給定編碼的INL:

INLCODE(LSB)= [VCODE-(CODE×VLSB)] / VLSB(公式3)

其中

CODE是要計(jì)算的數(shù)字編碼

。VLSB是公式2中計(jì)算的電壓值

。VCODE是計(jì)算的DAC輸出電壓值。

下面的等式用于計(jì)算任意給定編碼的DNL:

DNLCODE(個(gè)LSB)= [VCODE - VCODE -1 - VLSB] / VLSB(公式4)

其中

,CODE是要計(jì)算的數(shù)字編碼

VCODE是針對(duì)CODE計(jì)算的。DAC輸出電壓值

VCODE-1是針對(duì)CODE - 1計(jì)算的DAC輸出電壓值。

VLSB是公式2中計(jì)算的電壓值。下面通過使用

MATLAB腳本計(jì)算MAX5889,MAX5890和MAX5891的線性度進(jìn)行說明。每次計(jì)算都得到最小和最大DNL和INL誤差編碼和誤差值。實(shí)例還為所有編碼畫出要求用戶輸入前面表格中所列出的編碼的電壓測(cè)量值。必須按照依次順序輸入數(shù)值。

計(jì)算16位線性度的MATLAB

腳本函數(shù)Lin16(Measurements)

%計(jì)算INL和DNL。具有5-4-3-4分段架構(gòu)的16位設(shè)備的

百分比DACCodes是到16位DAC

DACCodes = [0:65535]‘的可能輸入數(shù)據(jù)的范圍;

從測(cè)量點(diǎn)計(jì)算出每個(gè)代碼的%VOUT。

%創(chuàng)建一個(gè)VOUT變量,并用零填充

VOUT = zeros(size(DACCodes));

%第一個(gè)測(cè)量值為零標(biāo)度點(diǎn),或代碼(0x0000)

ZS = Measurements(1);

VOUT(1)= ZS;

%最后一次測(cè)量是滿量程點(diǎn)或代碼(0xFFFF)

FS =測(cè)量值(長(zhǎng)度(測(cè)量值));

VOUT(65536)= FS;

%Midscale存儲(chǔ)在輸入數(shù)據(jù)數(shù)組

MS的第43位,MS = Measurements(43);

設(shè)備具有四個(gè)細(xì)分級(jí)別

Segments = 4;

%LSB代碼的十進(jìn)制值為1、2、4和8

Seg1Codes = [1; 2; 4; 8]; 對(duì)于i = 1:4 Seg1V(i)= Measurements(i + 1)-MS,

LSB的電壓在輸入陣列的位置2-5中。end %第二段細(xì)分由輸入代碼16到%112進(jìn)行控制,步長(zhǎng)為16。創(chuàng)建代碼數(shù)組并填充%sthisegmentation level Seg2Codes = [16:16:16 * 7]’的測(cè)量值;對(duì)于i = 1:7 Seg2V(i)= Measurements(i + 5)-MS; 結(jié)束

細(xì)分級(jí)別3使用128到1920的輸入代碼,步長(zhǎng)為128。

%創(chuàng)建代碼數(shù)組并填充測(cè)量值數(shù)組。

Seg3Codes = [128:128:128 *(2 ^ 4-1)]‘;

對(duì)于i =

1:15 Seg3V(i)= Measurements(i + 12)-MS;

結(jié)束

%細(xì)分級(jí)別3使用輸入代碼2048到63,488,步長(zhǎng)為2048。

%創(chuàng)建代碼數(shù)組并填充測(cè)量值數(shù)組。

Seg4Codes = [2048:2048:2048 *(2 ^ 5-1)]’;

對(duì)于i =

1:31 Seg4V(i)= Measurements(i + 27)-ZS;

結(jié)束

%已經(jīng)定義了端點(diǎn),現(xiàn)在填寫

DAC傳遞函數(shù)的%剩余點(diǎn)的電壓。

對(duì)于i = 2:65535

targetcode = i-1;

VOUT(i)= ZS; 如果seg4Codes 《= targetcode

,則s = 31:-1:1

targetcode = targetcode-Seg4Codes(s);

VOUT(i)= VOUT(i)+ Seg4V(s);

s = 0;

端

結(jié)束

對(duì)于s = 15:-1:1

如果Seg3Codes(S)《= targetcode

targetcode = targetcode-Seg3Codes(一個(gè)或多個(gè));

VOUT(i)= VOUT(i)+ Seg3V(s);

s = 0;

端

如果targetcode == 0

S = 0;

端

結(jié)束

-1:對(duì)于s = 7 1

如果Seg2Codes(S)《= targetcode

targetcode = targetcode-Seg2Codes(一個(gè)或多個(gè));

VOUT(i)= VOUT(i)+ Seg2V(s);

s = 0;

端

如果targetcode == 0

S = 0;

端

結(jié)束

如果targetcode == 0

S = 0; 如果Seg1Codes 《= targetcode targetcode = targetcode-Seg1Codes(s),則

結(jié)束

于s = 4:-1:1 。

VOUT(i)= VOUT(i)+ Seg1V(s);

結(jié)束

結(jié)束

結(jié)束

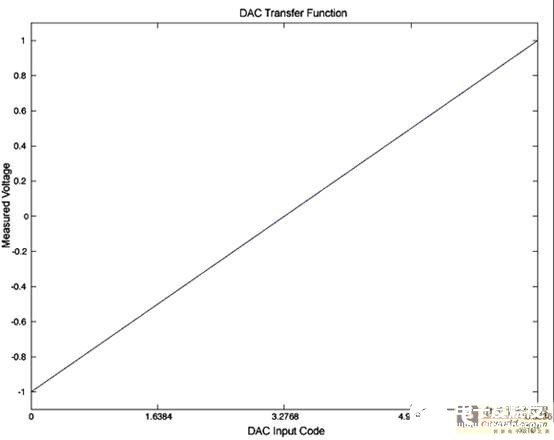

%繪制傳遞函數(shù)

圖(1)

圖(DACCodes,VOUT);

xlabel(‘DAC輸入代碼’);

ylabel(‘實(shí)測(cè)電壓’);

軸([0 65536 -1.1 1.1]);

title(‘DAC傳遞函數(shù)’);

set(gca,‘XTick’,0:16384:65536)

%計(jì)算線性度

LSB =(max(VOUT)-min(VOUT))/ 65535;

INL(1)= 0;

DNL(1)= 0;

對(duì)于i = 2:65536

INL(i)=(VOUT(i)-(VOUT(1)+(i-1)* LSB))/ LSB;

DNL(i)=(VOUT(i)-VOUT(i-1)-LSB)/ LSB;

結(jié)束

%Plot INL

圖(2)

圖(DACCodes,INL);

title(‘DAC積分線性度’);

xlabel(‘DAC輸入代碼’);

ylabel(‘INL(LSBs)’);

軸([0 65536 min(INL)* 1.1 max(INL)* 1.1]);

set(gca,‘XTick’,0:16384:65536)

%繪制DNL

圖(3)

圖(DACCodes,DNL);

title(‘DAC差分線性度’);

xlabel(‘DAC輸入代碼’);

ylabel(‘DNL(LSBs)’);

軸([0 65536 min(DNL)* 1.1 max(DNL)* 1.1]);

set(gca,‘XTick’,0:16384:65536)

txtstr = sprintf(‘INL MAX =%f’,max(INL));

顯示(txtstr);

txtstr = sprintf(‘INL MIN =%f’,min(INL));

顯示(txtstr);

txtstr = sprintf(‘DNL MAX =%f’,max(DNL));

顯示(txtstr);

txtstr = sprintf(‘DNL MIN =%f’,min(DNL));

顯示(txtstr);

16位腳本產(chǎn)生的曲線

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論