完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > fpga

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。

文章:12600個 瀏覽:618645次 帖子:7908個

晶圓的另一面:背面供電領(lǐng)域的最新發(fā)展研究

在我從事半導(dǎo)體設(shè)備的職業(yè)生涯之初,晶圓背面是個麻煩問題。當(dāng)時發(fā)生了一件令我記憶深刻的事:在晶圓傳送的過程中,幾片晶圓從機(jī)器人刀片上飛了出來。

RPP「六邊形戰(zhàn)士」處理器:融合NPU與GPU優(yōu)勢,兼具高效與實時性的AI新星

? 在科技江湖中,處理器家族群英薈萃,各展神通,從DSP到NPU再到GPGPU,每款處理器優(yōu)劣各異,各有所長。正是這些處理器的優(yōu)點,使它們在特定的市場領(lǐng)...

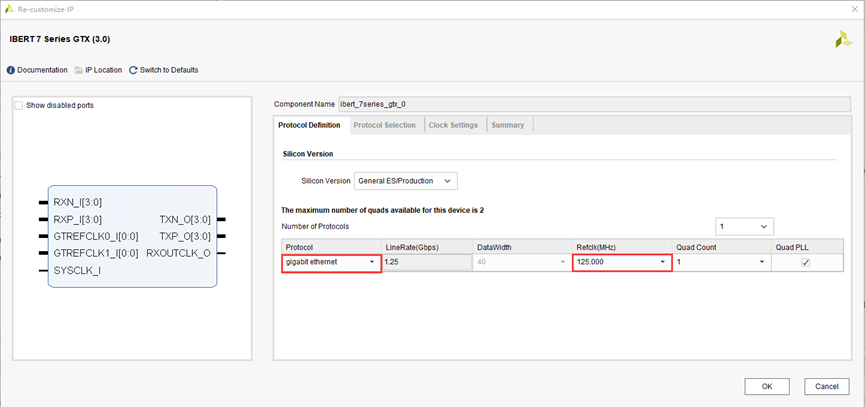

本文介紹一個FPGA開源項目:基于IBERT的GTX數(shù)據(jù)傳輸測試。IBERT是指誤碼率測試,在Vivado軟件中,IBERT 7 Series GTX ...

2023-08-31 標(biāo)簽:fpga收發(fā)器數(shù)據(jù)傳輸 3655 0

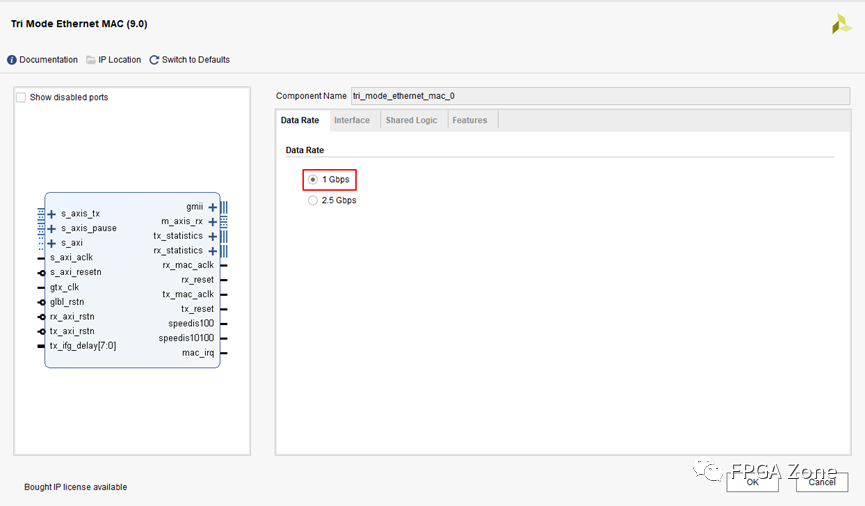

本文介紹一個FPGA開源項目:UDP千兆以太網(wǎng)光通信。利用SFP接口,可以通過使用SFP轉(zhuǎn)RJ45模塊或者直接使用光纖進(jìn)行以太網(wǎng)通信。

2023-08-31 標(biāo)簽:fpga接口千兆以太網(wǎng) 5449 0

基于Xilinx FPGA AXI-EMC IP的EMIF通信測試

外部存儲器接口( EMIF )通信常用于FPGA和DSP之間的數(shù)據(jù)傳輸,即將FPGA作為DSP的外部SRAM、或者協(xié)同處理器等。Xilinx提供了AXI...

Xilinx 7系列FPGA的時鐘結(jié)構(gòu)解析

通過上一篇文章“時鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區(qū)域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結(jié)合,Xilin...

中國市場FPGA產(chǎn)業(yè)競爭格局現(xiàn)狀分析

在應(yīng)用領(lǐng)域方面,行業(yè)龍頭企業(yè) AMD(Xilinx)、Intel(Altera)的產(chǎn)品已可對工業(yè)控制、網(wǎng)絡(luò)通信、消費電子、數(shù)據(jù)中心、汽車電子、人工智能等...

目前TCP協(xié)議大多由cpu跑代碼實現(xiàn), 這次用FPGA的純邏輯實現(xiàn) , System Verilog編寫,下面給大家粗略講一下我的實現(xiàn)方法,下面是工程的示意圖。

2023-08-30 標(biāo)簽:fpga千兆以太網(wǎng)TCP 1070 0

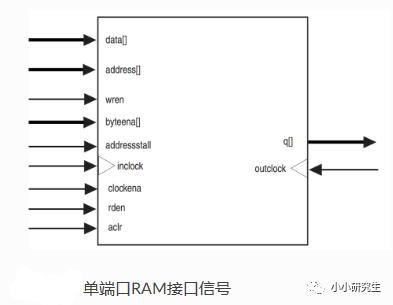

FPGA學(xué)習(xí)筆記:RAM IP核的使用方法

我們知道除了只讀存儲器外還有隨機(jī)存取存儲器,這一篇將介紹另一種 存儲類IP核 ——RAM的使用方法。RAM是 隨機(jī)存取存儲器 (Random Acces...

關(guān)鍵件重要件及關(guān)鍵過程的區(qū)別

對于所謂關(guān)鍵工序多出現(xiàn)在現(xiàn)場作業(yè)工藝文件,只是工藝管理的具體要求,對應(yīng)工藝執(zhí)行,不涉及產(chǎn)品可靠性分析。(當(dāng)然工藝文件好壞一定影響產(chǎn)品質(zhì)量),但對產(chǎn)品固有...

深度解析CPLD和FPGA內(nèi)部結(jié)構(gòu)和原理

大多數(shù)FPGA都具有內(nèi)嵌的塊RAM,這大大拓展了FPGA的應(yīng)用范圍和靈活性。塊RAM可被配置為單端口RAM、雙端口RAM、內(nèi)容地址存儲器(CAM)以及F...

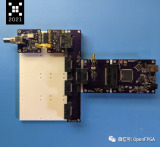

通過使用Xilinx 的 XC7A35T-2CSG325C Artix-7 FPGA,ThunderScope 可以將 1 GB/s 的實時采樣數(shù)據(jù)傳輸...

2023-08-29 標(biāo)簽:fpga示波器數(shù)據(jù)傳輸 1038 0

其實用FPGA做的示波器有很多,開源的相對較少,我們今天就簡單介紹一個使用FPGA做的開源示波器。

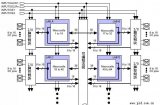

本系統(tǒng)的硬件設(shè)計有本團(tuán)隊成員使用Cadence系列軟件進(jìn)行EDA設(shè)計,包括原理圖庫設(shè)計、原理圖設(shè)計、PCB封裝庫設(shè)計以及PCB設(shè)計。本作品的硬件系統(tǒng)原理...

2023-08-28 標(biāo)簽:fpga液晶顯示器EDA設(shè)計 1155 0

基于FPGA的電機(jī)控制系統(tǒng)設(shè)計

FPGA 非常適合精密電機(jī)控制,在這個項目中,我們將創(chuàng)建一個簡單的電機(jī)控制程序,在此基礎(chǔ)上可以構(gòu)建更復(fù)雜的應(yīng)用。

2023-08-28 標(biāo)簽:fpga控制系統(tǒng)電機(jī)控制 1887 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |