完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > fpga

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。

文章:12600個(gè) 瀏覽:618564次 帖子:7908個(gè)

什么是FPGA原型驗(yàn)證?FPGA原型設(shè)計(jì)的好處是什么?

FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上...

接口和連接資源接口和連接功能主要包括無線基站對外的高速通信接口(PCI Express、以太網(wǎng) MAC、高速 AD/DA 接口)以及內(nèi)部相應(yīng)的背板協(xié)議(...

2023-02-09 標(biāo)簽:fpga算法數(shù)字信號處理 1745 0

鋯石FPGA A4_Nano開發(fā)板視頻:多終端點(diǎn)歌系統(tǒng)設(shè)計(jì)實(shí)戰(zhàn)

點(diǎn)歌系統(tǒng)中的專業(yè)版被廣泛應(yīng)用于ktv、酒店、酒吧等娛樂場所中,它是全電腦自動(dòng)操作,無需DJ操作,無需換碟、換節(jié)目、無盤片磨損之憂,不存在花碟、死機(jī)等現(xiàn)像。

AMD Versal系列FPGA NoC介紹及實(shí)戰(zhàn)

NoC是相對于SoC的新一代片上互連技術(shù),從計(jì)算機(jī)發(fā)展的歷史可以看到NoC 必將是SoC 之后的下一代主流技術(shù),SoC 通常指在單一芯片上實(shí)現(xiàn)的數(shù)字計(jì)算...

2023-07-13 標(biāo)簽:fpgaamd計(jì)算機(jī) 1745 0

鋯石FPGA A4_Nano開發(fā)板視頻:DA外設(shè)IP核定制

IP核有三種不同的存在形式:HDL語言形式,網(wǎng)表形式、版圖形式。分別對應(yīng)我們常說的三類IP內(nèi)核:軟核、固核和硬核。這種分類主要依據(jù)產(chǎn)品交付的方式,而這三...

阿里FPGA云服務(wù)器平臺(tái)FaaS,可大大降低加速器的開發(fā)與部署成本

FPGA (現(xiàn)場可編程門陣列)由于其硬件并行加速能力和可編程特性,在傳統(tǒng)通信領(lǐng)域和IC設(shè)計(jì)領(lǐng)域大放異彩。一路走來,F(xiàn)PGA的技術(shù)并不是一個(gè)新興的硬件器...

采用FPGA芯片的系統(tǒng)應(yīng)用的電源管理問題

目前的電子產(chǎn)品市場競爭非常激烈,廠商都希望能在最短時(shí)間內(nèi)將新產(chǎn)品推出市場,以致子系統(tǒng)的設(shè)計(jì)周期越縮越短。在這個(gè)發(fā)展過程中,F(xiàn)PGA及ASIC 的重要性越...

FIFO為什么不能正常工作?復(fù)位信號有效長度不夠,接口時(shí)序不匹配,可看下面這篇文章。 本文將介紹: 非DFX工程如何確保異步FIFO自帶的set_max...

2023-11-02 標(biāo)簽:fpgaFPGA設(shè)計(jì)fifo 1743 0

采用LED光通信技術(shù)實(shí)現(xiàn)溫度實(shí)時(shí)顯示系統(tǒng)的設(shè)計(jì)

LED光通信,就是用LED光來實(shí)現(xiàn)無線通信,主要是靠發(fā)光二極管(LED)發(fā)出的高速亮滅閃爍信號來傳輸信息的。LED光通信具有傳輸數(shù)據(jù)率高,保密性強(qiáng),無電...

FPGA(現(xiàn)場可編程門陣列)芯片中的觸發(fā)器是一種重要的存儲(chǔ)元件,它在數(shù)字電路設(shè)計(jì)中起著至關(guān)重要的作用。觸發(fā)器的主要功能是存儲(chǔ)和同步數(shù)字信號,確保電路在正...

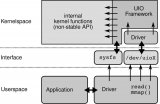

使用Linux UIO框架實(shí)現(xiàn)ARM和FPGA的高效通信

在 ARM 和 FPGA 之間通信的通信過程中,通信開始或者完成時(shí),需要實(shí)時(shí)通知對方,如果 ARM 使用類似 while (1) 循環(huán)進(jìn)行反復(fù)查看標(biāo)志位...

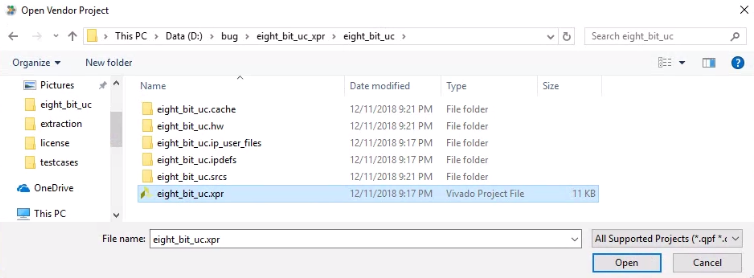

如何使用 InTime 軟件優(yōu)化 FPGA 設(shè)計(jì)

教程介紹 本教程旨在指導(dǎo)用戶通過 Plunify Cloud 的云服務(wù)器,來使用 InTime 軟件優(yōu)化 FPGA 設(shè)計(jì)。如果您首次使用 InTime,...

2020-12-21 標(biāo)簽:fpga 1739 0

了解FPGA如何允許您根據(jù)您的特定需求進(jìn)行定制,同時(shí)使您能夠保護(hù)您在市場中的差異化。

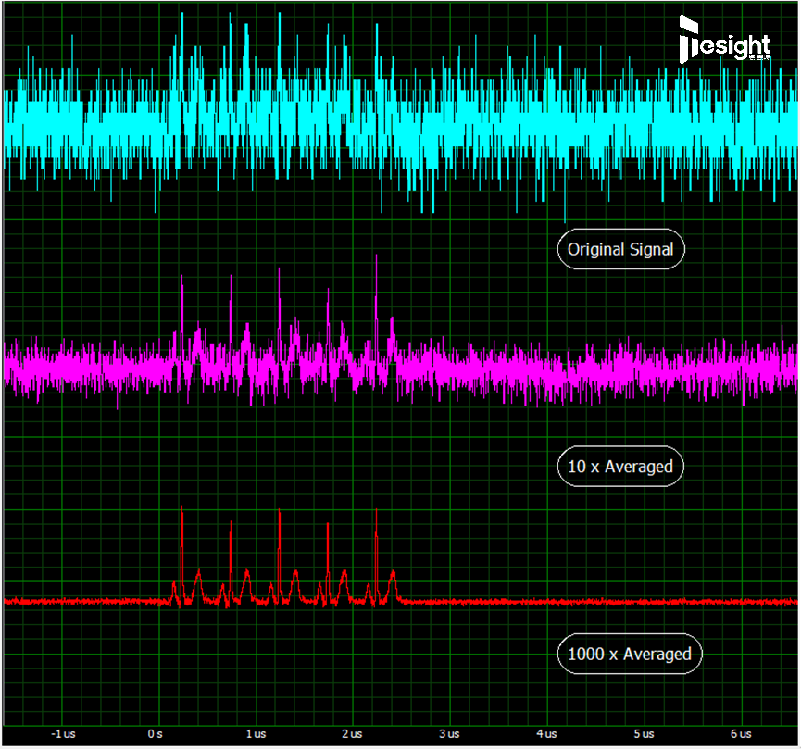

德思特分享 突破FPGA限制:德思特TS-M4i系列數(shù)字化儀利用GPU加速實(shí)現(xiàn)高效塊平均處理

本白皮書將展示如何使用德思特TS-M4i系列數(shù)字化儀的高速PCIe流模式來在軟件中實(shí)現(xiàn)塊平均處理,從而突破FPGA的限制。我們用了TS-M4i.2230...

如何根據(jù)自己設(shè)計(jì)中的寄存器配置總線定義來生成一套寄存器配置模版

無論是FPGA還是ASIC,系統(tǒng)設(shè)計(jì)中總會(huì)存在配置寄存器總線的使用,我們會(huì)將各種功能、調(diào)試寄存器掛載在寄存器總線上使用。

使用DDS生成三個(gè)信號并在Vivado中實(shí)現(xiàn)低通濾波器

本文使用 DDS 生成三個(gè)信號,并在 Vivado 中實(shí)現(xiàn)低通濾波器。低通濾波器將濾除相關(guān)信號。

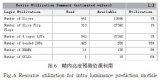

基于FPGA的幀內(nèi)預(yù)測編碼器硬件架構(gòu)設(shè)計(jì)詳解

針對幀內(nèi)預(yù)測的快速算法,由于DSP 架構(gòu)軟件順序執(zhí)行的局限性難以滿足實(shí)時(shí)性要求,而FPGA 以其高速的計(jì)算速度和強(qiáng)大的并行處理能力成為H.264 和A...

基于FPGA系統(tǒng)應(yīng)用的供電要求和最新高性能DC/DC穩(wěn)壓器解決方案詳解

隨著FPGA制造工藝尺寸持續(xù)縮小、設(shè)計(jì)配置更加靈活,以及采用FPGA的系統(tǒng)的不斷發(fā)展,原來只采用微處理器和ASIC的應(yīng)用現(xiàn)在也可以用FPGA來實(shí) 現(xiàn)了。...

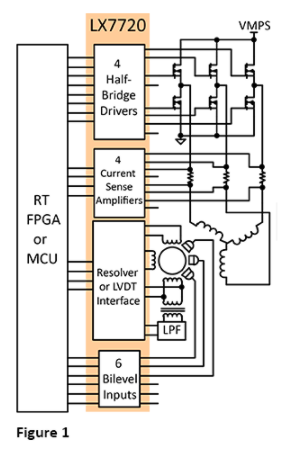

使用LX7720的電機(jī)驅(qū)動(dòng)器:將LX7720如何集成到電機(jī)驅(qū)動(dòng)系統(tǒng)中

LX7720航天器電機(jī)驅(qū)動(dòng)器經(jīng)過設(shè)計(jì),經(jīng)過抗輻射處理。它是空間場可編程門陣列(FPGA)的配套集成電路(IC),例如Microchip的RTG4 FPG...

2023-04-23 標(biāo)簽:fpga驅(qū)動(dòng)器電機(jī) 1737 0

使用MATLAB Simulink和HDL編碼器創(chuàng)建自定義IP--AWB

自動(dòng)白平衡模塊的設(shè)計(jì)是使用 HDL Coder 在 MATLAB 和 Simulink 中創(chuàng)建的。HDL Coder能夠生成 HDL 文件,這些文件可以...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |