Versal ACAP(自適應(yīng)計(jì)算加速平臺(tái))是高度集成化的多核計(jì)算平臺(tái),可通過(guò)靈活的自適應(yīng)能力來(lái)滿(mǎn)足不斷變化的動(dòng)態(tài)算法的需求。VCK190 是賽靈思最早發(fā)布的 Versal AI Core 評(píng)估器

2020-09-28 10:57:58 4804

4804

1. 介紹 Vitis是Xilinx新推出的統(tǒng)一軟件平臺(tái),可實(shí)現(xiàn)在 Xilinx 所有芯片(包括 FPGA、SoC 和 Versal ACAP)上開(kāi)發(fā)嵌入式軟件和加速應(yīng)用。Xilinx主要宣傳

2020-11-04 12:03:25 5069

5069

從 2019.2 版開(kāi)始,賽靈思 SDK 開(kāi)發(fā)環(huán)境已統(tǒng)一整合到全功能一體化的 Vitis 統(tǒng)一軟件平臺(tái) 中。 馬上開(kāi)始將工程從賽靈思 SDK 移植到 Vitis 吧。 Vivado 工程升級(jí) 工程

2020-11-09 16:57:12 2283

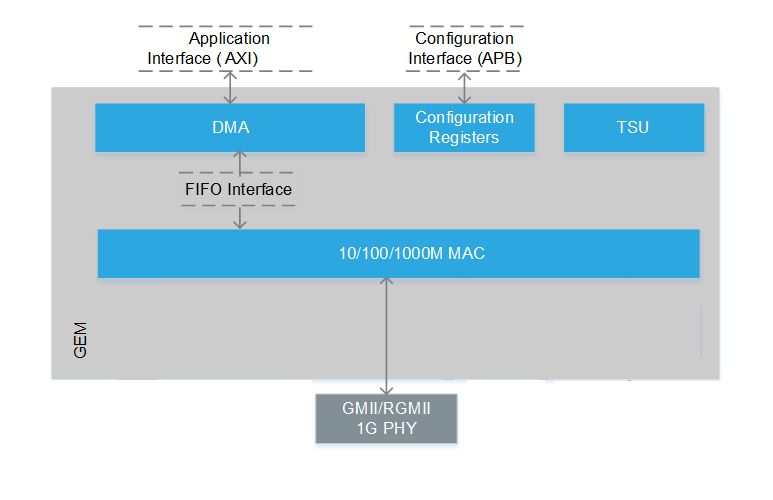

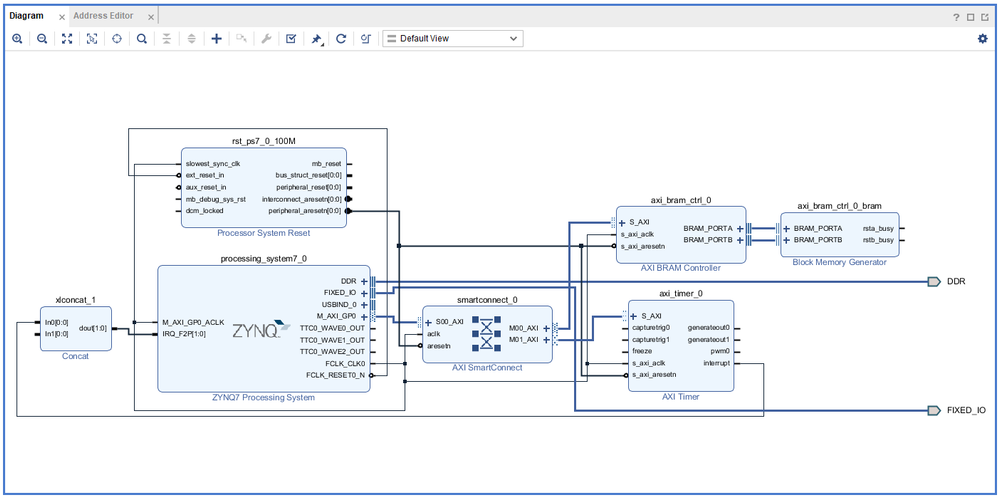

2283 本篇中,我想跳過(guò)一些細(xì)枝末節(jié), 先簡(jiǎn)單介紹 AMD Xilinx Vitis AI 在 Zynq 這個(gè)硬件加速平臺(tái)下軟硬件開(kāi)發(fā)的基本思路和流程,把各個(gè)開(kāi)發(fā)流程和工具分開(kāi),幫助剛剛接觸Vitis/Vitis AI的同學(xué)快速找到學(xué)習(xí)和開(kāi)發(fā)的方向。

2022-12-21 10:15:33 1353

1353 通過(guò)賽靈思 SoC 和自適應(yīng)計(jì)算加速平臺(tái) (ACAP) 來(lái)充分發(fā)掘 AI 加速的全部潛能。Vitis AI 開(kāi)發(fā)環(huán)境將底層可編程邏輯的繁復(fù)細(xì)節(jié)加以抽象化,從而幫助不具備 FPGA 知識(shí)的用戶(hù)輕松開(kāi)發(fā)深度學(xué)習(xí)推斷應(yīng)用。

2023-09-28 00:05:50 2031

2031

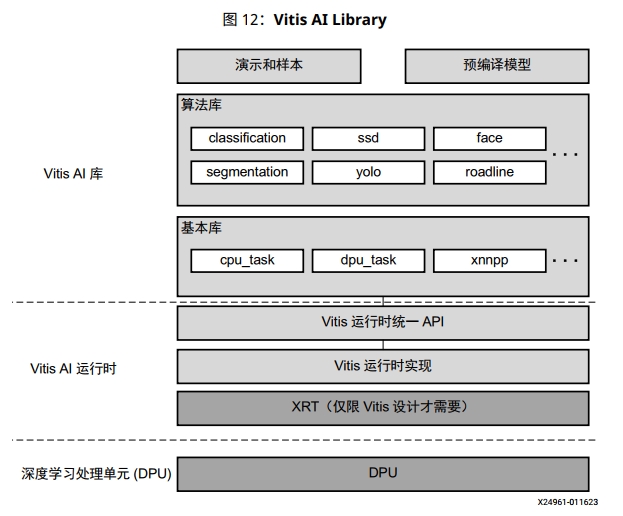

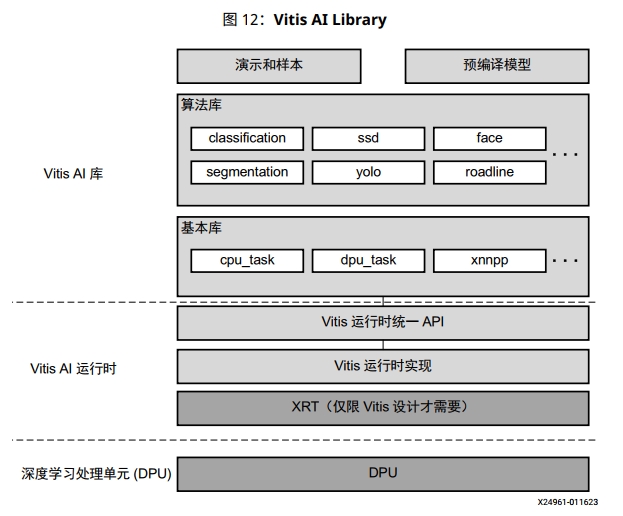

Vitis AI Library是一組高層次庫(kù)和 API,專(zhuān)為利用 DPU 高效執(zhí)行 AI 推斷而構(gòu)建。它是基于 Vitis AI運(yùn)行時(shí)利用 Vitis運(yùn)行時(shí)統(tǒng)一 API 來(lái)構(gòu)建的,能夠?yàn)?XRT 提供完整支持。

2023-10-17 08:23:20 522

522

2019年“FPGA國(guó)際研討會(huì)”上,賽靈思發(fā)表了兩篇長(zhǎng)論文,詳細(xì)介紹了賽靈思“自適應(yīng)計(jì)算加速平臺(tái)”ACAP的系統(tǒng)架構(gòu)和技術(shù)細(xì)節(jié)。本文將對(duì)ACAP的主要架構(gòu)創(chuàng)新進(jìn)行深入解讀,讓各位先睹為快。

2020-11-27 07:30:17

Vitis AI Model Zone軟件平臺(tái)具備哪些功能?Vitis AI Model Zone軟件平臺(tái)的應(yīng)用范圍包括哪些?

2021-07-09 06:44:28

Vitis準(zhǔn)備工程及注意事項(xiàng)

2021-01-25 06:26:20

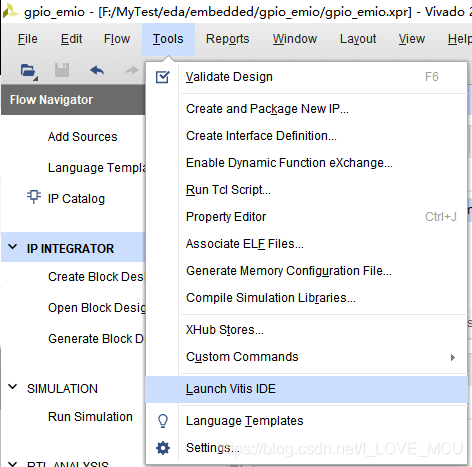

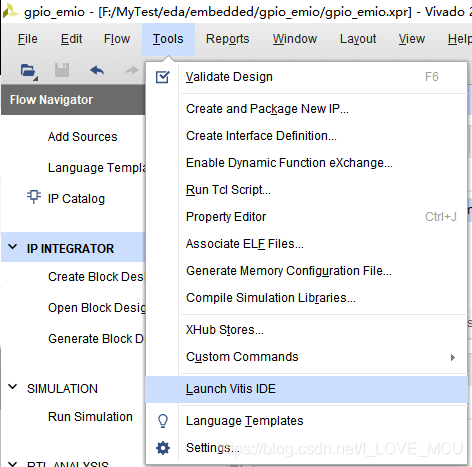

找到vitisvivado->tools->launch vitis ide如果打開(kāi)失敗,說(shuō)明沒(méi)有安裝vitis,先進(jìn)行安裝安裝vitisvivado->help->Add

2020-12-23 17:10:37

在學(xué)習(xí)ZYNQ嵌入式開(kāi)發(fā)的過(guò)程中,正點(diǎn)原子的教程是采用SDK,而我下載的vivado2020.1已經(jīng)變成了vitis,所以寫(xiě)一這篇博客,方便后續(xù)查閱。

2021-02-04 07:09:50

RTC介紹中斷介紹Vitis程序編寫(xiě)

2021-02-25 07:39:08

vitis和vivado有什么區(qū)別和聯(lián)系呢

2023-10-16 07:55:35

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開(kāi)源出來(lái)了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

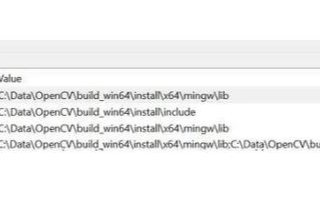

源文件,之后Clean,再之后Build(Ctrl + B)。 注:中間會(huì)彈出來(lái)一個(gè)錯(cuò)誤的提示,不用理會(huì),等待工程編譯完成,錯(cuò)誤提示就不存在了。 更改目錄后vitis工程需要重新加載平臺(tái) 在建

2021-01-15 16:46:02

廠(chǎng)商的數(shù)據(jù)中心中都會(huì)搭載賽靈思的技術(shù)與產(chǎn)品,讓開(kāi)發(fā)者可以直接通過(guò)云服務(wù)軟件接入賽靈思ACAP/FPGA的能力,不需要硬件開(kāi)發(fā)能力。 根據(jù)深鑒科技給出的數(shù)據(jù),賽靈思提供的高效FPGA加速語(yǔ)音識(shí)別引擎

2018-03-23 14:31:40

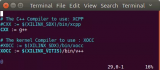

kernel-devel kernel-tools

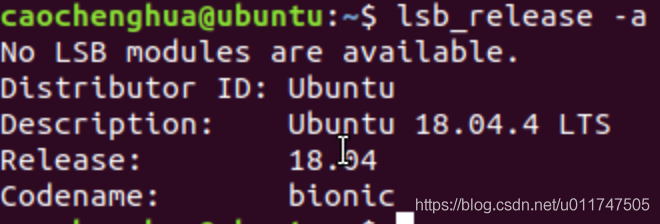

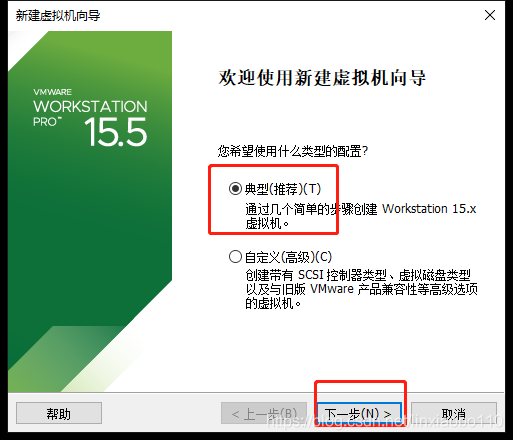

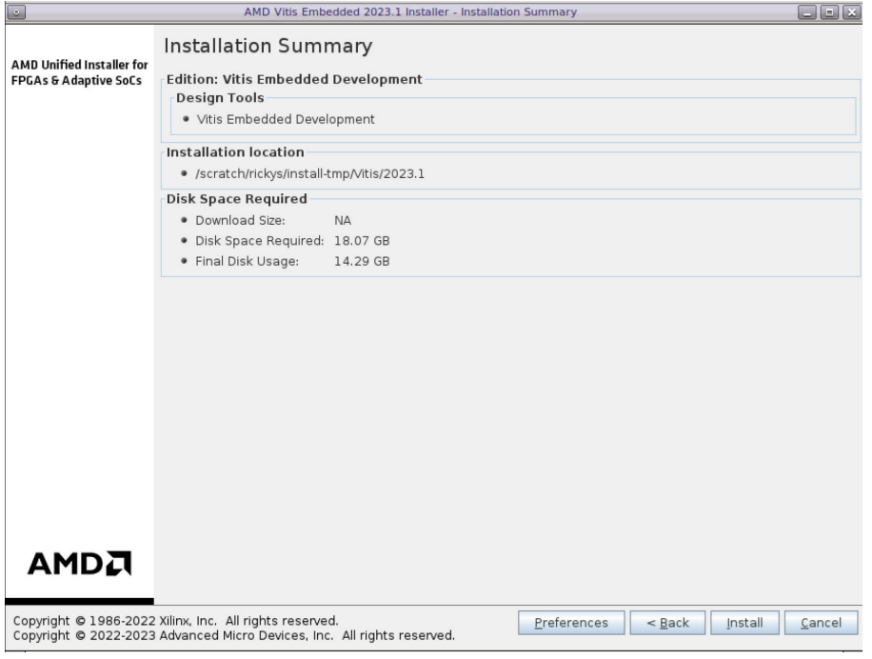

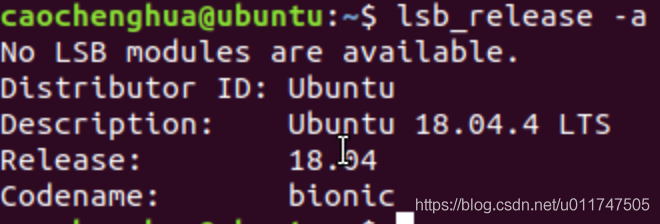

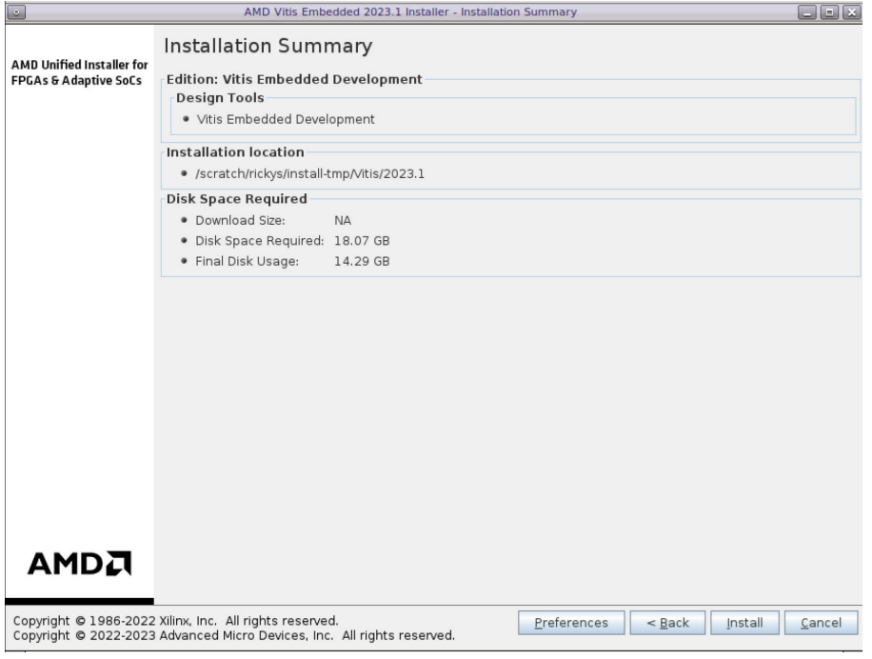

3. Vitis-v2022.2安裝

推薦使用Vitis-v2022.2開(kāi)發(fā)環(huán)境,安裝流程耗時(shí)約半個(gè)工作日,注意時(shí)間分配。

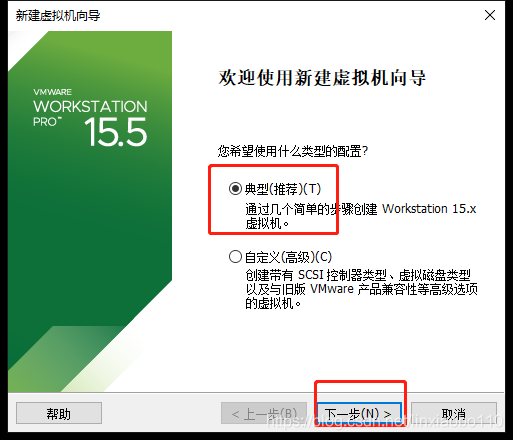

3.1 基本流程概述

2023-08-27 21:22:34

速度、用戶(hù)界面的友好性,產(chǎn)品的穩(wěn)定性,易用性及可行性等。

一、Vitis AI Library

Vitis AI Library是一組高層次庫(kù)和 API,專(zhuān)為利用 DPU 高效執(zhí)行 AI 推斷而構(gòu)建

2023-10-16 23:25:11

計(jì)算加速平臺(tái) (ACAP) 來(lái)充分發(fā)掘 AI 加速的全部潛能。Vitis AI 開(kāi)發(fā)環(huán)境將底層可編程邏輯的繁復(fù)細(xì)節(jié)加以抽象化,從而幫助不具備 FPGA 知識(shí)的用戶(hù)輕松開(kāi)發(fā)深度學(xué)習(xí)推斷應(yīng)用。

深度學(xué)習(xí)

2023-09-10 13:15:24

/vitis-ai-cpu:latest

第二步,可以使用了………完………

(^_^),當(dāng)然不是這么簡(jiǎn)單,Vitis AI 不僅僅是一個(gè)工具,而是一個(gè)綜合的 AI 推斷開(kāi)發(fā)平臺(tái),它包括了從模型優(yōu)化到應(yīng)用部署的全流程

2023-10-14 15:34:26

本文將介紹如何使用Vitis-AI加速YOLOX模型實(shí)現(xiàn)視頻中的目標(biāo)檢測(cè),并對(duì)相關(guān)源碼進(jìn)行解讀。由于演示的示例程序源碼是Vitis-AI開(kāi)源項(xiàng)目提供的,本文演示之前會(huì)介紹所需要的準(zhǔn)備工作。演示之后

2023-10-06 23:32:47

Vitis AI 概述

AMD Vitis? AI 開(kāi)發(fā)環(huán)境可在 AMD 硬件平臺(tái)上加速 AI 推斷,包括邊緣器件和 AMD Versal? 加速器卡。這一綜合性框架包括最優(yōu)化 IP 核、多用途

2023-10-16 04:22:23

?filename=xilinx-kv260-dpu-v2022.2-v3.0.0.img.gz

鏡像下載地址

1.2、SD卡系統(tǒng)燒錄

balenaEtcher軟件

二、字符和文本檢測(cè)介紹

字符和文本檢測(cè)是計(jì)算機(jī)

2023-09-26 16:31:59

一、DPU 鏡像環(huán)境配置

官方鏡像已經(jīng)安裝好了可以在安裝相關(guān)配置,示例來(lái)源Vitis AI Library用戶(hù)指南3.0版本,首先需要安裝DPU鏡像。

1.1、克隆Vitis AI倉(cāng)庫(kù)

$ cd

2023-09-26 16:22:43

?filename=xilinx-kv260-dpu-v2022.2-v3.0.0.img.gz

鏡像下載地址

1.2、SD卡系統(tǒng)燒錄

balenaEtcher軟件

二、多任務(wù)執(zhí)行介紹

MultiTask V3

2023-09-26 16:43:01

?filename=xilinx-kv260-dpu-v2022.2-v3.0.0.img.gz

鏡像下載地址

1.2、SD卡系統(tǒng)燒錄

balenaEtcher軟件

二、車(chē)牌檢測(cè)和車(chē)牌識(shí)別介紹

車(chē)牌檢測(cè)是對(duì)包含

2023-09-26 16:28:10

和設(shè)計(jì)示例組成。其設(shè)計(jì)以高效和易用為核心,旨在通過(guò)賽靈思 SoC 和自適應(yīng)計(jì)算加速平臺(tái) (ACAP) 來(lái)充分發(fā)掘 AI 加速的全部潛能。Vitis AI 開(kāi)發(fā)環(huán)境將底層可編程邏輯的繁復(fù)細(xì)節(jié)加以抽象化

2023-09-27 23:21:32

%80%E4%BD%93%E4%B8%AD%E6%96%87/ug1414-vitis-ai/Vitis-AI-%E6%A6%82%E8%BF%B0

首次開(kāi)發(fā)流程和api流程基礎(chǔ)都能參考本文檔。但是依然要有一定的AI基礎(chǔ)

2023-08-27 23:35:48

本文首先將會(huì)對(duì)Vitis統(tǒng)一軟件平臺(tái)和Vitsi AI進(jìn)行簡(jiǎn)單介紹,然后介紹如何在KV260上部署DPU鏡像,最后在KV260 DPU鏡像上運(yùn)行Vitis AI自帶的圖像分類(lèi)示例。通過(guò)本文,你將會(huì)

2023-09-10 23:01:02

和示例設(shè)計(jì)組成。Vitis AI 以高效易用為設(shè)計(jì)理念,可在 Xilinx FPGA 和 ACAP 上充分發(fā)揮人工智能加速的潛力。使用新的軟件平臺(tái)進(jìn)行Ai加速必然需要借助DPU這個(gè)IP核,目前較為實(shí)用且

2020-12-03 19:22:13

1、使用Vitis HLS創(chuàng)建屬于自己的IP高層次綜合(High-level Synthesis)簡(jiǎn)稱(chēng)HLS,指的是將高層次語(yǔ)言描述的邏輯結(jié)構(gòu),自動(dòng)轉(zhuǎn)換成低抽象級(jí)語(yǔ)言描述的電路模型的過(guò)程。對(duì)于AMD

2022-09-09 16:45:27

立即學(xué)習(xí)—60天FPGA工程師入門(mén)就業(yè)項(xiàng)目實(shí)戰(zhàn)特訓(xùn)營(yíng)(3月16日開(kāi)班)Vitis是 Xilinx 最新推出的開(kāi)發(fā)平臺(tái),雖然Vitis 早就在電腦上安裝好了,但一直沒(méi)怎么使用。現(xiàn)在用低成本的ZYNQ礦

2020-03-06 22:59:12

大家好!我是新來(lái)的,是個(gè)真正的菜鳥(niǎo)。本人學(xué)51剛剛?cè)齻€(gè)月,基本的東西應(yīng)該算是掌握了,但是本人是在校學(xué)生,不能去工作又不在實(shí)驗(yàn)室。 1.怎么才可以強(qiáng)化一下呢? 2.我現(xiàn)在可以接著學(xué)STM32么?麻煩各位大神指教!謝謝!

2019-06-03 00:43:53

數(shù)字設(shè)計(jì)及驗(yàn)證技術(shù)演進(jìn)的概觀現(xiàn)代化IC設(shè)計(jì)環(huán)境必須強(qiáng)化的方法

2021-04-09 06:17:44

Vivado硬件平臺(tái)更新后Vitis工程如何快捷更新

2021-03-08 08:00:55

一:深度學(xué)習(xí)DeepLearning實(shí)戰(zhàn)時(shí)間地點(diǎn):1 月 15日— 1 月18 日二:深度強(qiáng)化學(xué)習(xí)核心技術(shù)實(shí)戰(zhàn)時(shí)間地點(diǎn): 1 月 27 日— 1 月30 日(第一天報(bào)到 授課三天;提前環(huán)境部署 電腦

2021-01-10 13:42:26

醬油中鐵強(qiáng)化劑快檢儀深圳市芬析儀器制造有限公司生產(chǎn)的CSY-SAT醬油中鐵強(qiáng)化劑快檢儀能夠快速檢測(cè)醬油中的鐵強(qiáng)化含量;根據(jù)DBS 65006-2012《食品安全地方標(biāo)準(zhǔn) 加鐵醬油》規(guī)定了醬油中鐵強(qiáng)化

2022-05-24 20:44:08

為什么選擇ACAP?

2018-11-21 06:43:00 2968

2968 賽靈思革命性的Versal ACAP,是業(yè)界首款完全支持軟件編程的異構(gòu)計(jì)算平臺(tái),加上賽靈思最新發(fā)布的Vitis統(tǒng)一軟件平臺(tái),賽靈思正引領(lǐng)致力于創(chuàng)新事業(yè)的開(kāi)發(fā)者,邁入自適應(yīng)的下一個(gè)計(jì)算時(shí)代

2019-10-21 15:21:27 837

837 Vitis 2019.2 使用 gcc 編譯 C 語(yǔ)言源代碼,使用 Vivado HLS 編譯與 SDAccel 流匹配的加速內(nèi)核。此外,Vitis 也使用與 SDAccel 相同的目標(biāo)平臺(tái)

2020-06-28 10:05:51 2012

2012

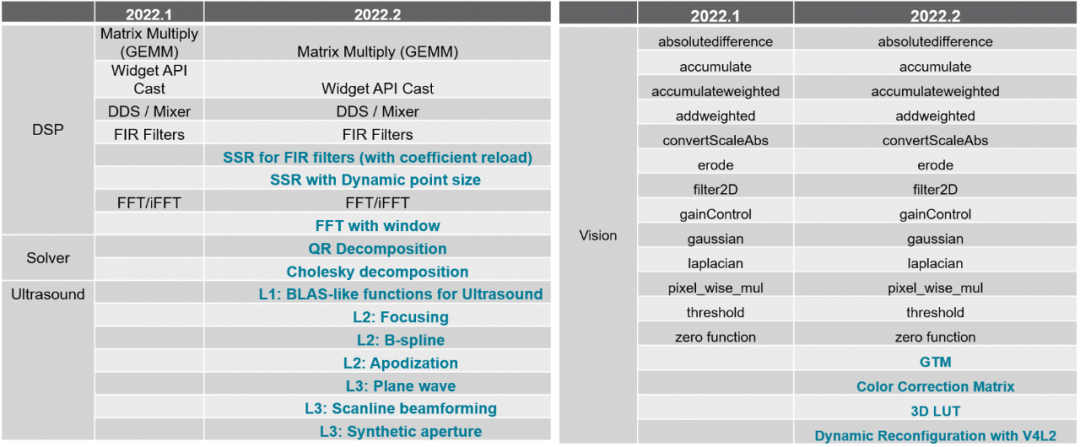

Vitis 加速庫(kù) Vitis 統(tǒng)一軟件平臺(tái)包括一組廣泛的、性能優(yōu)化的開(kāi)源庫(kù),這些庫(kù)提供了即開(kāi)即用的加速功能,并且對(duì)現(xiàn)有應(yīng)用實(shí)現(xiàn)最小化代碼更改或零更改。 常見(jiàn)的 Vitis 加速庫(kù)(用于數(shù)學(xué)、統(tǒng)計(jì)

2020-11-23 15:45:07 1413

1413 的是VivadoIP,用于支持Vivado IP 設(shè)計(jì)流程。后者用于Vitis應(yīng)用加速流程,此時(shí),Vitis HLS會(huì)自動(dòng)推斷接口,無(wú)需在代碼里通過(guò)Pragma或Directive的方式定義Interface,最終會(huì)輸出.xo文件。 User Control Settings還有其他的一些變化,如下表

2020-11-05 17:43:16 37071

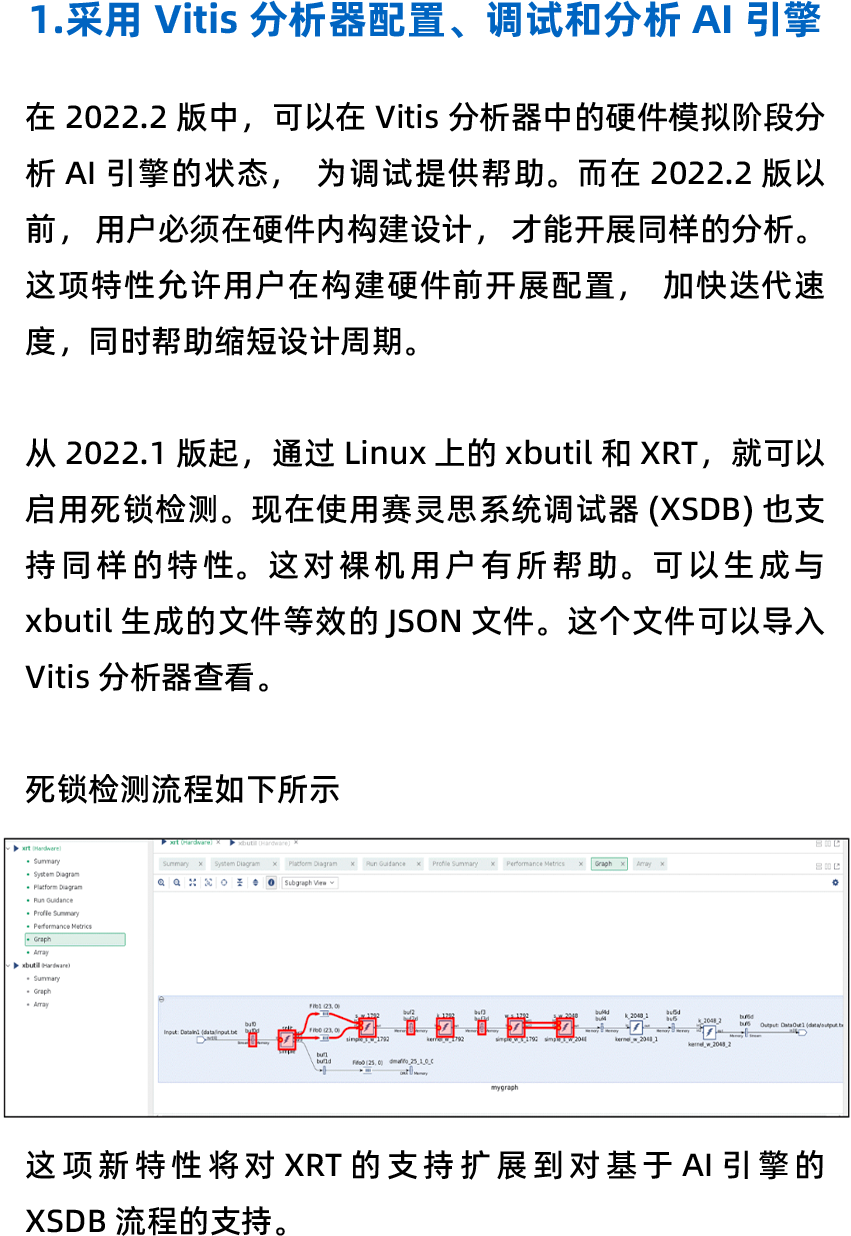

37071 Vitis迎來(lái)了版本更新,Vitis 2020.2 帶來(lái)更加快捷智能的使用體驗(yàn)。首次引入Vitis?AI Engine( AI引擎)編譯器,并提供多個(gè)加速功能。

2020-12-09 09:10:25 1284

1284 這是《創(chuàng)建 Vitis 加速平臺(tái)》系列的第 3 篇博文。在前文中,我們講解了如何創(chuàng)建硬件和軟件工程。在本文中,我們將講解如何在 Vitis 中將所有這些工程封裝在一起。 在 Vitis 中加速軟件

2020-12-26 10:20:54 2465

2465

? 本文給想直接使用Vitis HLS 工具在 Standalone 模式下調(diào)用 Xilinx Vision Library L1 API 的小伙伴提供了一個(gè)非常容易上手的腳本文件。 在論壇上遇到

2020-12-29 11:12:19 3100

3100

、工具、庫(kù)、模型和示例設(shè)計(jì)組成。Vitis AI 以高效易用為設(shè)計(jì)理念,可在 Xilinx FPGA 和 ACAP 上充分發(fā)揮人工智能加速的潛力。 Vitis AI 1.3 將為用戶(hù)提供更完整的深度學(xué)習(xí)框架和模型支持,進(jìn)一步整合了從邊緣端到數(shù)據(jù)中心端的編譯流程,首次發(fā)布面向數(shù)據(jù)中心平臺(tái)的多個(gè) CN

2020-12-29 11:18:24 2594

2594 在瞬息萬(wàn)變的智能化時(shí)代, 單一計(jì)算架構(gòu)已難以應(yīng)對(duì)處理海量數(shù)據(jù)的重任, 業(yè)界亟需“異構(gòu)計(jì)算”來(lái)解決當(dāng)今所面臨的挑戰(zhàn), 賽靈思 Versal ACAP, 作為高度集成的多核異構(gòu)計(jì)算平臺(tái), 支持所有類(lèi)型

2021-01-15 13:53:52 2150

2150 本文介紹如何一步一步將設(shè)計(jì)從SDSoC/Vivado HLS遷移到Vitis平臺(tái)。

2022-07-25 17:45:48 3059

3059

賽靈思公司(Xilinx)推出Vitis——這是一款統(tǒng)一軟件平臺(tái),可以讓包括軟件工程師和AI科學(xué)家在內(nèi)的廣大開(kāi)發(fā)者都能受益于硬件靈活應(yīng)變的優(yōu)勢(shì)。歷經(jīng)5年、投入總計(jì)1000人打造而成,Vitis統(tǒng)一軟件平臺(tái)無(wú)需用戶(hù)深入掌握硬件專(zhuān)業(yè)知識(shí),即可根據(jù)軟件或算法代碼自動(dòng)適配和使用賽靈思硬件架構(gòu)。

2022-07-25 18:07:14 13523

13523

在學(xué)習(xí)ZYNQ嵌入式開(kāi)發(fā)的過(guò)程中,正點(diǎn)原子的教程是采用SDK,而我下載的vivado2020.1已經(jīng)變成了vitis,所以寫(xiě)一這篇博客,方便后續(xù)查閱。

2022-07-25 18:03:30 3090

3090

第一個(gè)Xilinx Vitis IDE入門(mén)helloworld程序

2022-07-25 17:37:23 994

994

本博文介紹Vitis AI1.1 系列軟件安裝教程。

2022-07-25 17:25:27 1529

1529

賽靈思公司(Xilinx)推出Vitis——這是一款統(tǒng)一軟件平臺(tái),可以讓包括軟件工程師和AI科學(xué)家在內(nèi)的廣大開(kāi)發(fā)者都能受益于硬件靈活應(yīng)變的優(yōu)勢(shì)。歷經(jīng)5年、投入總計(jì)1000人打造而成,Vitis統(tǒng)一軟件平臺(tái)無(wú)需用戶(hù)深入掌握硬件專(zhuān)業(yè)知識(shí),即可根據(jù)軟件或算法代碼自動(dòng)適配和使用賽靈思硬件架構(gòu)。

2021-01-31 07:49:37 16

16 本文介紹如何一步一步將設(shè)計(jì)從SDSoC/Vivado HLS遷移到Vitis平臺(tái)。

2021-01-31 08:12:02 8

8 在學(xué)習(xí)ZYNQ嵌入式開(kāi)發(fā)的過(guò)程中,正點(diǎn)原子的教程是采用SDK,而我下載的vivado2020.1已經(jīng)變成了vitis,所以寫(xiě)一這篇博客,方便后續(xù)查閱。

2021-02-21 06:48:51 17

17 本博文介紹Vitis AI1.1 系列軟件安裝教程。

2021-03-01 10:36:55 5

5 ,并將底層 FPGA 和 ACAP 的繁復(fù)細(xì)節(jié)抽象化。幫助缺乏專(zhuān)業(yè)知識(shí)的用戶(hù)輕松開(kāi)發(fā)深度學(xué)習(xí)推斷應(yīng)用,再度刷新AI推斷的高效性和易用性。 想了解Vitis AI為AI推斷帶來(lái)了哪些改變? Vitis AI的強(qiáng)大功能特性 在以高效和易用為核心的設(shè)計(jì)理念支持下,Vitis AI擁有了經(jīng)過(guò)最

2021-05-17 10:38:07 1911

1911

在Vitis 統(tǒng)一軟件平臺(tái)中使用Alveo系列開(kāi)發(fā)板設(shè)計(jì)加速Kernel時(shí),系統(tǒng)會(huì)自動(dòng)為Kernel的時(shí)鐘設(shè)置默認(rèn)頻率。 以 xilinx_u200_qdma_201910_1 平臺(tái)

2021-06-12 14:19:00 36857

36857 Vitis AI 1.4 賽靈思 Vitis AI 是一款功能強(qiáng)大的機(jī)器學(xué)習(xí)開(kāi)發(fā)平臺(tái),用于在賽靈思自適應(yīng)計(jì)算平臺(tái)上實(shí)現(xiàn) AI 推斷加速。最新發(fā)布的 Vitis AI 1.4 版本為用戶(hù)提供了完整

2021-08-09 10:54:33 1435

1435 Versal 自適應(yīng)計(jì)算加速平臺(tái) (ACAP) 將標(biāo)量引擎 (Scalar Engine)、自適應(yīng)引擎 (Adaptable Engine) 和智能引擎(Intelligent Engine

2021-09-09 11:03:22 4191

4191 Vitis Vision庫(kù)是OpenCV和Vision功能的加速庫(kù),可在Vitis環(huán)境中使用,這些庫(kù)的L1目錄是示例設(shè)計(jì)。為了適應(yīng)各種用戶(hù)環(huán)境,從2020.1版本開(kāi)始,Xilinx不再

2022-02-16 16:21:38 2019

2019

Vitis AI 2.0 全面發(fā)布!作為賽靈思 FPGA 和自適應(yīng) SoC 上最綜合全面的基于軟件的 AI 加速解決方案,Vitis AI 繼續(xù)為用戶(hù)的 AI 產(chǎn)品貢獻(xiàn)價(jià)值與競(jìng)爭(zhēng)力。2.0 版本

2022-03-15 17:39:04 1911

1911 Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數(shù)硬連線(xiàn)到器件邏輯互連結(jié)構(gòu)和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應(yīng)用加速開(kāi)發(fā)流程中實(shí)現(xiàn)硬件

2022-05-25 09:43:36 1930

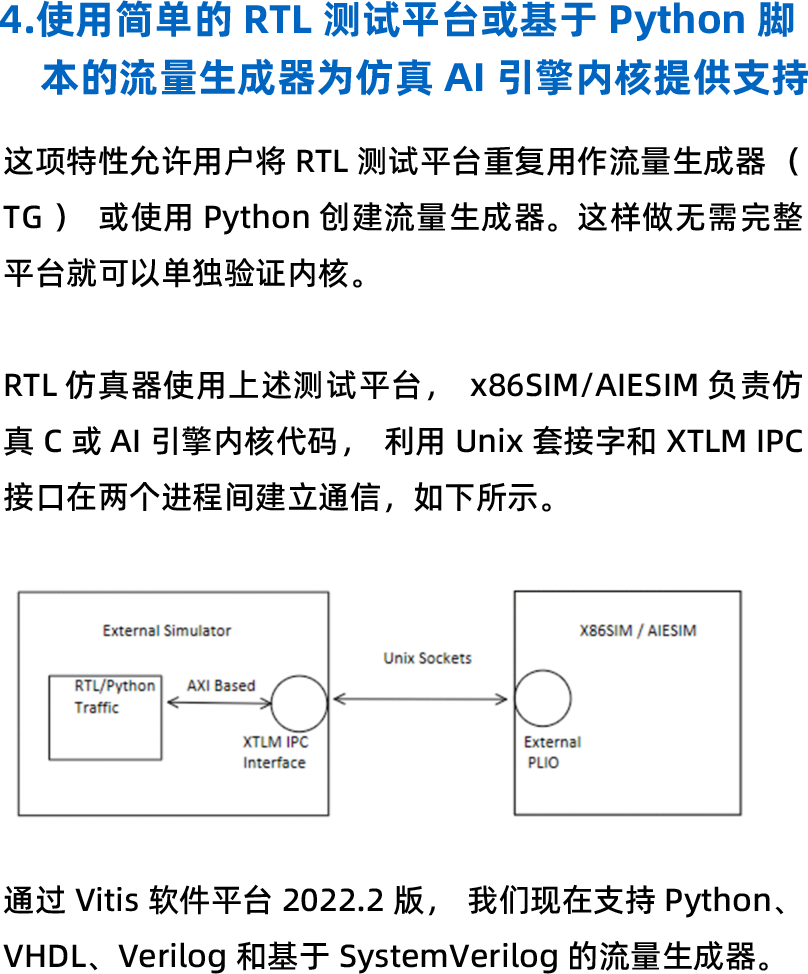

1930 Vitis 環(huán)境開(kāi)發(fā)方法論反應(yīng)了 Versal ACAP 系統(tǒng)的異構(gòu)性質(zhì),此類(lèi)系統(tǒng)通常是由 PS、PL 和 AI 引擎功能組成的。您可使用 Vitis 工具來(lái)獨(dú)立開(kāi)發(fā)并驗(yàn)證這些組件,并逐漸將其加以集成以構(gòu)成最終系統(tǒng)。

2022-06-16 10:23:38 972

972 HLS導(dǎo)出的.xo文件如何導(dǎo)入到Vitis里面?需要把.xo文件解壓,然后把文件夾導(dǎo)入到Vitis Kernel/src文件夾下嗎?

2022-08-03 11:20:26 2663

2663

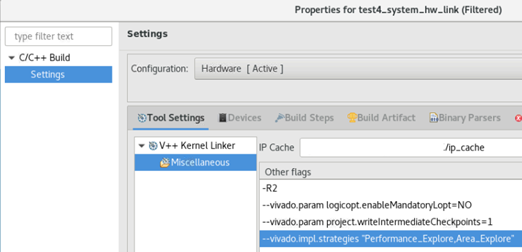

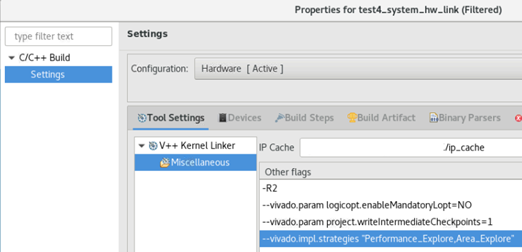

本篇博文將繼續(xù)介紹在Vitis中把Settings信息傳遞到底層的Vivado。

2022-08-02 10:26:41 712

712

Vitis HLS 工具能夠?qū)?C++ 和 OpenCL 功能部署到器件的邏輯結(jié)構(gòu)和 RAM/DSP 塊上。在 GitHub 上提供 Vitis HLS 前端為研究人員、開(kāi)發(fā)人員和編譯器愛(ài)好者開(kāi)啟了無(wú)限可能的新世界,使他們可以利用 Vitis HLS 技術(shù)并根據(jù)其應(yīng)用的特定需求進(jìn)行修改。

2022-08-03 09:53:58 714

714 IntelliJ IDEA 2022.2 為遠(yuǎn)程開(kāi)發(fā)功能帶來(lái)了多項(xiàng)質(zhì)量改進(jìn),使其更美觀、更穩(wěn)定。從 v2022.2 開(kāi)始,IntelliJ IDEA 使用 JetBrains Runtime 17

2022-08-04 10:58:09 1066

1066 對(duì)于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開(kāi)源出來(lái)了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點(diǎn)介紹Vitis HLS。

2022-09-02 09:06:23 2858

2858 金秋已至。伴著涼爽的秋風(fēng)一起到來(lái)的,還有 OpenVINO 工具套件剛剛推出的最新版本 OpenVINO 2022.2。除了能支持英特爾今年新推出的一系列獨(dú)立顯卡進(jìn)行 AI 模型的推理加速及部署外,2022.2的新版本中還有哪些亮眼的新特性呢?讓我們一起來(lái)看看吧。

2022-10-09 09:13:34 1349

1349 安裝流程很簡(jiǎn)單,需要注意的就是要關(guān)閉或退出殺毒軟件或xx管家,電腦用戶(hù)名和安裝路徑不要有中文和空格。

2022-10-24 09:39:26 3436

3436 智能設(shè)計(jì)運(yùn)行 (IDR) 是基本無(wú)需用戶(hù)干預(yù)的一鍵式時(shí)序收斂流程。在 2022.2 版中,我們首次為 Versal 器件提供 IDR 增強(qiáng)功能。使用 IDR 后,我們看到 Versal ACAP 設(shè)計(jì)的 QoR 平均提高 5%

2022-11-03 11:29:56 1761

1761 電子發(fā)燒友網(wǎng)站提供《Zynq上使用Vitis的雙ARM Hello World.zip》資料免費(fèi)下載

2022-12-14 10:15:40 0

0 AMD Vitis HLS 工具允許用戶(hù)通過(guò)將 C/C++ 函數(shù)綜合成 RTL,輕松創(chuàng)建復(fù)雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線(xiàn))及 Vitis 統(tǒng)一軟件平臺(tái)(用于所有異構(gòu)系統(tǒng)設(shè)計(jì)和應(yīng)用)高度集成。

2023-04-23 10:41:01 652

652

在本快速入門(mén)演示中,將探討如何在 Vitis 中使用 Git 集成以及如何使用團(tuán)隊(duì)操作來(lái)共享 Vitis 工程。

2023-05-12 15:01:00 567

567

本文展示了在AMD Zynq設(shè)計(jì)中,如何用 Vitis Vision Library中的函數(shù)導(dǎo)出一個(gè) IP

2023-07-13 17:05:40 315

315

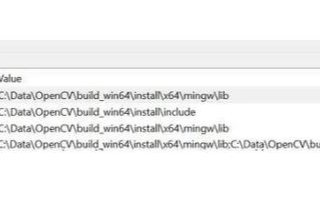

本文演示了在Vitis? 中對(duì) Linux 應(yīng)用程序開(kāi)發(fā)的過(guò)程中如何使用外部庫(kù)

2023-07-07 14:14:51 736

736

本文涵蓋了有關(guān)使用 PetaLinux 命令行來(lái)對(duì) Versal? ACAP 的 PetaLinux BSP 運(yùn)行 QEMU 的信息

2023-07-07 14:14:59 353

353 Vitis? HLS 2023.1 支持新的 L1 庫(kù)向?qū)В疚膶⒅v解如何下載 L1 庫(kù)、查看所有可用功能以及如何在 Vitis HLS GUI 中使用庫(kù)函數(shù)。

2023-08-16 10:26:16 546

546

Vitis AI 遞歸神經(jīng)網(wǎng)絡(luò) (RNN) 工具是 Vitis? AI 開(kāi)發(fā)環(huán)境的一個(gè)子模塊,專(zhuān)注于在 Xilinx? 硬件平臺(tái)(包括 Alveo? 加速器卡)上實(shí)現(xiàn) RNN。這些工具由優(yōu)化的 IP

2023-09-13 17:32:53 0

0 電子發(fā)燒友網(wǎng)站提供《Vitis AI優(yōu)化器指南.pdf》資料免費(fèi)下載

2023-09-14 11:04:38 0

0 電子發(fā)燒友網(wǎng)站提供《Vitis Model Composer用戶(hù)指南.pdf》資料免費(fèi)下載

2023-09-14 09:59:15 0

0 電子發(fā)燒友網(wǎng)站提供《Vitis Model Composer教程.pdf》資料免費(fèi)下載

2023-09-14 09:52:29 0

0 檔旨在逐步指導(dǎo)您熟悉各種 Vitis 工具,這些工具采用自下而上的設(shè)計(jì)流程來(lái)開(kāi)發(fā)系統(tǒng)組件,隨后將其集成到頂層系統(tǒng)工程中。 如果您希望獲取完整版用戶(hù)指

2023-09-13 08:15:02 336

336

電子發(fā)燒友網(wǎng)站提供《Vitis AI用戶(hù)指南.pdf》資料免費(fèi)下載

2023-09-13 15:00:21 0

0 電子發(fā)燒友網(wǎng)站提供《Versal ACAP設(shè)計(jì)指南.pdf》資料免費(fèi)下載

2023-09-13 14:40:49 0

0 電子發(fā)燒友網(wǎng)站提供《Vitis HLS移植指南.pdf》資料免費(fèi)下載

2023-09-13 09:21:12 0

0 電子發(fā)燒友網(wǎng)站提供《Vitis AI庫(kù)用戶(hù)指南.pdf》資料免費(fèi)下載

2023-09-15 10:46:57 0

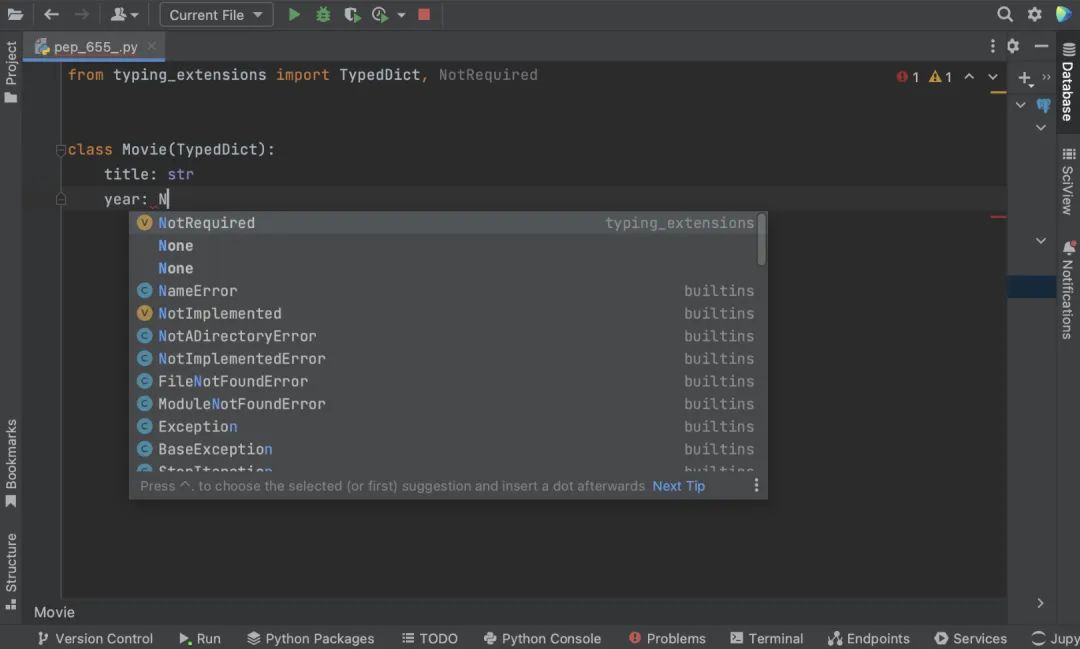

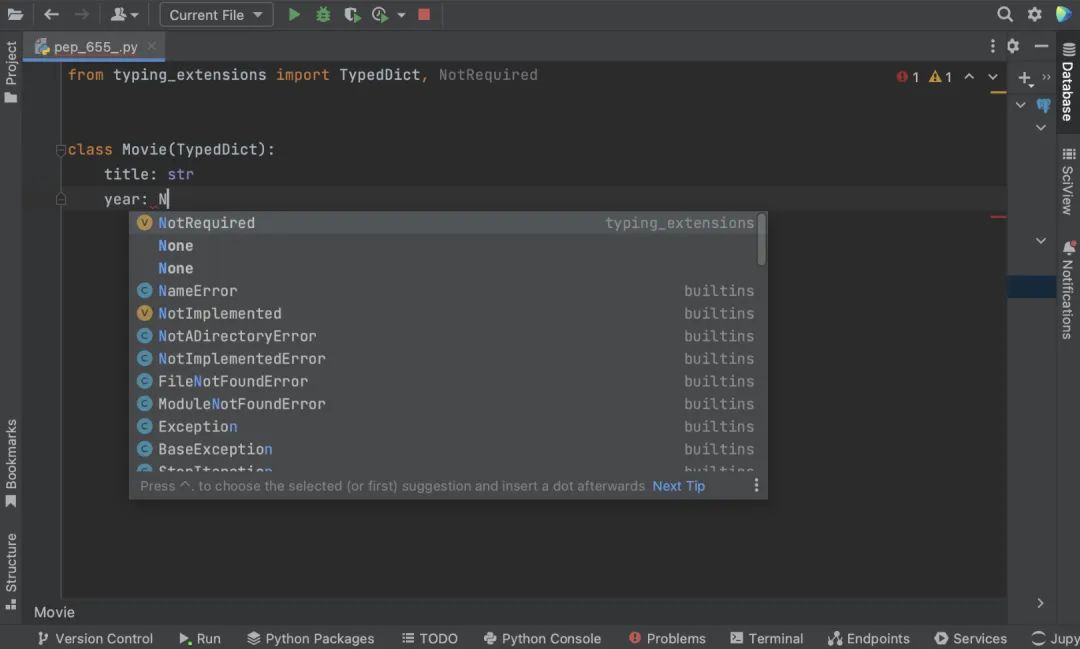

0 通常而言,使用新潮的或者快速發(fā)展的技術(shù),可能會(huì)挺有挑戰(zhàn)性,你可能得經(jīng)常閱讀文檔,才能熟悉新的語(yǔ)法、API 和協(xié)議。 PyCharm 2022.2 通過(guò)提供對(duì) Python 3.11 的語(yǔ)言特性

2023-10-21 10:35:12 243

243

AMD Vitis 軟件平臺(tái)是一款開(kāi)發(fā)環(huán)境,主要用于開(kāi)發(fā)包括 FPGA 架構(gòu)、Arm 處理器子系統(tǒng)和 AI 引擎在內(nèi)的設(shè)計(jì)。Vitis 工具與 AMD Vivado ML 設(shè)計(jì)套件相結(jié)合,可為

2023-12-20 10:00:02 154

154

電子發(fā)燒友網(wǎng)站提供《Vitis AI用戶(hù)指南.pdf》資料免費(fèi)下載

2024-01-03 10:51:52 0

0 Vitis Vision 庫(kù)是一組 90 多個(gè)內(nèi)核,基于 OpenCV 計(jì)算機(jī)視覺(jué)庫(kù),針對(duì) AMD FPGA、AMD AI Engine? 和 AMD SoC 進(jìn)行了優(yōu)化。

2024-01-03 10:10:56 259

259

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論