? ? ? 上一次寫到關于信號完整性的概述。今天講一下時間和頻率。

? ? ? ?先吹上一波牛逼,愛因斯坦相對論中提出時間和空間這兩個概念應該是相對的,而不是絕對的。那么這個應該怎么理解,我的理解是在光速這個不變量的情況下,時間和空間是相互可以置換。哈哈哈,吹不下去了。還是切入正題吧

? ? ? ?在我們的映像中,一直都是以時間作為一個標度,那么我們要知道時間和時刻其實是有分別的,這個分別就參考高中物理書吧。所有的物理都是在一個時刻和一個確定的位置的一個定義。比如我們要知道某一處的某一時刻的電磁場是什么樣的,這就是我們現實生活中所接觸的 ,也就是說這個是實實在在存在的。不管你今天是干了啥,反正時間就是會走,這是一個沒有后退的變量,只能遞增,而不能減小。那么頻域是什么,頻域只是為了方便而引入的一個數學概念,這就是一種數學方法。

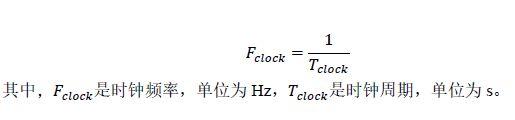

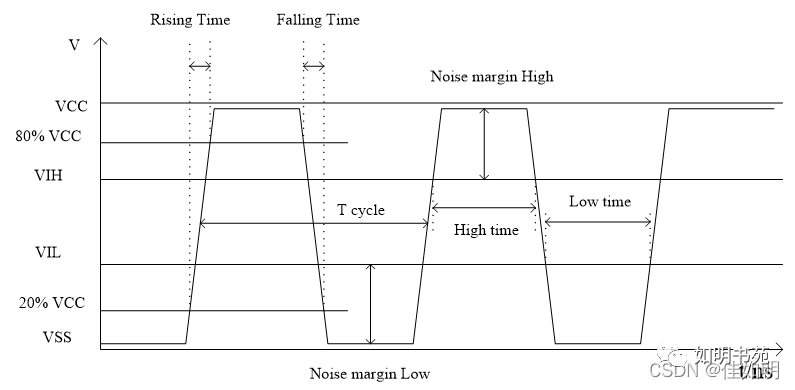

? ? ? 時域就是我們真是的世界,包括我們的測量。頻率和頻域要分清楚。頻率是指一秒內從重復的次數,而頻域確實一個概念,一個維度的坐標系而已。

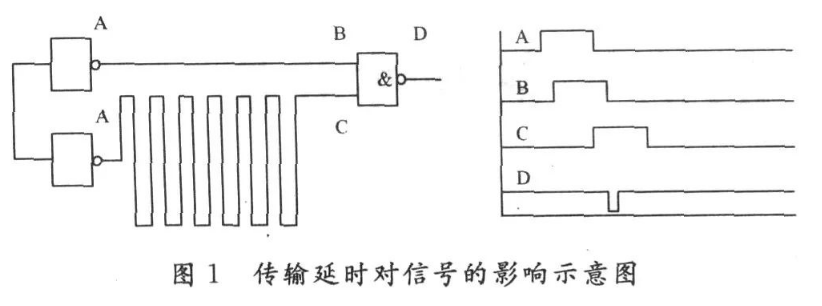

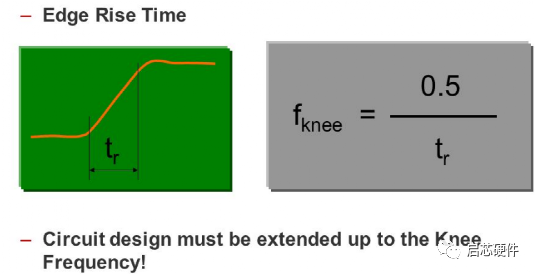

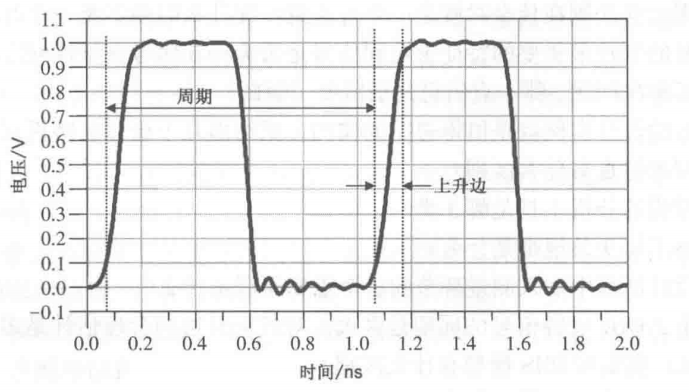

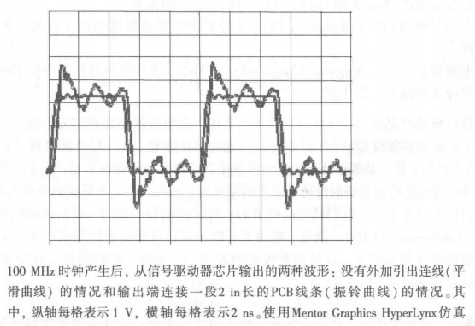

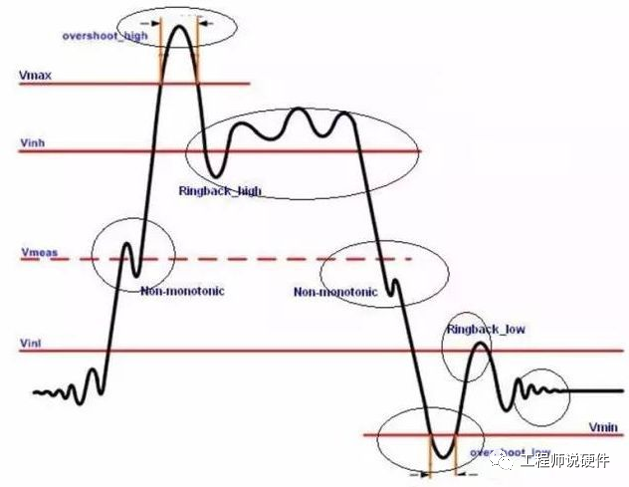

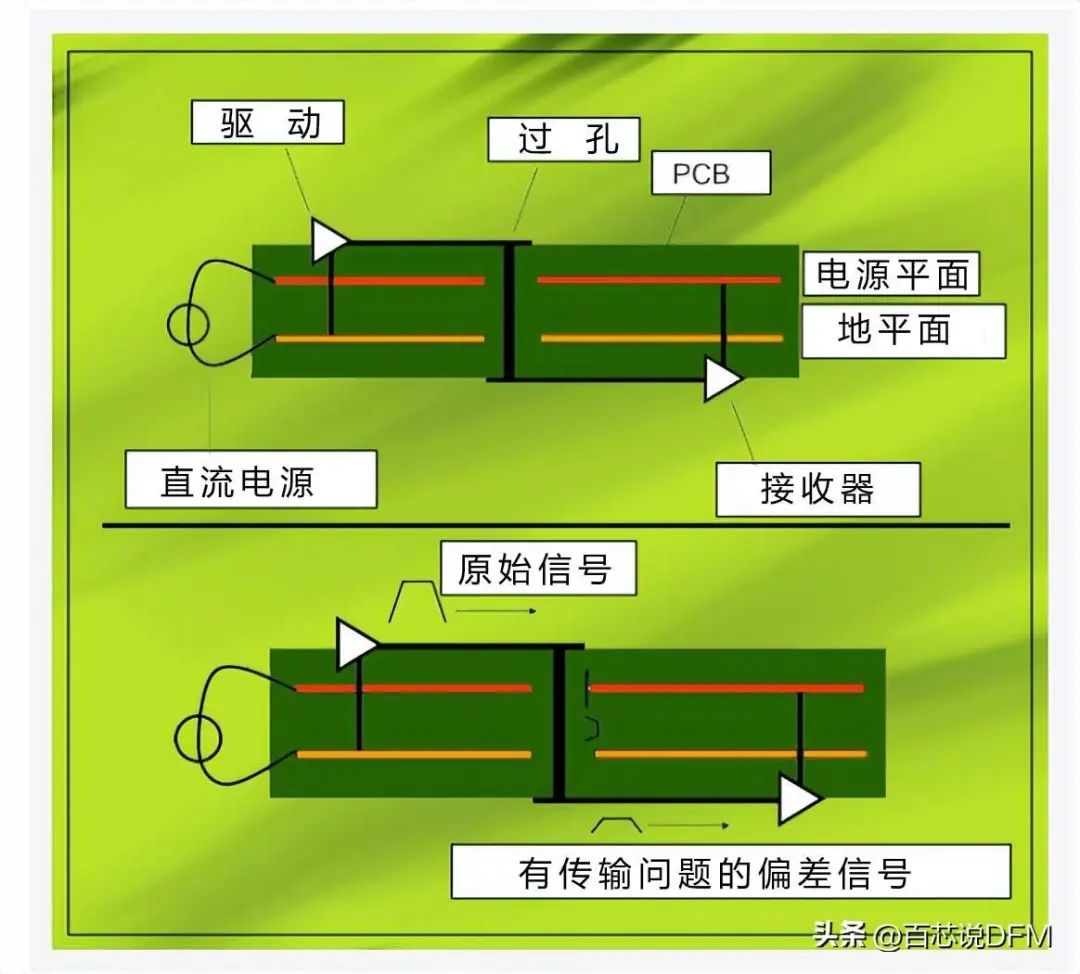

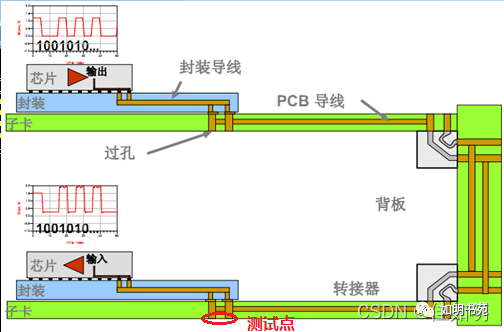

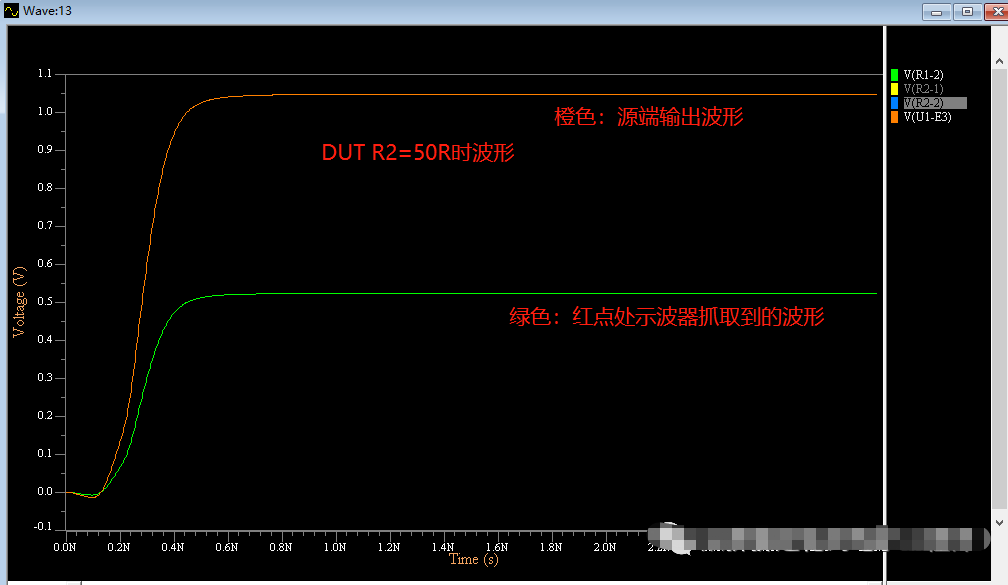

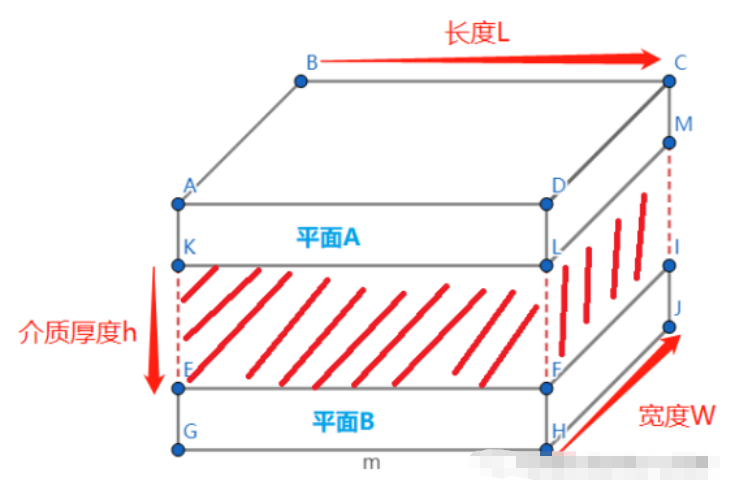

? ? 下面先說時域,F=1/T,這個就是頻率,在信號中,上升沿就是低電平跳到高電平所需時間,而這個時間,就是影響我們信號質量的關鍵。如果經過一段互聯的傳輸,如果上升沿沒有變化,那么這段互聯就是高質量的,從而我們得到的信號就是原始的,這就是高質量。

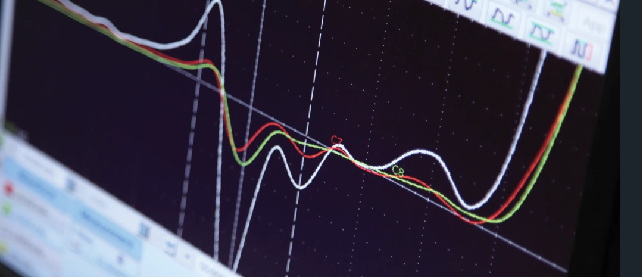

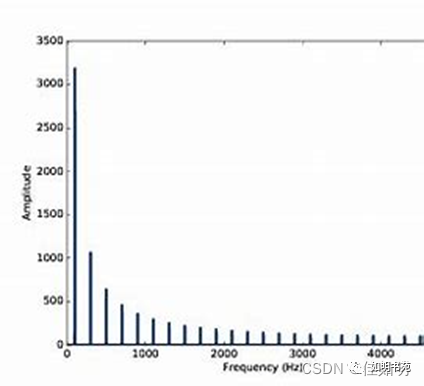

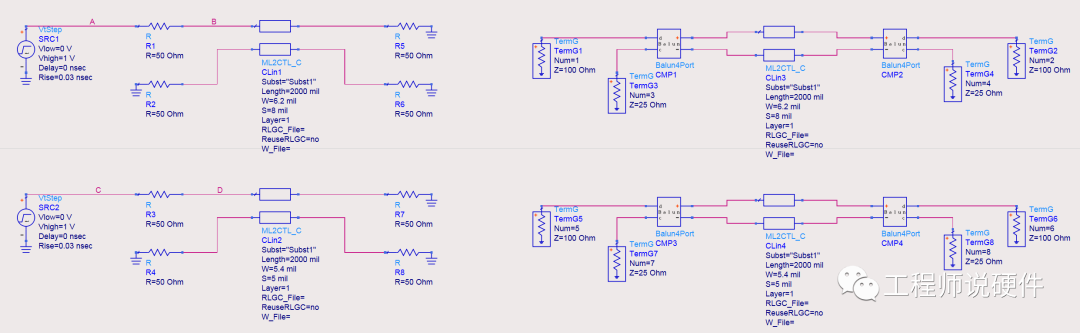

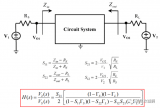

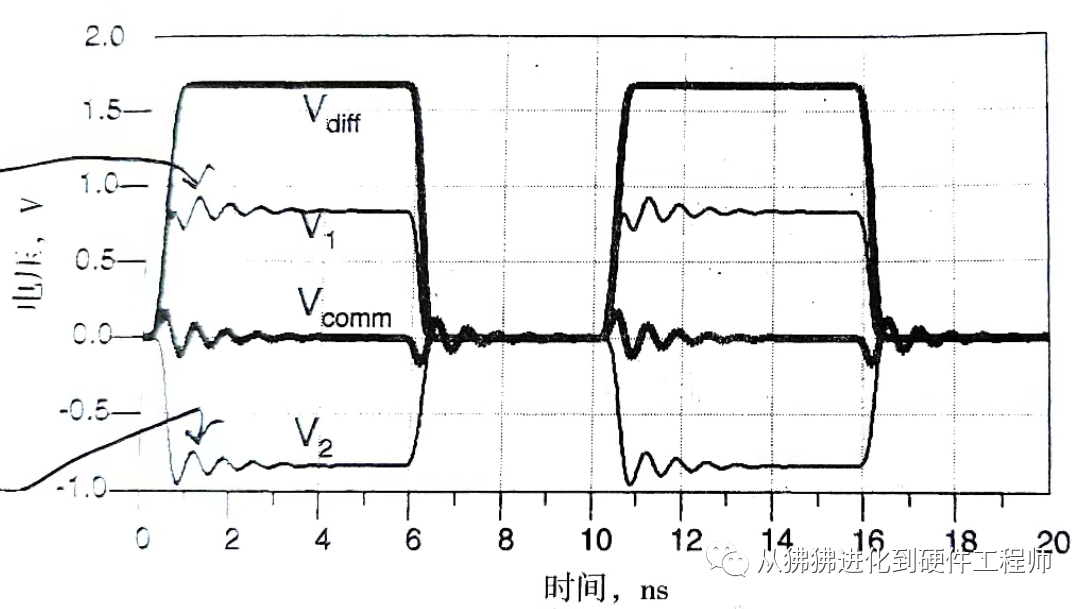

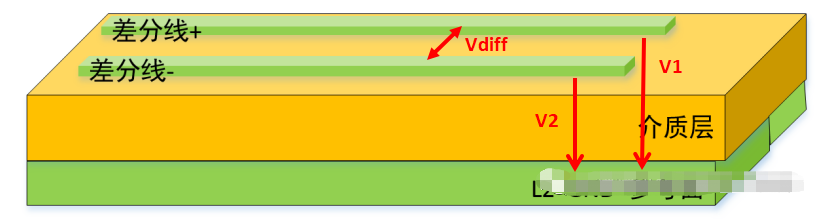

? ? ?頻域,通過一種數學變化(傅里葉變換)將時域中的信號分解成了無數多個正弦波疊加在一起 也能夠湊成了我們想要的信號,理解頻率最重要的是記住:1、頻率是現實世界不存在的,只是一種數學的構造而已;2、在頻域中只存在標準的正弦波。如果使用其他變換,那么當讓也存在其他的數學構造。我們之所以使用正弦波,是因為他有良好的性質如下:

1、所有信號都可以且只有唯一的正弦波描述,

2、所有正弦波都是正交的

3、正弦波沒有上下沿

這些性質都特別有助于我們對信號的分析。任何時域中的波形我們都可以放在頻域中分析

如上圖所示,這就是整個時域中的信號可以完全變化成n個正弦波的疊加,只是幅度不一樣。

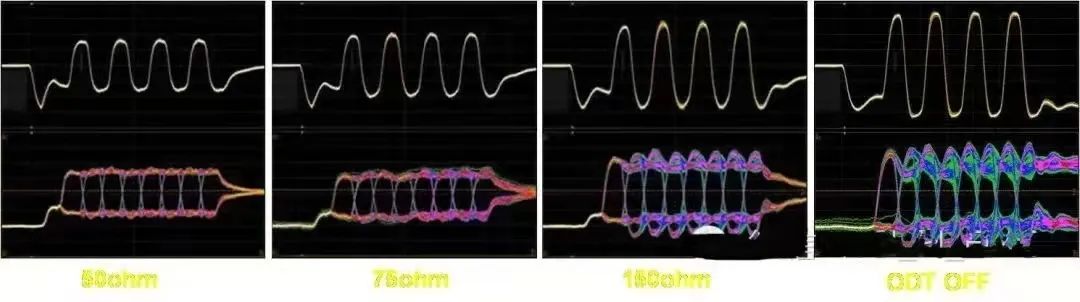

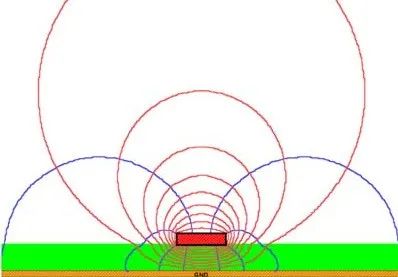

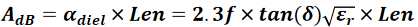

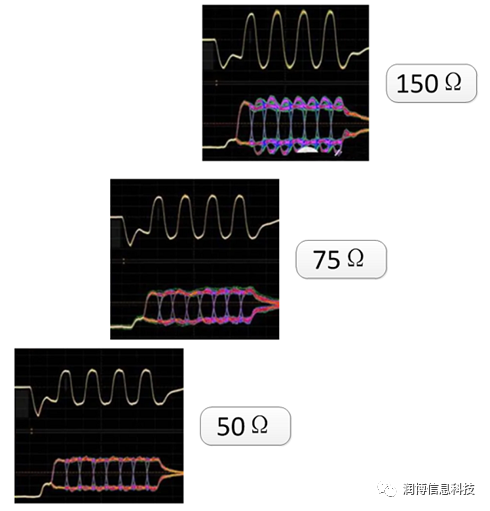

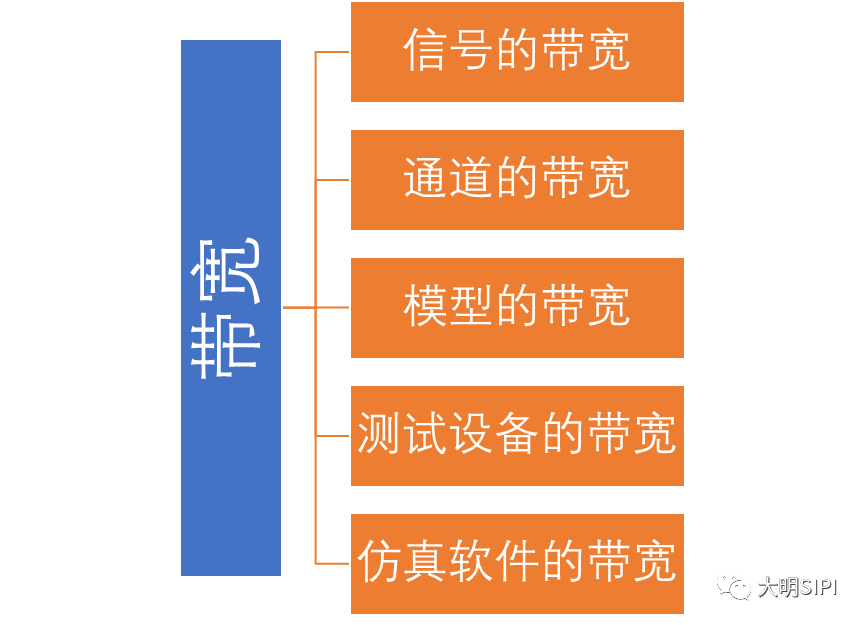

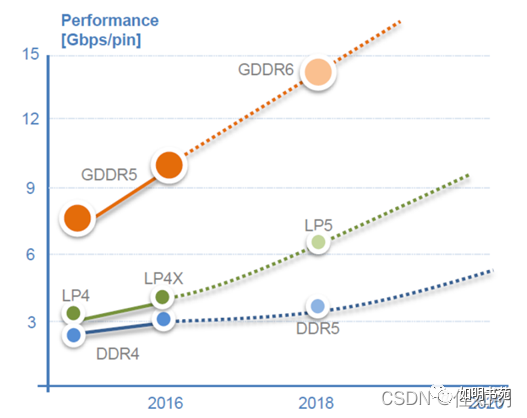

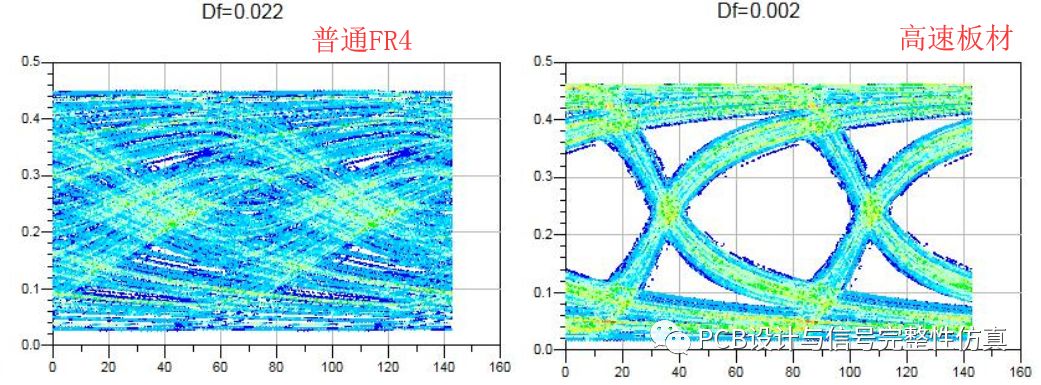

那么這又得出一個問題,信號中常說的帶寬是什么?其實帶寬就是互聯不會屏蔽過濾掉正弦波中有用的疊加。如果能到達理想狀態最好,那就是所有的正弦波都沒有被濾除,那么就不會影響到信息含量最大的地方,那就是信號的上升沿,信號中的判定,時序都是上升沿能夠保證和輸出的一樣,我們所有的信號中,最有信息含量的就是上升沿時間和幅度。當然這在現實中是不可能的。因此我們只能盡最大的努力保證上升沿變化在我們的可接受范圍內。很顯然,帶寬的定義就出來了,也就是保證信號的我們可接受的最高次諧波不被濾除,而能夠順利的通過互聯。

計算帶寬的公式:BW=0.35/RT RT是上升沿時間。0.35怎么來可參考于博士信號處理中的推導。RT占周期的比例越小,所需要滿足的帶寬就越大。

差不多了 ,這也就是我最多的理解了。這個文筆真特碼爛,哎? ,萬里雄關從頭越。長征二萬五,感覺才走第一步。

電子發燒友App

電子發燒友App

評論