電路功能與優(yōu)勢(shì)

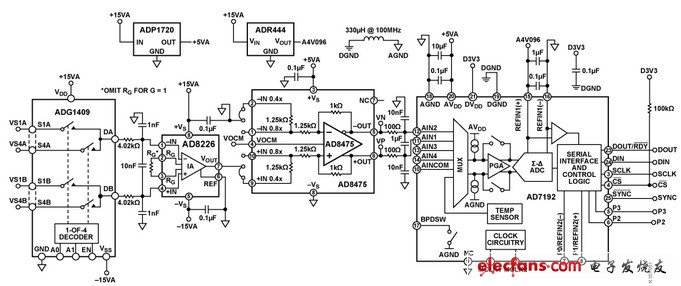

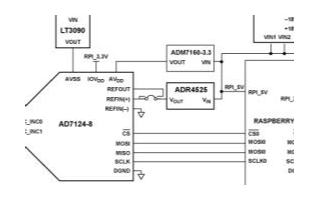

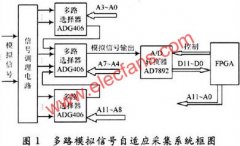

圖1所示電路是一種靈活的信號(hào)調(diào)理電路,用于處理寬動(dòng)態(tài)范圍(從幾mV p-p到20 V p-p)的信號(hào)。該電路利用高分辨率模數(shù)轉(zhuǎn)換器(ADC)的內(nèi)部可編程增益放大器(PGA)來提 供必要的調(diào)理和電平轉(zhuǎn)換并實(shí)現(xiàn)動(dòng)態(tài)范圍。

在過程控制和工業(yè)自動(dòng)化應(yīng)用中,±10 V滿量程信號(hào)非常常見;然而,有些情況下,信號(hào)可能小到只有幾mV。用現(xiàn)代低壓ADC處理±10 V信號(hào)時(shí),必須進(jìn)行衰減和電平轉(zhuǎn)換。但是,對(duì)小信號(hào)而言,需要放大才能利用ADC的動(dòng)態(tài)范圍。因此,在輸入信號(hào)的變化范圍較大時(shí),需要使用帶可編程增益功能的電路。

此外,小信號(hào)可能具有較大的共模電壓擺幅;因此需要較高的共模抑制(CMR)性能。在某些源阻抗較大的應(yīng)用中,模擬前端輸入電路也需要具有高阻抗。

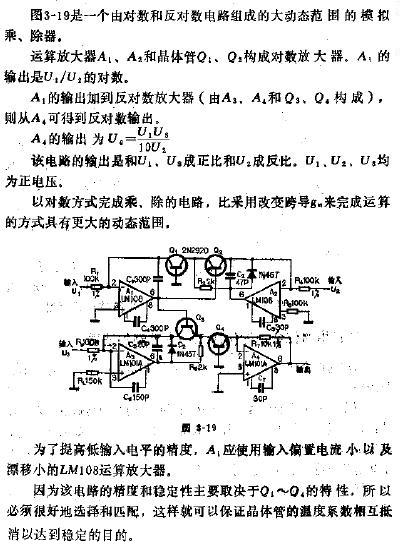

?

圖1. 適合寬工業(yè)范圍信號(hào)調(diào)理的靈活模擬前端電路

圖1所示電路解決了所有這些難題,并提供了可編程增益、高CMR和高輸入阻抗。輸入信號(hào)經(jīng)過4通道ADG1409 多路復(fù)用器進(jìn)入 AD8226低成本、寬輸入范圍儀表放大器。AD8226 提供高達(dá)80dB的高共模抑制(CMR)和非常高的輸入阻抗(差模800M和共模400M)。寬輸入范圍和軌到軌輸出使得AD8226可以充分利用供電軌。

AD8475是一款全差分衰減放大器,集成精密增益電阻,可提供精密衰減(G=0.4或G=0.8)、共模電平轉(zhuǎn)換及單端差分轉(zhuǎn)換功能AD8475是一種易于使用、完全集成的精密增益模塊,采用單電源供電時(shí),最高可處理±10 V的信號(hào)電平。因此,AD8475適用于衰減來自AD8226且最高20Vp-p的信號(hào),同時(shí)維持高CMR性能并提供差分輸出來驅(qū)動(dòng)差分輸入ADC。

AD7192是一款內(nèi)置PGA的24位ADC。片內(nèi)低噪聲增益級(jí)(G=1、8、16、32、64或128)意味著可直接向該ADC輸入小信號(hào)。

結(jié)合上述器件,對(duì)幅度會(huì)變化的信號(hào)而言,該電路可以提供非常好的性能且易于配置。該電路適合工業(yè)自動(dòng)化、過程控制、儀器儀表和醫(yī)療設(shè)備應(yīng)用。

電路描述

該電路包含一個(gè)ADG1409多路復(fù)用器、一個(gè)AD8226儀表放大器、一個(gè)AD8475差動(dòng)放大器、一個(gè)AD7192Σ-Δ型ADC(帶 ADR444基準(zhǔn)電壓源)以及 ADP1720穩(wěn)壓器。只需少量外部元件來提供保護(hù)、濾波和去耦,使得該電路具有高集成度,而且所需的電路板(印刷電路板[PCB])面積較小。

穩(wěn)壓器和基準(zhǔn)電壓源的選擇

該電路選擇ADP1720-5作為5 V穩(wěn)壓器。它是一款高壓、微功耗、低壓差線性穩(wěn)壓器,適合工業(yè)應(yīng)用。

該電路選擇4.096V ADR444作為基準(zhǔn)電壓源。它是一款超低噪聲、高精度、低壓差器件,特別適合高分辨率、∑-△型ADC和精密數(shù)據(jù)采集系統(tǒng)。

輸入開關(guān)和保護(hù)

ADG1409 多路復(fù)用器擁有2位二進(jìn)制地址線,可用于選擇四種可能的輸入通道之一。該設(shè)計(jì)還包括外部保護(hù)功能,如標(biāo)準(zhǔn)二極管和瞬態(tài)電壓抑制器,用以增強(qiáng)電路的魯棒性。這些在圖1中并未顯示,但是在CN0251設(shè)計(jì)支持包的詳細(xì)原理圖及其它文檔中有所展示。

ADG1409多路復(fù)用器配置為接收四路差分輸入信號(hào):(VS1A?VS1B)、(VS2A?VS2B)、(VS3A?VS3B)和(VS4A?VS4B)。多路復(fù)用器的輸出(DA和DB)施加于 AD8226儀表放大器的輸入端。

AD8226輸入儀表放大器

外部RG電阻設(shè)置AD8226的增益。對(duì)于該電路,省略了RG,且儀表放大器級(jí)的增益為1。因此,AD8226的輸出為VSxA–VSxB,其中x為輸入通道編號(hào)。

AD8226的差分輸入由兩個(gè)4.02k電阻和一個(gè)10nF電容進(jìn)行濾波,這些電阻和電容構(gòu)成一個(gè)截止頻率為2.0kHz的單極點(diǎn)RC濾波器。兩個(gè)1nF電容增加了截止頻率為40kHz的共模濾波。

AD7192ADC PGA增益配置

AD7192配置為接收差分模擬輸入,以匹配來自AD8475的差分輸出信號(hào)。 AD7192的滿量程輸入范圍為±VREF/增益,其中±VREF=REFINx(+)-REFINx(-)。

AD7192中的緩沖器使能時(shí),輸入通道會(huì)驅(qū)動(dòng)緩沖放大器的高阻抗輸入級(jí),此模式下的絕對(duì)輸入電壓范圍將限制在AGND+250mV至AVDD-250mV。增益級(jí)使能后,緩沖器輸出將施加于PGA的輸入端,模擬輸入范圍必須限制在±(AVDD-1.25V)/增益以內(nèi),因?yàn)镻GA需要額外的裕量。因此,采用4.096V基準(zhǔn)電壓源和5V電源時(shí),為了最充分地利用ADC的動(dòng)態(tài)范圍,可按表1所示對(duì)信號(hào)進(jìn)行衰減或放大。

表1. AD8475和 AD7192內(nèi)置PGA的各種輸入范圍增益配置

差分衰減放大器

為了驅(qū)動(dòng)低壓ADC,±0V或±5V信號(hào)需要進(jìn)行衰減和電平轉(zhuǎn)換。若將差動(dòng)放大器配置與精密電阻配合使用,勢(shì)必會(huì)因電阻之間出現(xiàn)失配而導(dǎo)致CMR性能下降。AD8475電平轉(zhuǎn)換器/衰減器集成精密激光調(diào)整匹配電阻,可確保低增益誤差、低增益漂移(最大33ppm/°C)和高CMR特性。

AD8475提供兩個(gè)引腳可選的增益選項(xiàng),即0.4和0.8。VOCM引腳用于調(diào)整精密電平轉(zhuǎn)換的輸出共模電壓,以便匹配ADC的輸入范圍,并使動(dòng)態(tài)范圍最大化。此引腳可保持懸空,并利用一個(gè)精密分壓器進(jìn)行內(nèi)部偏置,該分壓器由電源與地之間的兩個(gè)200M電阻組成,從而在該引腳上提供中間電源電壓。

由兩個(gè)100電阻和一個(gè)1F電容組成的一個(gè)單極點(diǎn)差分RC濾波器充當(dāng)AD7192的抗混疊和降噪濾波器,其截止頻率為800Hz。兩個(gè)10nF電容提供截止頻率為160kHz的共模濾波。

濾波器、輸出數(shù)據(jù)速率和建立時(shí)間

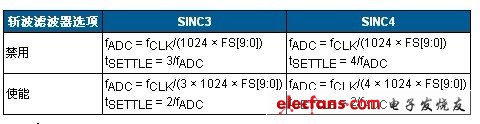

AD7192Σ-Δ型ADC由調(diào)制器和數(shù)字濾波器組成。輸出數(shù)據(jù)速率(fADC)和建立時(shí)間(tSETTLE)與濾波器配置及斬波配置有關(guān)。表2顯示了不同配置情況下的輸出數(shù)據(jù)速率和建立時(shí)間計(jì)算情況。

表2. 不同配置的輸出數(shù)據(jù)速率和建立時(shí)間

布局考慮

該電路或其它任何高速/高分辨率電路的性能都高度依賴于適當(dāng)?shù)腜CB布局,包括但不限于電源旁路、信號(hào)路由以及適當(dāng)?shù)碾娫磳雍徒拥貙印?/p>

系統(tǒng)性能

24位 AD7192 Σ-Δ 型ADC可在該電路中提供非常好的性能。

在配置設(shè)為斬波禁用、輸出數(shù)據(jù)速率為4.7 Hz、增益為1且采用一個(gè)SINC4濾波器的情況下,噪聲性能如圖2所示,500個(gè)樣本的噪聲分布直方圖則如圖3所示。該電路中測(cè)得的峰峰值噪聲約為3.9 μV(見圖2),均方根噪聲為860 nV。這相當(dāng)于峰峰值(無噪聲碼)分辨率為20位,均方根分辨率為23位。表3顯示了斬波禁用且采用一個(gè)SINC4濾波器時(shí)一些數(shù)據(jù)速率和增益設(shè)置條件下的AD7192均方根噪聲。

圖2. 噪聲輸出(VREF = 4.096 V, AVDD = 5 V, Output Data Rate = 4.7 Hz, a Rate = 4.7 Hz,

圖3. 噪聲直方圖(VREF = 4.096 V,AVDD =5 V,輸出數(shù)據(jù)速率 = 4.7Hz,增益 = 1,斬波禁用,SINC4濾波器)

表3. 斬波禁用且采用一個(gè)SINC4濾波器時(shí)不同輸出數(shù)據(jù)速率和增益設(shè)置條件下的AD7192系統(tǒng)均方根分辨率(減去2.7位以獲取峰峰值或無噪聲碼分辨率)

常見變化

可使用其它集成PGA的24位或較低分辨率的Σ-Δ型ADC, 例如 AD7190、 AD7193、 AD7797和AD7799。如果無需對(duì)輸入信號(hào)進(jìn)行衰減, 則可使用功耗低于 AD8475 的 AD8476。

在無需衰減和高輸入阻抗的應(yīng)用中,可將 AD7192 直接連接到傳感器,以避免模擬前端調(diào)理電路引入的噪聲。例如,滿量程輸出電壓較小的稱重傳感器無需衰減,因此可以直接連接到 AD7192 差分輸入端

電路評(píng)估與測(cè)試

該電路測(cè)試設(shè)置使用 EVAL-CN0251-SDPZ電路評(píng)估板和系統(tǒng)演示平臺(tái)(SDP)評(píng)估板( EVAL-SDP-CB1Z)。這兩片板具有120引腳的對(duì)接連接器,可以快速完成設(shè)置并評(píng)估電路性能 EVAL-CN0251-SzzDPZ 板包含要評(píng)估的電路,如本電路筆記所述;SDP評(píng)估板與 CN-0251 評(píng)估軟件一起使用,可從 EVAL-CN0251-SDPZ中獲取數(shù)據(jù)。SDP也用于控制 AD7792 ADC中的多路復(fù)用器輸入和各種功能。

設(shè)備要求

需要以下設(shè)備:

帶USB端口的Windows XP、Windows Vista(32位)或 Windows 7(32位)PC

EVAL-CN0251-SDPZ 電路評(píng)估板

EVAL- SDP-CB1Z SDP 評(píng)估板

直流電源:+15 V、-15 V和+6 V。

CN-0251 評(píng)估軟件

入門指南

將 CN-0251 評(píng)估軟件光盤放進(jìn)PC的光盤驅(qū)動(dòng)器,加載評(píng)估 軟件。找到包含評(píng)估軟件光盤的驅(qū)動(dòng)器,打開Readme文 件。按照Readme文件中的說明安裝和使用評(píng)估軟件。

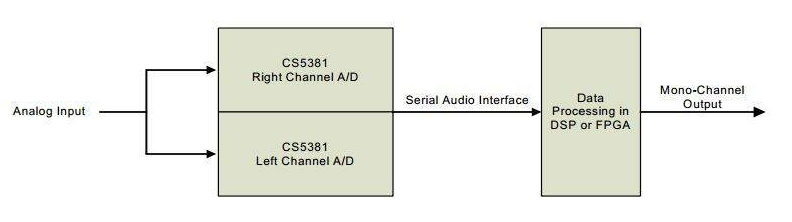

功能框圖

圖4為測(cè)試設(shè)置功能框圖。EVAL-CN0251-SDPZ-SCH.pdf文件包含 EVAL-CN0251-SDPZ 的詳細(xì)原理圖。

圖4. 測(cè)試設(shè)置功能框圖

設(shè)置

將 EVAL-CN0251-SDPZ 上的120引腳連接器連接到 EVAL-SDP-CB1Z (SDP)(SDP)上的CONA連接器。使用尼龍五金配件通過120引腳連接器兩端的孔牢牢固定這兩片板。將直流輸出電源成功設(shè)置為+15 V、-15 V和+6 V輸出后,關(guān)閉電源。

在斷電情況下,將+15 V電源連接到J3的+15VA引腳,將-15V電源連接到J3的-15VA引腳,將GND連接到J3的AGND引腳。此外,在斷電情況下,將6 V電源連接到J2。接通電源,然后將SDP板附帶的USB電纜連接到PC上的USB端口。接通EVAL-CN0251-SDPZ的直流電源之前,請(qǐng)勿將該USB電纜連接到SDP板上的微型USB連接器。

測(cè)試

設(shè)置好電源并將它連接到 EVAL-CN0251-SDPZ后,啟動(dòng)評(píng)估軟件,并通過USB電纜將PC連接到SDP板上的微型USB連接器。如果設(shè)備管理器中列出了Analog Devices SystemDevelopment Platform驅(qū)動(dòng)器,軟件將能與SDP板通信。

一旦USB通信建立,就可以使用SDP來發(fā)送、接收和捕捉來自 EVAL-CN0251-SDPZ的串行數(shù)據(jù)。然后,連接信號(hào)源以便進(jìn)行測(cè)量。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論