了解如何使用Vivado Device Programmer來創(chuàng)建和配置內存可配置器件。首先,我們將學習如何設置一個正確的比特流特性,及生成一個內存配置文件。然后我們將用該配置文件來對內存可配置器件進行編程。最后我們還會用這個可配置內存來引導FPGA。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618659 -

賽靈思

+關注

關注

33文章

1797瀏覽量

132366 -

內存

+關注

關注

8文章

3125瀏覽量

75280

發(fā)布評論請先 登錄

相關推薦

熱點推薦

Vivado無法選中開發(fā)板的常見原因及解決方法

在使用 AMD Vivado Design Suite 對開發(fā)板(Evaluation Board)進行 FPGA 開發(fā)時,我們通常希望在創(chuàng)建工程時直接選擇開發(fā)板,這樣 Vivado 能夠自動

使用 BSP 助手創(chuàng)建項目并創(chuàng)建 BSP 后,我應該在哪里更改 cy_device_headers.h 中列出的設備名稱宏?

使用 BSP 助手創(chuàng)建項目并創(chuàng)建 BSP 后,我應該在哪里更改 cy_device_headers.h 中列出的設備名稱宏?例如,我想手動將設備

發(fā)表于 06-26 06:06

如何使用AMD Vitis HLS創(chuàng)建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 來創(chuàng)建一個 HLS IP,通過 AXI4 接口從存儲器讀取數據、執(zhí)行簡單的數學運算,然后將數據寫回存儲器。接著會在 AMD Vivado

一文詳解Vivado時序約束

Vivado的時序約束是保存在xdc文件中,添加或創(chuàng)建設計的工程源文件后,需要創(chuàng)建xdc文件設置時序約束。時序約束文件可以直接創(chuàng)建或添加已存在的約束文件,

飛凌嵌入式ElfBoard ELF 1板卡-字符驅動之自動創(chuàng)建節(jié)點

;Failed to create class\\n\");return PTR_ERR(my_class);}// 創(chuàng)建設備節(jié)點并關聯到設備類 my_device = device

發(fā)表于 03-18 09:48

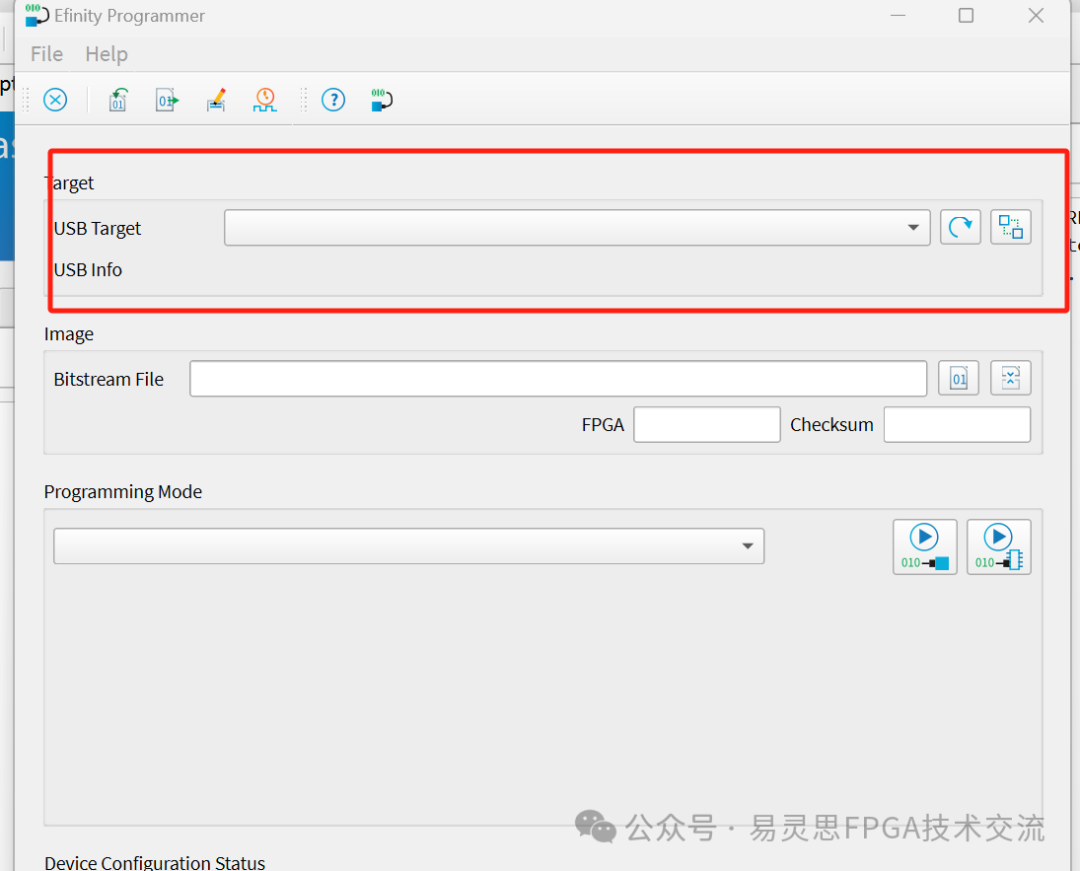

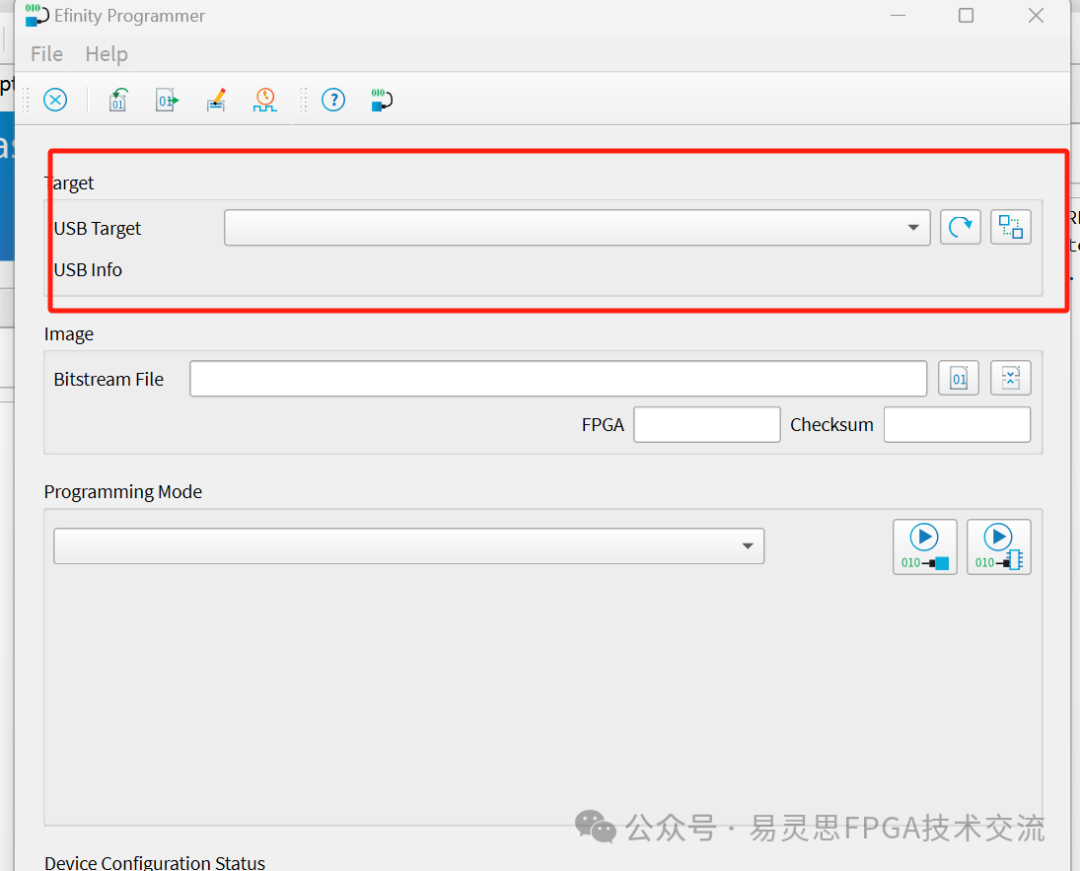

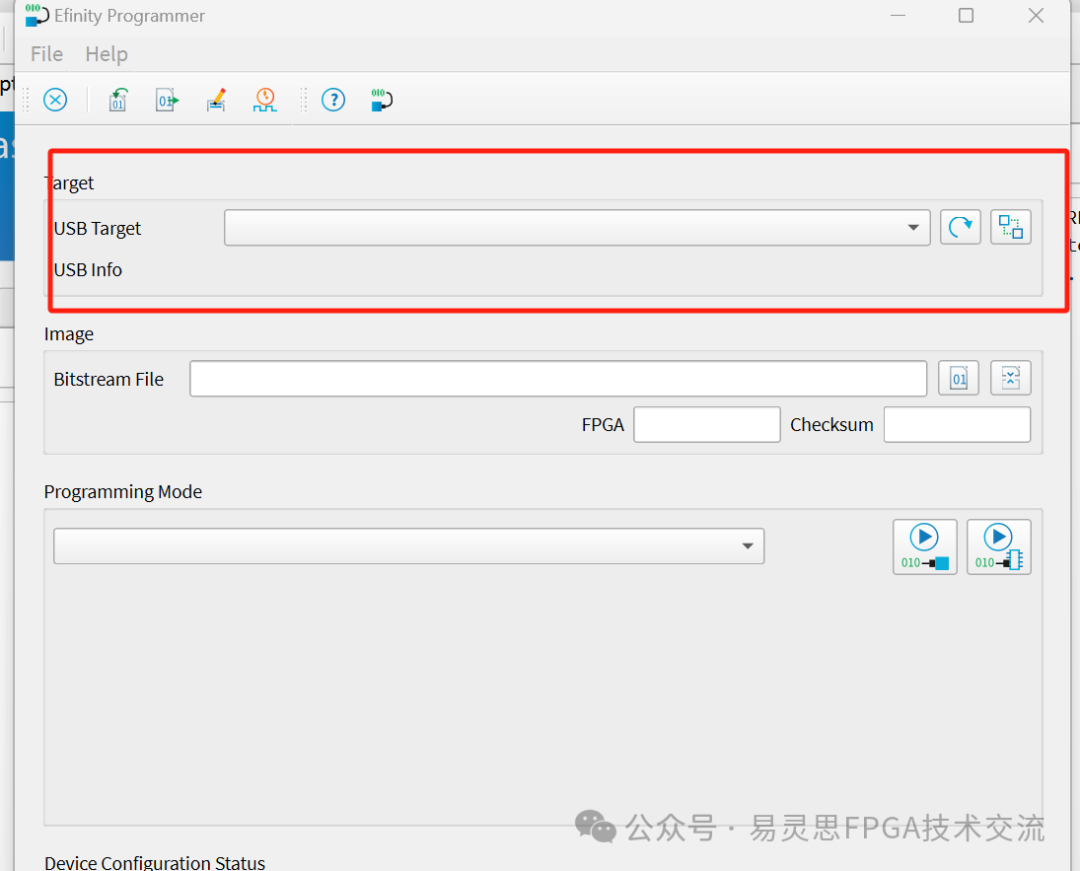

programmer下載常見問題總結-v10

? (0)連接下載器之后什么也讀不出來 說明 :一般為驅動沒有安裝,在device manger里面查看是否有l(wèi)ibusbK (1)打開Programmer異常 ? 原因:(1)更換USB接口

programmer下載常見問題總結-v9

? (0)連接下載器之后什么也讀不出來 說明 :一般為驅動沒有安裝,在device manger里面查看是否有l(wèi)ibusbK (1)打開Programmer異常 ? 原因:(1)更換USB接口

programmer下載常見問題總結-v8

(0)連接下載器之后什么也讀不出來 說明 :一般為驅動沒有安裝,在device manger里面查看是否有l(wèi)ibusbK (1)打開Programmer異常 原因:(1)更換USB接口 。 (2

SOLIDWORKS 2025教育版支持多部件裝配體的創(chuàng)建和管理

SOLIDWORKS作為一款廣泛使用的三維CAD設計軟件,在教育領域同樣占據了重要地位。SOLIDWORKS 2025教育版不僅提供了強大的設計工具和功能,還大大地支持了多部件裝配體的創(chuàng)建和管理,為教育工作者和學生提供了一個有效、直觀的設計平臺。

迅為RK3568開發(fā)板篇OpenHarmony配置HDF驅動控制LED-修改HCS硬件配置

上面的節(jié)點配置

device_topeet_led 設備節(jié)點歸類于 platform 這個 host

device_topeet_led :: de

發(fā)表于 01-08 15:25

Hyper-V創(chuàng)建虛擬機配置IP等網絡配置原理(Linux、Windows為例)

大家知道Windows系統(tǒng)里面內置了Hyper-V管理器,用來創(chuàng)建和管理本地虛擬機環(huán)境。今天我創(chuàng)建了兩臺虛擬機,一臺是CentOS7.9(Linux),另一臺是Windows 11,然后發(fā)現

Vivado中DDRX控制器(mig)ip核配置中關于命令序號選擇和地址映射說明

本篇主要討論Vivado中DDRX控制器(mig)ip核配置中關于命令序號選擇和地址映射說明(一) 利用Xilinx 7系列FPGA開發(fā)時,經常需要驅動外部存儲器--DDRX。Xilinx提供了

VLAN 配置中的常見問題解決

VLAN(虛擬局域網)配置中的常見問題涉及多個方面,包括配置錯誤、網絡互通問題、設備連接故障等。以下是對這些問題的分析和解決方法: 一、配置錯誤 管理VLAN

Vivado使用小技巧

有時我們對時序約束進行了一些調整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調整

programmer下載常見問題總結-v3

(0)連接下載器之后什么也讀不出來 說明 :一般為驅動沒有安裝,在device manger里面查看是否有l(wèi)ibusbK (1)打開Programmer異常 原因:(1)更換USB接口 。 (2

如何使用Vivado Device Programmer創(chuàng)建和配置存儲設備

如何使用Vivado Device Programmer創(chuàng)建和配置存儲設備

評論